## Semiconductor Memory: Opportunities and Challenges

### Bob Gleixner

Technology Development, Micron Technology, Inc. (Acknowledging Fabio Pellizzer and Hongmei Wang for content)

©2017 Micron Technology, Inc. All rights reserved. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Statements regarding products, including regarding their features, availability, functionality, or compatibility, are provided for informational purposes only and do not modify the warranty, if any, applicable to any product. Drawings may not be to scale. Micron, the Micron logo, and all other Micron trademarks are the property of Micron Technology, Inc. All other trademarks are the property of their respective owners.

### **Outline of Talk**

- Memory Trends

- Storage Class Memory

- Path for Emerging Memories

- Conclusions

# **Trends Driving Increased Data Traffic**

#### Enterprise

**Online Transaction** Processing systems with lowlatency in-memory compute

Automotive

Cloud/ **Big Data**

### **Networking**

**Mobile**/ Client

### IoT

Global sales of autonomous vehicles to reach ~600,000 units by 2025

Data center storage installed capacity to grow ~5X to 1.8 ZB between 2015 and 2020

**Global IP traffic** grows at a CAGR of 24% from 2016 to 2020

Global mobile data traffic to rise ~7X between 2016 and 2021

27.1 billion networked devices by 2021

Source, September 2017: Cisco, Gartner, IDC, Automobile manufacturers IoT – Internet of Things

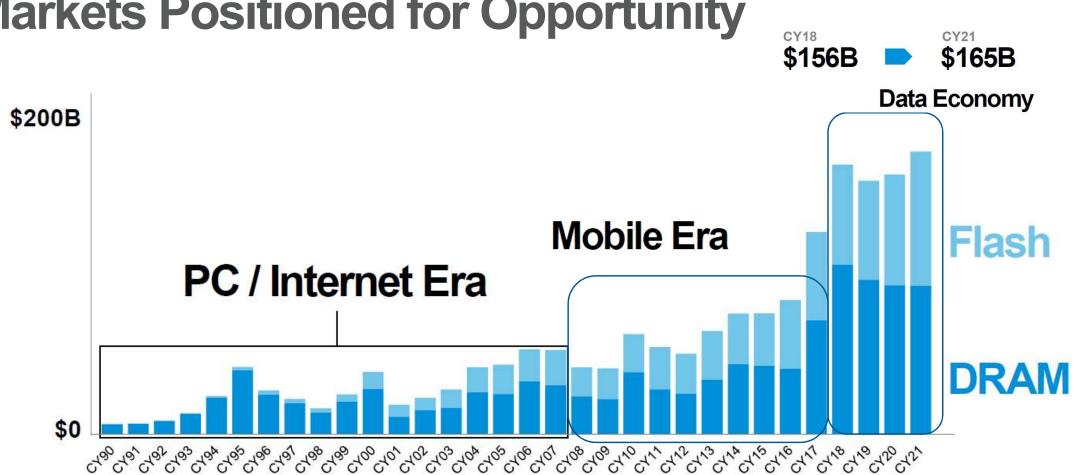

### Markets Positioned for Opportunity

□ Trends such as AI, ADAS and IoT driving demand for tailored DRAM solutions

Source: Micron AI - Artificial Intelligence ADAS - Advanced Driver Assistance Systems Ongoing adoption of SSDs in enterprise, cloud and client driving NAND demand

### **DRAM Memory**

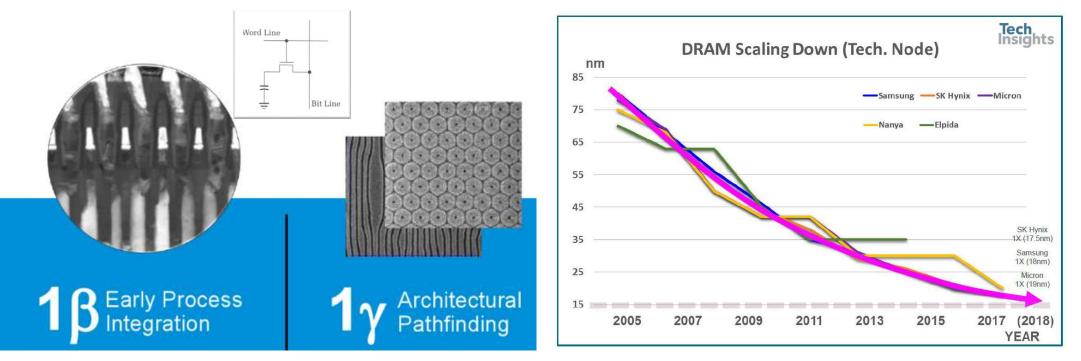

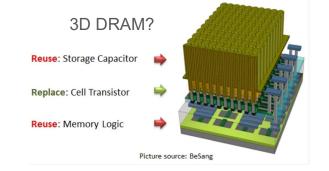

□ DRAM has evolved from a planar to a vertical approach

- Planar capacitor cell; 1978: Stacked capacitor cell structure; 1982: Trench capacitor cell structure; 2003: 3D access transistor; 2008: buried WL

- Current DRAM in production are 15/17nm node (6F2) with cylindrical STC with buried WL access transistor

Micron

□ A few more generations are possible. What's next?

### **NAND Memory**

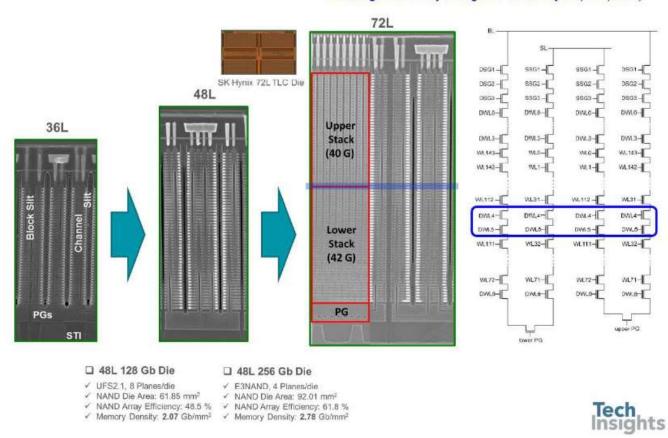

TechInsights Memory Design on Cell Array Report (MDC)

#### Low NAND cell current issue Junction Engineering, S/A Design

#### ✓ Select Transistor VT Controllability

- Fringing Field, Doping, Programmed SG

- Mobility (GB, trimmed Si Channel) Engineering

✓ PGM/ERS Speed @ same retention

#### Multi-stack NAND Strings

- Currently 2 stacked (64L, 128L)

- 4 stacked (128L, 256L) or more (512L)

#### ✓ HAR Plasma Etching and Filling

- Channel tube etch, CSL etch (> 90:1, 96/128L)

- Uniform Filling (Si or metal)

#### ✓ WL Cell Contacts Formation

Throughput and cost issue

#### ✓ Decoder TR Reliability

• HV + MV

#### Dtox (narrow SiON profile) ✓ e-migration in CTL

- Deep trap, Laminated CTL

- Cell coupling, Cell VT distribution issue

ONOA uniformity,

#### ✓ PGM/ERS Controllability

- Negative WL PGM VT

- PGM bias condition

- ✓ COP Opt., Triple Oxide (LLV, LV, HV), Chip size, Defect free, Yield, Low Power

$\checkmark$

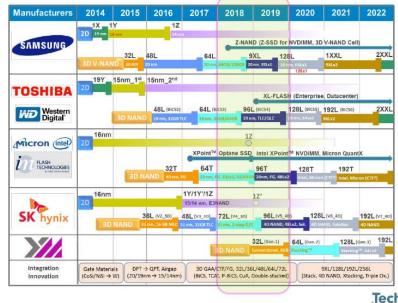

□ Transitioned from planar to 3D ~ 2015.

- □ Today in production: 94 tiers, 256 Gbits, 59 mm<sup>2</sup>

- □ The roadmap is to increase tiers. How far can it go?

# **Storage Class Memory and the Future Path**

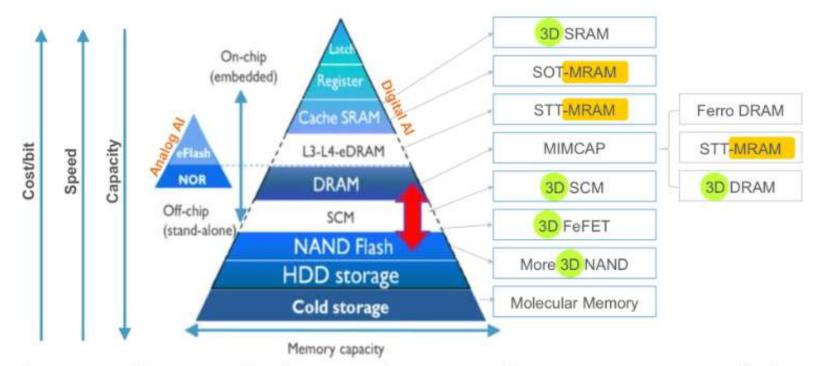

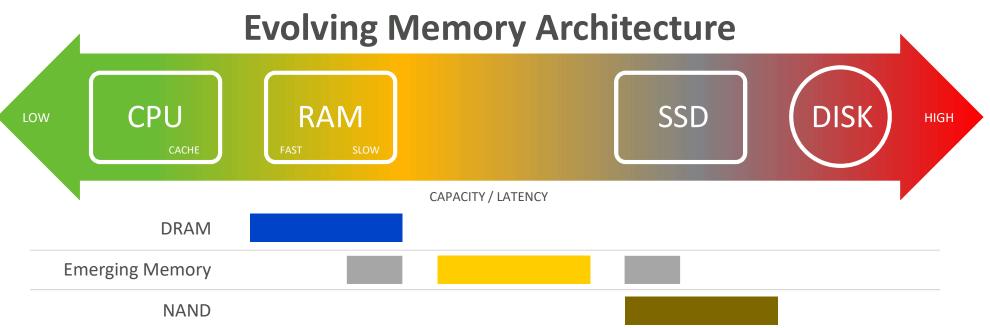

### **Position of emerging memory**

Fig 1: Emerging Memories for Pervasive Data and Compute Source: Applied Materials

It's hard to directly replace DRAM and NAND with emerging memory as they continue to scale

Emerging memory deployment has been confined to niche markets with low density devices

Storage class memory offers the opportunity for new memories to access a much larger market

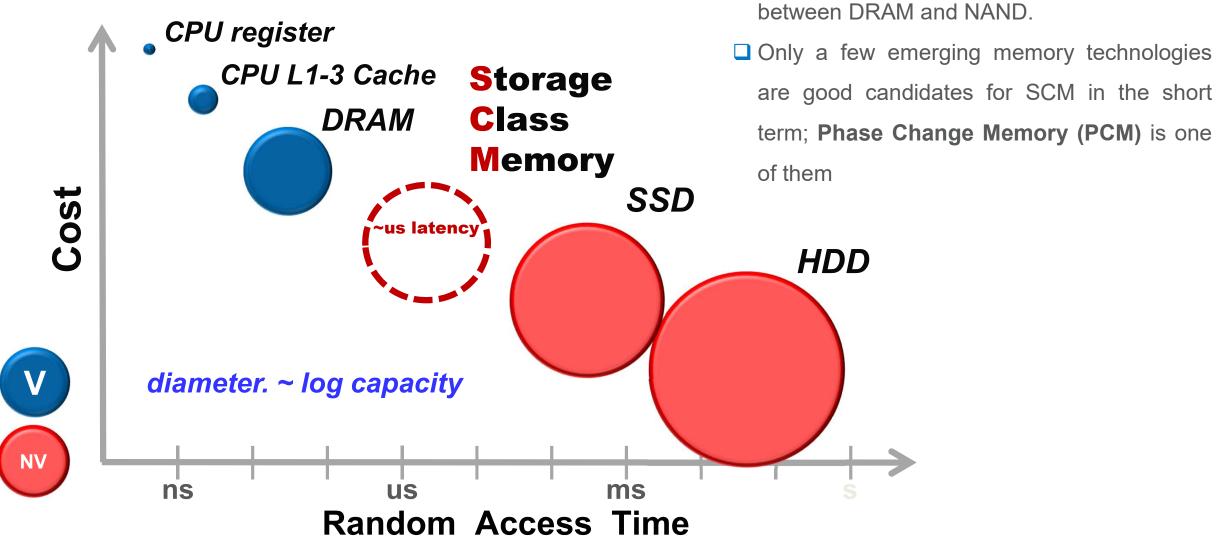

### Why Storage Class Memory?

From Rich Fackenthal, ISSCC 2014

Fills the gap in the memory hierarchy

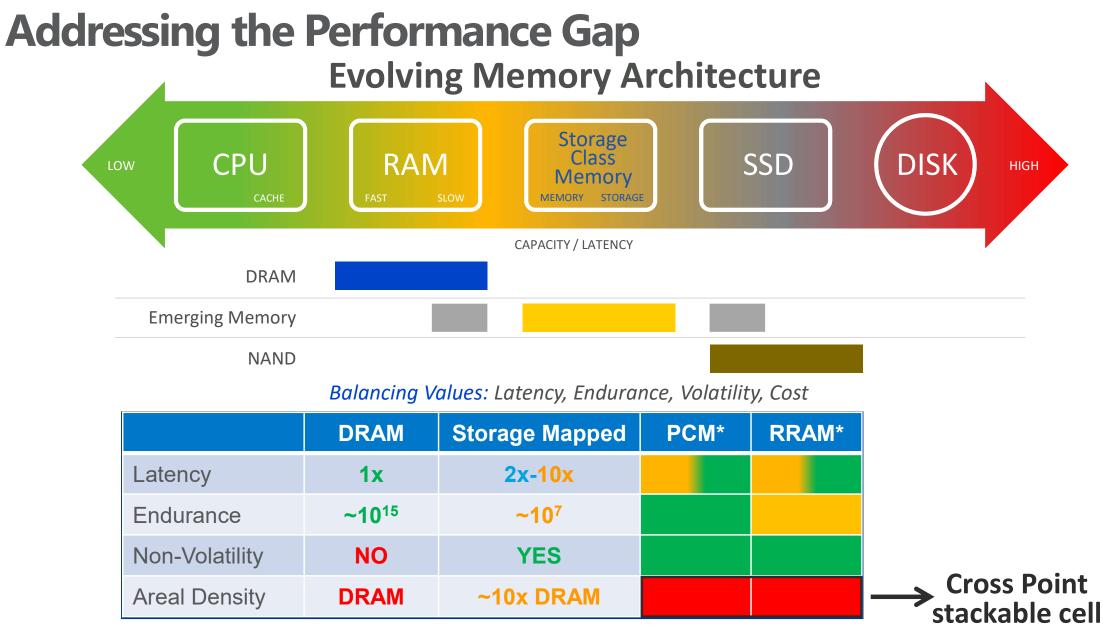

### Addressing the Performance Gap

#### Balancing Values: Latency, Endurance, Volatility, Cost

|                | DRAM                     | NAND                    |

|----------------|--------------------------|-------------------------|

| Latency        | 1x                       | 1000x                   |

| Endurance      | <b>~10</b> <sup>15</sup> | <b>~10</b> <sup>3</sup> |

| Non-Volatility | NO                       | YES                     |

| Areal Density  | DRAM                     | NAND                    |

#### **Addressing the Performance Gap Evolving Memory Architecture** Storage DISK Class CPU RAM SSD LOW HIGH Memory MEMORY STORAGE CAPACITY / LATENCY DRAM **Emerging Memory** NAND

#### Balancing Values: Latency, Endurance, Volatility, Cost

|                | DRAM                     | Memory Mapped                   | Storage Mapped | NAND         |

|----------------|--------------------------|---------------------------------|----------------|--------------|

| Latency        | <b>1</b> x               | <b>2</b> x                      | <b>2x-10x</b>  | 1000x        |

| Endurance      | <b>~10</b> <sup>15</sup> | <b>~10</b> <sup>13</sup>        | ~107           | <b>~10</b> ³ |

| Non-Volatility | NO                       | NO (>10x t <sub>refresh</sub> ) | YES            | YES          |

| Areal Density  | DRAM                     | ~DRAM                           | ~10x DRAM      | NAND         |

#### **Addressing the Performance Gap Evolving Memory Architecture** Storage Class DISK CPU SSD RAM LOW HIGH Memory MEMORY STORAGE CAPACITY / LATENCY DRAM **Emerging Memory** NAND **Balancing Values:** Latency, Endurance, Volatility, Cost **Storage Mapped** DRAM PCM\* **RRAM\*** 2x-10x Latency **1**x ~1015 ~107 Endurance

Latency1x2x-10xEndurance~1015~107Non-VolatilityNOYESAreal DensityDRAM~10x DRAM

\* Color codes referred to "Storage Mapped" specifications

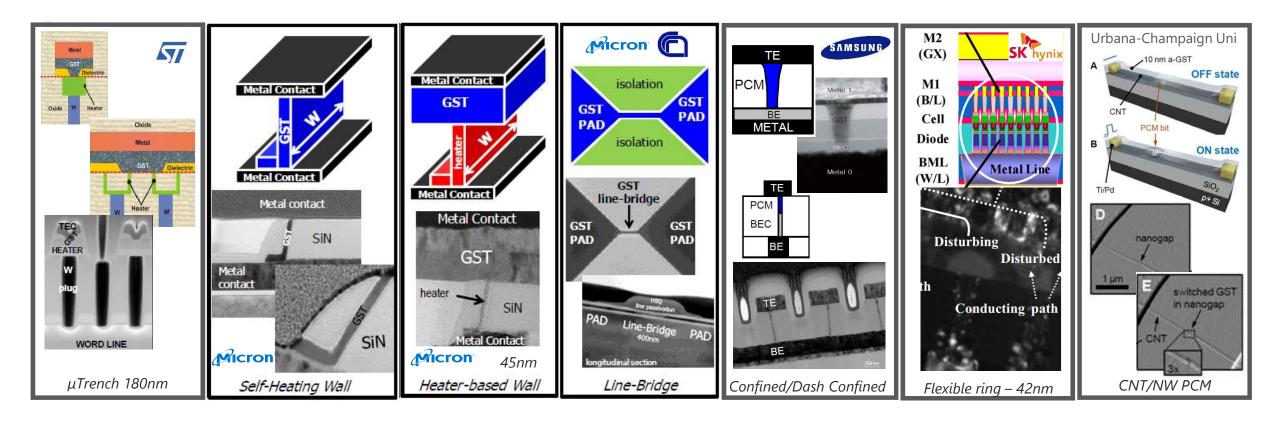

### **PCM Cell Architectures design**

Two families: self-heating PCM and heater-based PCM

- □ The different architectures aim at minimize both power consumption and latency

- □ All of them use a silicon based selector, which limits density and cost

### **PCM Applications**

#### Low to mid–end mobile phones

- NOR replacement with better performance:

- Higher throughput

- Single bit overwrite

- Execution in place (XIP)

#### PCM SSD prototype

- Improved performances vs. NAND SSD

- Much higher cost

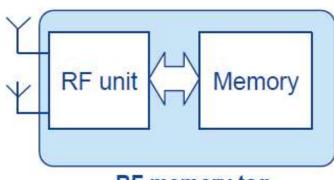

#### Wireless Memory

TAG (RF Memory TAG System)

IMW 2012 Nokia/Micron

#### Wireless memory

RF memory tag Without battery

#### PCM SSD prototype

|                           |            | PCM Prototype SSD     | NAND NAND SSD            |  |

|---------------------------|------------|-----------------------|--------------------------|--|

| System Interface          |            | PCIe 3.0x8            | PCIe 2.0x8               |  |

| Sector Access Granularity |            | 4096 byte             | 4096 byte                |  |

| Random<br>Reads           | Bandwidth  | 5.5 GB/s<br>> 1M IOPS | 3.0 GB/s<br>725,000 IOPS |  |

|                           | HW Latency | 5µs                   | ~50µs                    |  |

|                           | SW Latency | TBD                   |                          |  |

| Random<br>Writes          | Bandwidth  | ~625 MB/s             | 400 MB/s                 |  |

|                           | HW Latency | ≝ ~204 μs             | 300 µs                   |  |

|                           | SW Latency | TBD                   |                          |  |

| Density                   |            | 64 GByte              | 350GB, 700GB             |  |

| Total Pbytes (Life)       |            | ≥ 120 PB              | 25 PB (350GB)            |  |

G. Atwood, "Phase change memory: device physics, reliability and applications", Springer 2018

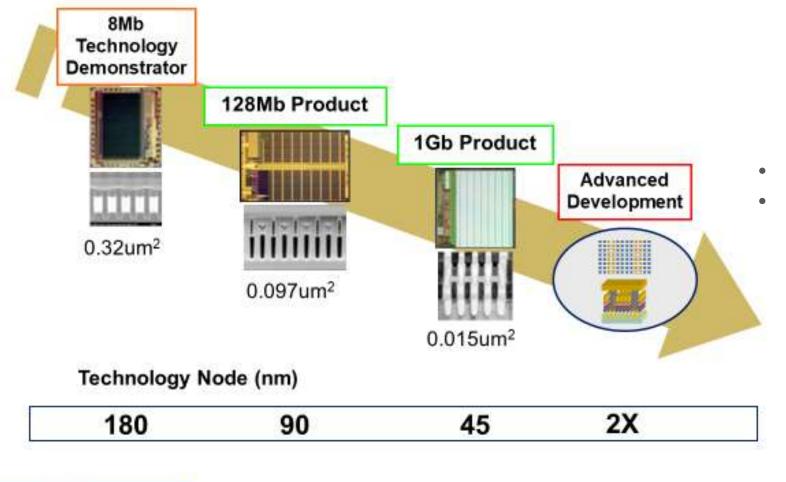

### From my 2012 Presentation

### PCM Technology Roadmap

- PCM technology was capable

- Scaling path showed insufficient market opportunity

#### **Addressing the Performance Gap Evolving Memory Architecture** Storage Class DISK CPU SSD RAM LOW HIGH Memory MEMORY STORAGE CAPACITY / LATENCY DRAM **Emerging Memory** NAND **Balancing Values:** Latency, Endurance, Volatility, Cost **Storage Mapped** DRAM PCM\* **RRAM\*** 2x-10x Latency **1**x ~1015 ~107 Endurance

Latency1x2x-10xEndurance~1015~107Non-VolatilityNOYESAreal DensityDRAM~10x DRAM

\* Color codes referred to "Storage Mapped" specifications

\* Color codes referred to "Storage Mapped" specifications

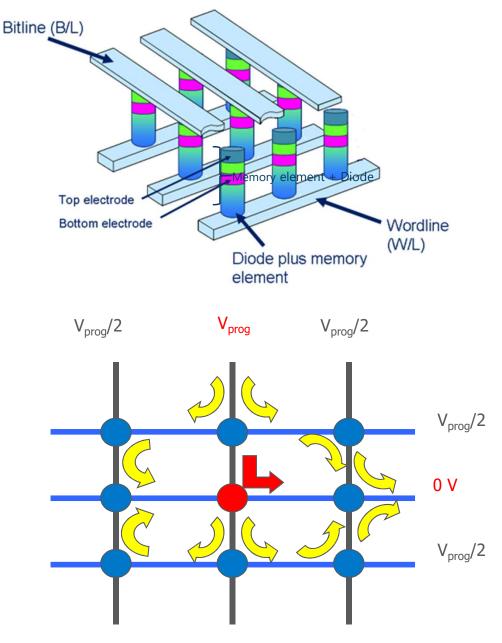

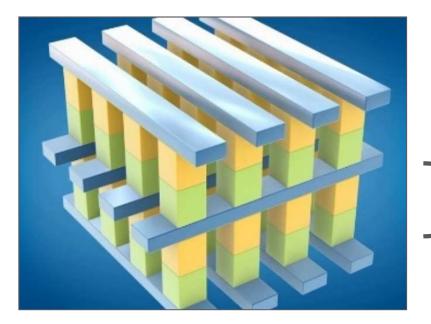

### **Cross Point Memory Architecture**

- To compete in the mainstream memory market, cost must be competitive. 3D stacking is required for any emerging memory.

- □ The cross point memory attracts great interest

- > "Simple" structure and minimum cell size (4F<sup>2</sup>)  $\rightarrow$  low cost

- > Suitable for 3D stacking  $\rightarrow$  cell size (4/n)F<sup>2</sup>

- > Array over circuitry  $\rightarrow$  better array efficiency

- The cross point's 2-terminal architecture requires a selector device to be integrated in the BEOL

- Parasitic paths exist through neighboring cells

- Programming and reading can disturb the array

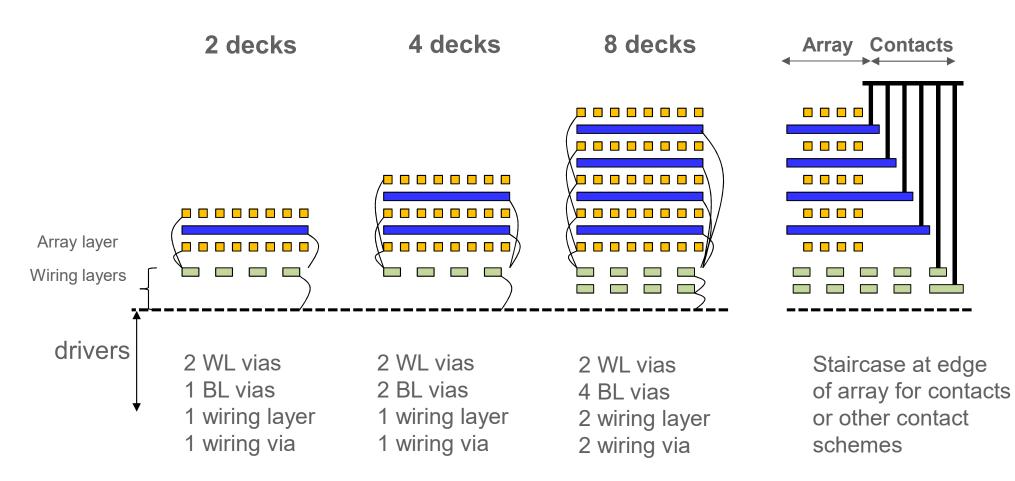

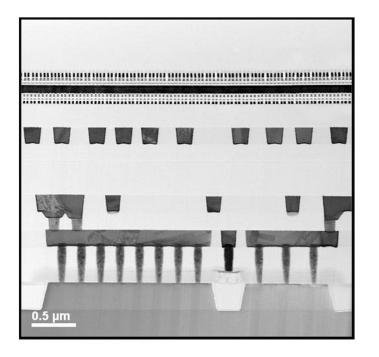

### **Planar 3D Stacking**

As the number of decks increases, interconnect and via levels increase

Cost Increases, complexity increases

Nirmal Ramaswamy, 2017 IEDM Short Course

Nirmal Ramaswamy, 2017 IEDM Short Course

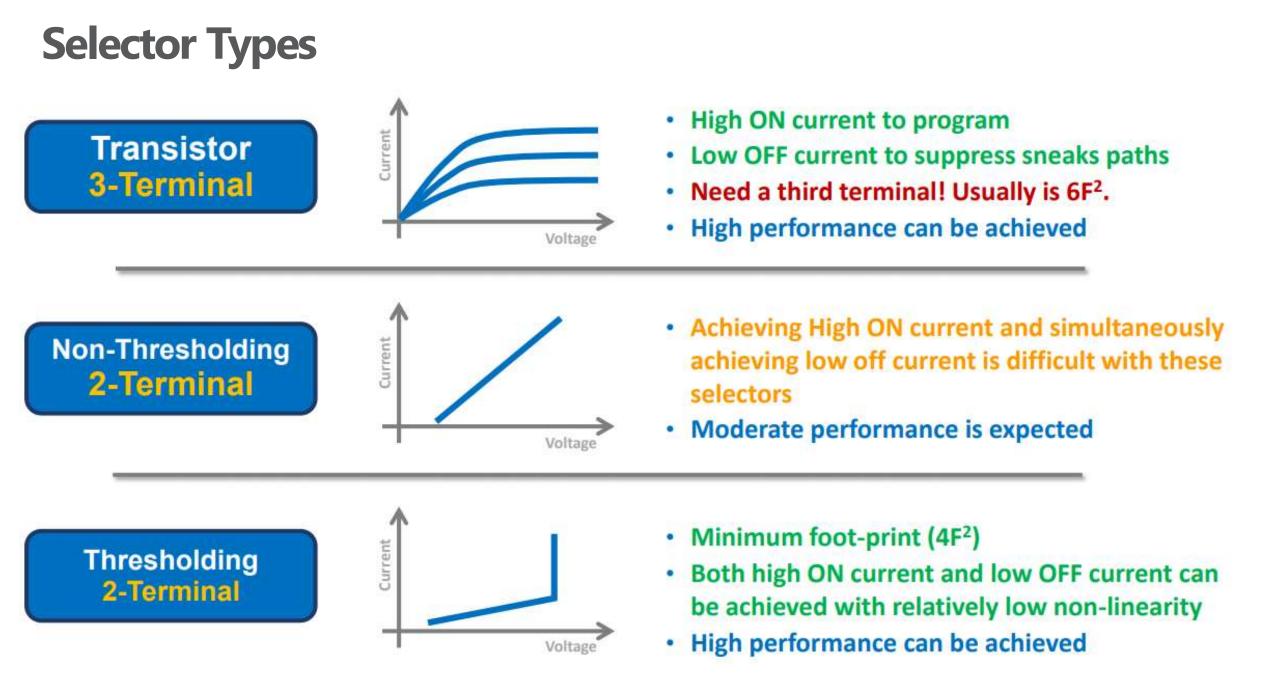

### **Cross Point Selector Requirements**

Selector device requirements:

- Very high forward bias current when selected

- Greater than the switching current

- Low deselect current

- Prevent loss of signal

- Leakage may set the block size

- Composition compatible with memory material

- Low temperature process

- Bipolar operation is preferred

- Selector device options:

- Homojunctions  $\rightarrow$  poly Si p/n junctions

- Heterojunctions  $\rightarrow$  p-CuO/n-InZnO

- Schottky diode  $\rightarrow$  Ag/n-ZnO

- Mixed Ionic Electronic Conduction (MIEC) materials

- Thin-film chalcogenide selector

In addition, selector reliability must be capable of meeting the cell reliability requirements.

### **3D XPoint<sup>TM</sup> Technology**

Cross Point architecture

- Storage element

- Fast and reliable switching device based on thin-film material

- Circuitry under the array

- 2 decks of 64Gb each

- □ 3D XPoint key advantages

- Better performance than NAND and lower cost than DRAM

- Low-latency and fast writes

- Intel and Micron announced 3D XPoint technology in 2015. Objective Analysis (2019 Flash Memory Summit) predicts that 3D XPoint media revenue will grow to more than \$3 billion in 2023.

Storage element + Switching element

# Conclusions

### Conclusions

- The semiconductor memory market is rapidly expanding, fueled by new market trends.

- Conventional NAND and DRAM currently dominate the market and should continue to do so in the near future.

- Most memory technologies have developed or are investigating 3D architectures due to limitations with 2D scaling.

- 3D capability is a requirement for any emerging memory seeking to replace the incumbents.

- There is an opportunity for a storage class memory to improve system level performance. SCM could create a significant market opportunity for a new memory.

- Success of emerging memory as an SCM depends both on the technology's capability as well as enabling the ecosystem.

- With Intel/Micron's vertical integration capability, 3DXpoint<sup>TM</sup> is the ideal candidate as an SCM both in the storage and memory replacement.