# Non-Volatile Memory Technology: Directions Beyond Floating Gate Devices

### Bob Gleixner and Chandra Mouli

Micron Technology

©2013 Micron Technology, Inc. All rights reserved. Products are warranted only to meet Micron's production data sheet specifications. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Dates are estimates only. Drawings are not to scale. Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

## Two question to ask (for a new NVM)...

What are the cost/performance characteristics required to add *significant* value in computing devices?

For the leading emerging NVM's, what materials improvements are needed to realize this value?

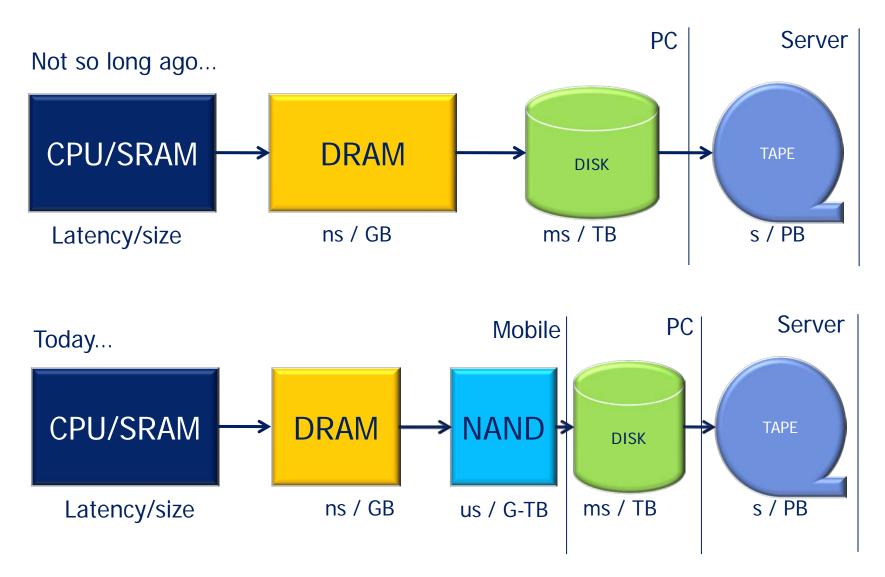

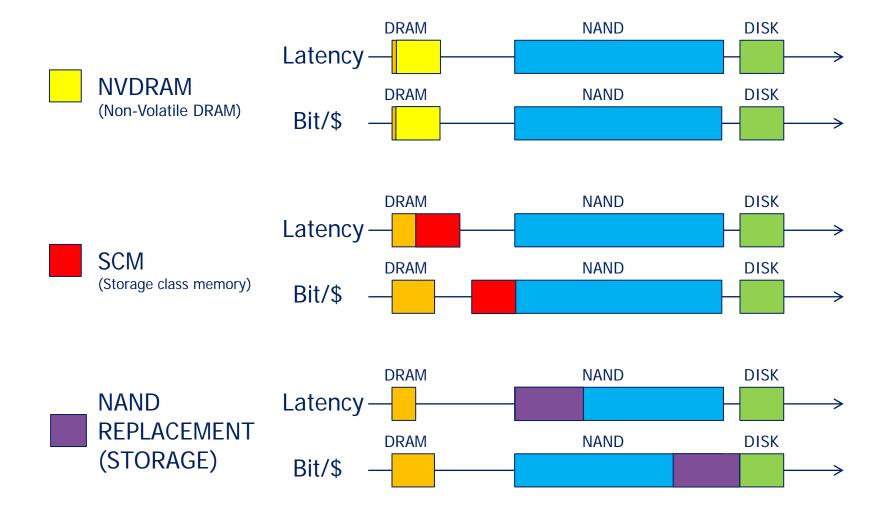

# Computing memory hierarchy

## Where could a new memory add value?

(Assumption – you find a niche to grow)

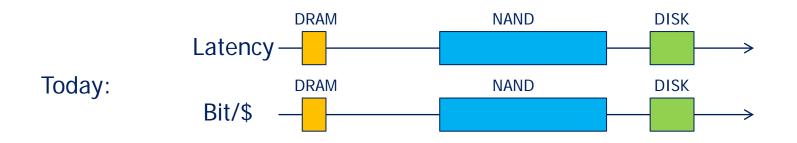

### NAND had a big "hole to fill" in 2009

| Normalized<br>Parameters | DRAM | NAND  | HDD       |

|--------------------------|------|-------|-----------|

| Latency                  | 1x   | ~500x | ~100,000x |

| \$/Bit                   | 1x   | ~0.1x | ~0.01x    |

A. Fazio, IEDM 2009

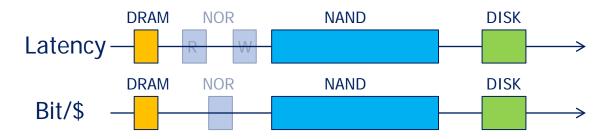

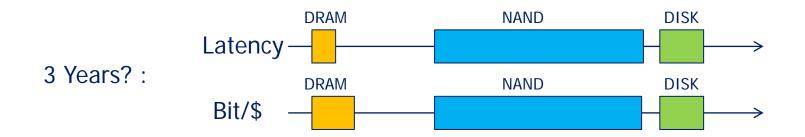

### What do the holes look like today?

More importantly, what does this look like in 3-5 years?

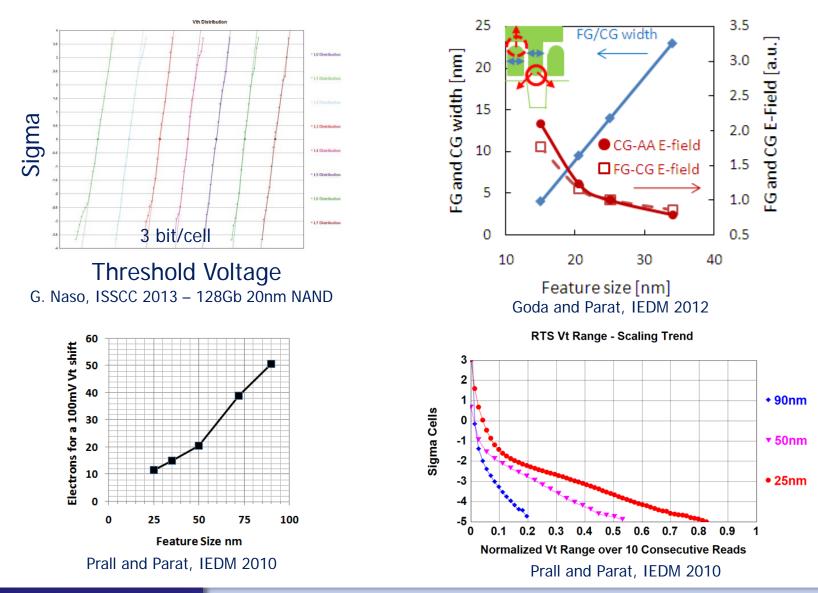

## Planar NAND is getting tough to scale...

## ... but continues to find solutions

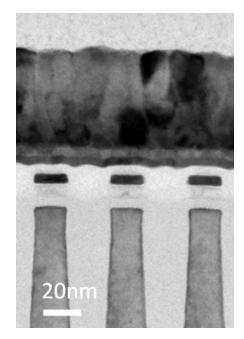

### Planar floating gate cell

Goda and Parat, IEDM 2012

### 16nm NAND announced

Micron

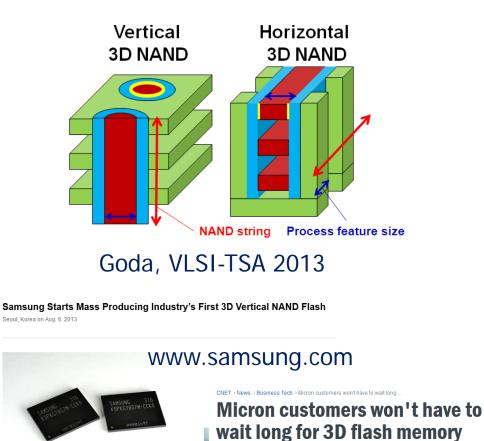

### **3D NAND**

quarter of 2014. Represents a breakthrough in overcoming NAND scaling limit; ushers in new 3D memory era

CEO Mark Durcan tells CNET that the company will start providing samples of the advanced memory technology to customers in the first

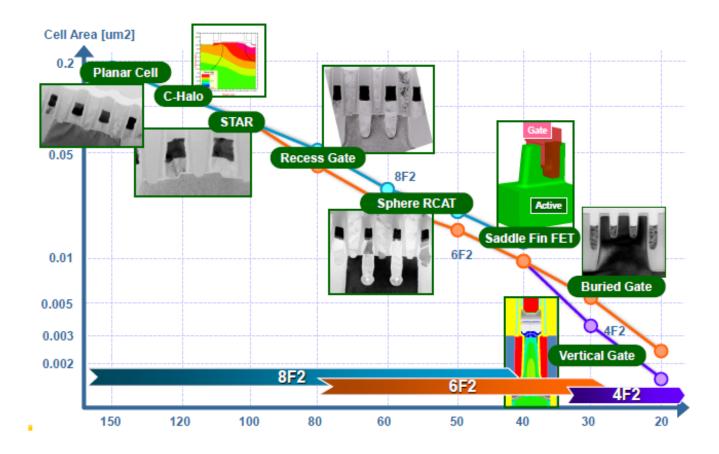

## While DRAM continues to scale

Seon Yong Cha, IEDM short course, 2011

## Main vector in DRAM/NAND: Cost reduction

# Where can an emerging memory fit in?

## Consider the "top 4" emerging memories

| Technology | Company           | Niche                                        |

|------------|-------------------|----------------------------------------------|

| RRAM       | Adesto            | EEPROM Replacement                           |

| MRAM       | Everspin          | Ultra high Reliability<br>BBSRAM replacement |

| STRAM      | Crocus            | Embedded<br>Security                         |

| FERAM      | TI                | Embedded                                     |

| FERAM      | Ramtron           | Low Density – Power<br>Meters                |

| РСМ        | Samsung<br>Micron | NOR replacement-<br>Wireless applications    |

Prall, IMW 2012

FIGURE 15: Memory capacity of emerging nonvolatile memories.

IEEE Solid-State Circuits Mag. Spring 2013

Micron

©2013 Micron Technology, Inc. | 10

## Memory "scorecard"

- Cost / bit

- Small bit cell

- Low programming energy

- Multi-level or multi-layer

- Latency

- Fast read (large signal + memory window)

- Fast / deterministic writes

- Write endurance

|                        | Planar<br>NAND            | DRAM                     |

|------------------------|---------------------------|--------------------------|

| Cost                   |                           |                          |

| Cell size              | 4F <sup>2</sup><br>16nm   | 6F <sup>2</sup><br>2x nm |

| Programming<br>energy  | Low                       | (Refresh)                |

| Multi-level /<br>layer | 1-3 BPC                   | None                     |

| Latency                |                           |                          |

| Fast read              | 10uS<br><sub>(page)</sub> | ~10ns                    |

| Fast write             | 1mS<br><sub>(page)</sub>  | ~10ns                    |

| Endurance              | 1-100k                    | >1e15                    |

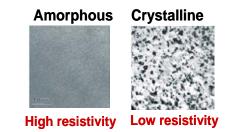

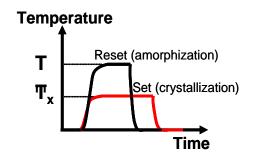

# Phase Change Memory (PCM)

- Storage mechanism

- Amorphous/poly-crystal phase of chalcogenide alloy (Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> – GST)

- Writing mechanism

- Current-induced Joule heating

- Sensing signal

- Resistance change of the GST

- Cell structure

Micron

1 transistor, 1 resistor (1T/1R)

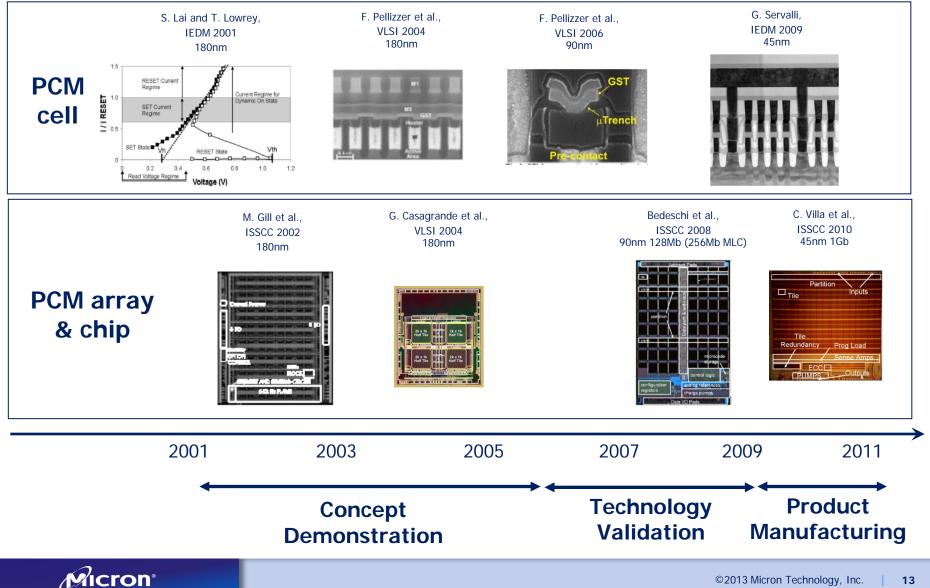

# History of PCM Silicon Development

<sup>©2013</sup> Micron Technology, Inc. 13

### PCM Scorecard

|                     | Planar<br>NAND            | DRAM                     | РСМ                     |

|---------------------|---------------------------|--------------------------|-------------------------|

| Cost Overall        |                           |                          |                         |

| Cell size           | 4F <sup>2</sup><br>16nm   | 6F <sup>2</sup><br>2x nm | 4F <sup>2</sup><br>20nm |

| Programming energy  | Low                       | (Refresh)                | ~High I                 |

| Multi-level / layer | 1-3 BPC                   | None                     | Level/Layer             |

| Latency Overall     |                           |                          |                         |

| Fast read           | 10uS<br><sub>(page)</sub> | ~10ns                    | <100ns                  |

| Fast write          | 1mS<br>(page)             | ~10ns                    | >100ns                  |

| Endurance           | 1-100k                    | >1e15                    | 1e8                     |

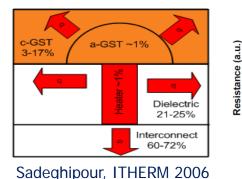

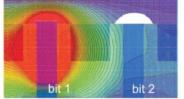

## **PCM Cell Challenges**

### High programming current

Micron

20nm cell 0 20 40 60 80 100 120 140 160 180 *Ireset* (uA) Kang, IEDM 2011

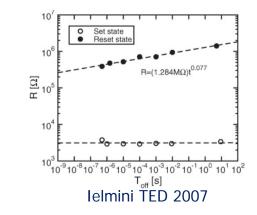

Resistance drift (MLC)

Programming speed to SET/crystallized state

Thermal disturb

90 nm structure (a)

45 nm non-isotropic (b) R 45

bit

bit 1

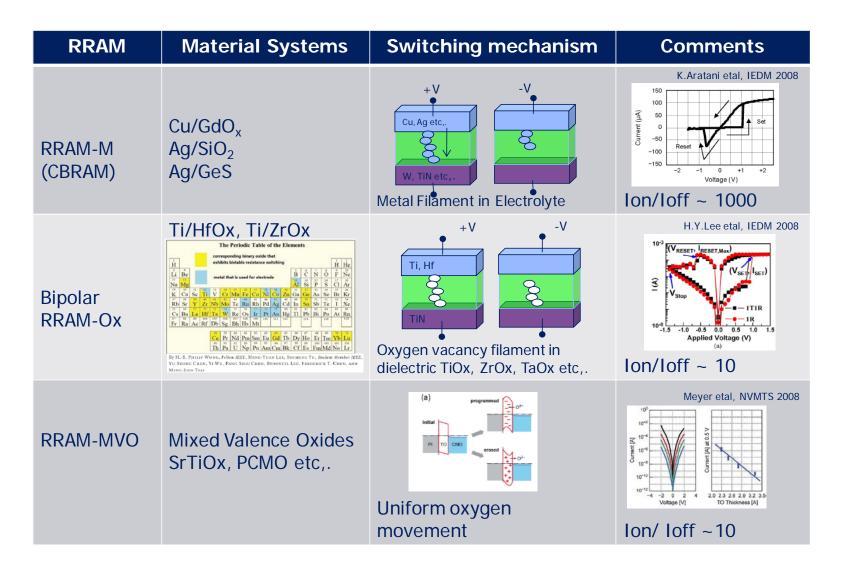

### RRAM

### **RRAM Scorecard**

|                     | Planar<br>NAND            | DRAM                     | RRAM                    |

|---------------------|---------------------------|--------------------------|-------------------------|

| Cost Overall        |                           |                          |                         |

| Cell size           | 4F <sup>2</sup><br>16nm   | 6F <sup>2</sup><br>2x nm | 4F <sup>2</sup><br>20nm |

| Programming energy  | Low                       | (Refresh)                | Low - Med               |

| Multi-level / layer | 1-3 BPC                   | None                     | Level/Layer             |

| Latency Overall     |                           |                          |                         |

| Fast read           | 10uS<br><sub>(page)</sub> | ~10ns                    | <100ns                  |

| Fast write          | 1mS<br>(page)             | ~10ns                    | ~10nS                   |

| Endurance           | 1-100k                    | >1e15                    | 1e8 ??                  |

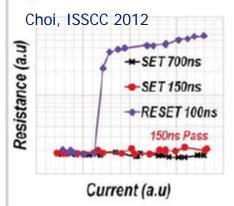

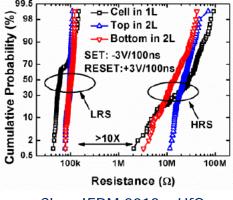

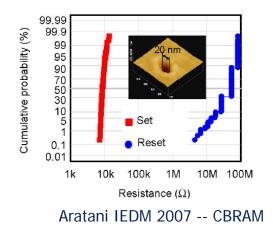

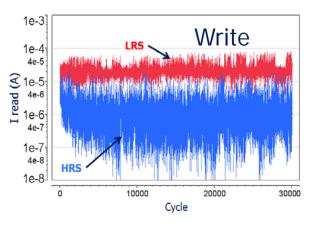

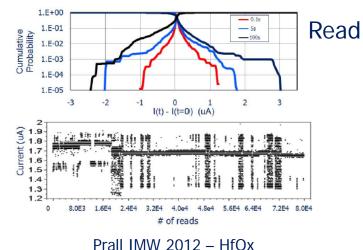

### **RRAM Cell Challenges**

Micron

Chen IEDM 2012 - HfOx

### Write current scalability?

Noise

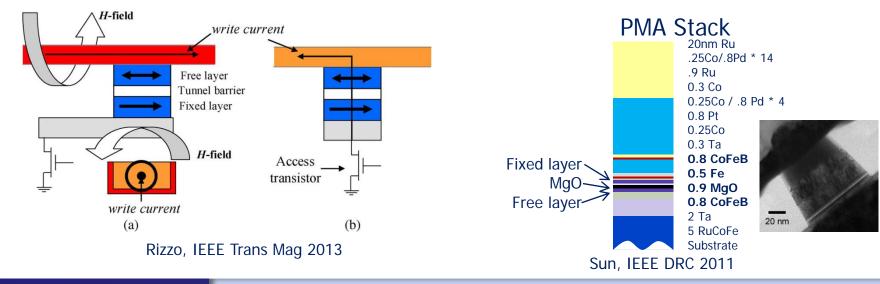

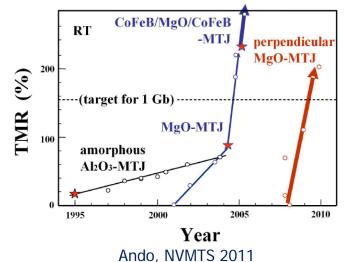

### MRAM

### Fast switching could enable DRAM replacement

#### **FEATURES**

Micron

- +3.3 Volt power supply

- Fast 35 ns read/write cycle

- SRAM compatible timing

- · Unlimited read & write endurance

- Data always non-volatile for >20 years at temperature

- RoHS-compliant small footprint BGA and TSOP2 package

- AEC-Q100 Grade 1 option in TSOP2 package.

**MR4A16B**

1M x 16 MRAM

MR4A16B Datasheet, www.everspin.com

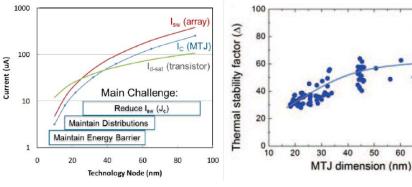

### But field / toggle MRAM cell too large $\rightarrow$ STT-MRAM

### **STT-MRAM Scorecard**

|                     | Planar<br>NAND          | DRAM                     | STT-<br>MRAM            |

|---------------------|-------------------------|--------------------------|-------------------------|

| Cost Overall        |                         |                          |                         |

| Cell size           | 4F <sup>2</sup><br>16nm | 6F <sup>2</sup><br>2x nm | 6F <sup>2</sup><br>20nm |

| Programming energy  | Low                     | (Refresh)                | Med I                   |

| Multi-level / layer | 1-3 BPC                 | None                     | Layer                   |

| Latency Overall     |                         |                          |                         |

| Fast read           | 10uS<br>(page)          | ~10ns                    | < 30ns                  |

| Fast write          | 1mS<br>(page)           | ~10ns                    | ~10ns                   |

| Endurance           | 1-100k                  | >1e15                    | >1e15                   |

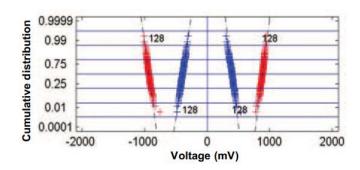

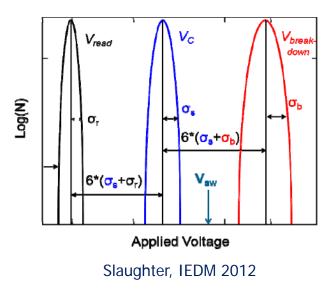

## **STT-MRAM Cell Challenges**

### Writing current vs. stability

Park, VLSI 2012

60 70 80

Operating window

Tunnel junction reliability

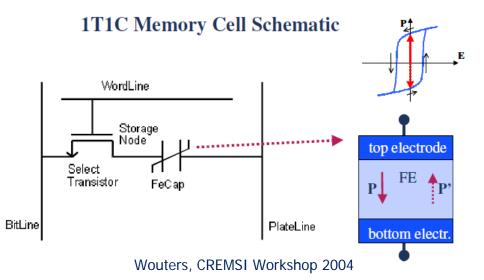

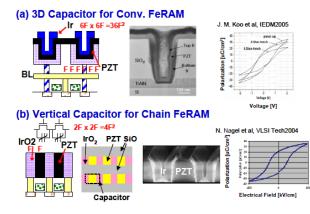

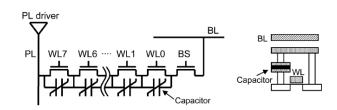

### FERAM

- Stores "charge" in a polarizable material

- Typically PZT

As with field/toggle MRAM, performance is similar to DRAM

#### FM23MLD16

8Mbit F-RAM Memory

#### Features

#### 8Mbit Ferroelectric Nonvolatile RAM

- Organized as 512Kx16

- Configurable as 1Mx8 Using /UB, /LB

- High Endurance 100 Trillion (10<sup>14</sup>) Read/Writes

- NoDelay<sup>™</sup> Writes

- Page Mode Operation to 33MHz

- Advanced High-Reliability Ferroelectric Process

#### SRAM Compatible

- JEDEC 512Kx16 SRAM Pinout

- 60 ns Access Time, 115 ns Cycle Time

#### Advanced Features

Low V<sub>DD</sub> Monitor Protects Memory against Inadvertent Writes

### RAMTRON

Superior to Battery-backed SRAM Modules

- No Battery Concerns

- Monolithic Reliability

- True Surface Mount Solution, No Rework Steps

- Superior for Moisture, Shock, and Vibration

#### Low Power Operation

- 2.7V 3.6V Power Supply

- 14 mA Active Current

#### Industry Standard Configuration

- Industrial Temperature -40° C to +85° C

- 48-pin "Green"/RoHS FBGA package

#### http://www.cypress.com/

### **FERAM Scorecard**

|                     | Planar<br>NAND           | DRAM                     | FERAM  |

|---------------------|--------------------------|--------------------------|--------|

| Cost Overall        |                          |                          |        |

| Cell size           | 4F <sup>2</sup><br>16nm  | 6F <sup>2</sup><br>2x nm | >100nm |

| Programming energy  | Low                      | (Refresh)                | Low    |

| Multi-level / layer | 1-3 BPC                  | None                     | Layer? |

| Latency Overall     |                          |                          |        |

| Fast read           | 10uS (page)              | ~10ns                    | ~10ns  |

| Fast write          | 1mS<br><sub>(page)</sub> | ~10ns                    | ~10ns  |

| Endurance           | 1-100k                   | >1e15                    | >1e14  |

## **FERAM Cell Challenges**

Need to reduce cells size – limited by polarization / bitline cap ratio

|                      | D. Takashima et al., MRS Spring Meeting 2011 |                     |                    |                          |                      |                      |  |

|----------------------|----------------------------------------------|---------------------|--------------------|--------------------------|----------------------|----------------------|--|

| Design Rule          |                                              | 0.5µm               | 0.25µm             | 0.2µm                    | 130nm                | 130nm+DualOx         |  |

| Capacity             |                                              | 16Kb                | 8Mb                | 32Mb                     | 64Mb                 | 128Mb                |  |

| Chip                 |                                              | ISSCC1999           | SSCC2001           | issec2003                | ISSCC2006            | ISSCC2009            |  |

| Cell Struc           | ture                                         | Offset Cell         | Offset Cell        | Stacked Cell 1-Mask Cell |                      | Adv. Twin Cell       |  |

| Capacit              | or                                           | Sputter PZT         | Sputter PZT        | Sputter PZT              | MOCVD PZT            | MOCVD PZT            |  |

| Cap. Siz             | ze                                           | 3.24µm²             | 0.855µm²           | 0.49µm²                  | 0.194µm²             | 0.098µm <sup>2</sup> |  |

| Cell Size            | Ave.                                         | 15.8µm <sup>2</sup> | 5.2µm <sup>2</sup> |                          | 0.719µm <sup>2</sup> | 0.32µm <sup>2</sup>  |  |

| Cell Size            | Pure                                         | 13.3µm²             | 4.2µm <sup>2</sup> | 1.539µm <sup>2</sup>     | 0.612µm <sup>2</sup> | 0.25µm²              |  |

| Proces               | S                                            | 2Metal              | 2Metal             | 3Metal                   | 3Metal               | 4Metal Dual Ox       |  |

|                      | Chip Size                                    |                     | 76mm <sup>2</sup>  | 96mm <sup>2</sup>        | 87.5mm <sup>2</sup>  | 87.7mm <sup>2</sup>  |  |

| R/W Cycle            |                                              | 80ns                | 70ns               | 75ns                     | 60ns                 | 75ns                 |  |

| Page/Burst           |                                              | 80ns                | 40ns               | 25ns                     | 10ns                 | 1.25ns               |  |

| <b>R/W Bandwidth</b> |                                              | 12.5MB/s            | 50MB/s             | 80MB/s                   | 200MB/s              | 1.6GB/s              |  |

| Vdd                  |                                              | 3.3V                | 3.3V               | 3.3V/2.5V                | 3.3V/2.5V            | 1.8V                 |  |

Considering cell / array architecture solutions

Shiga JSSC 2010

**Micron**<sup>®</sup>

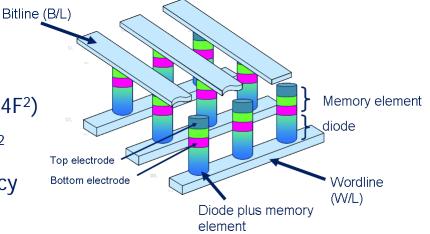

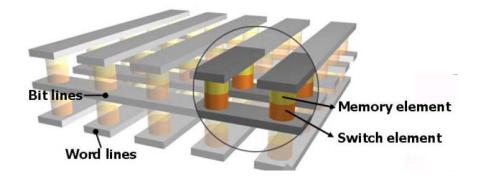

# Multi-Layer Memory

- Crossbar memory very attractive

- "Simple" structure and minimum cell size (4F<sup>2</sup>)

- Suitable for 3D stacking  $\rightarrow$  cell size (4/n)F<sup>2</sup>

- ► Array over circuitry → better array efficiency

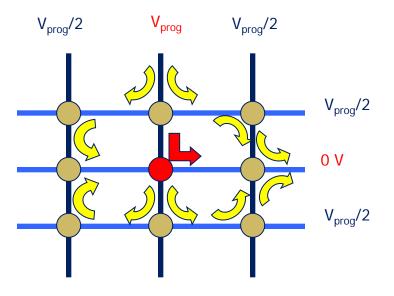

- The basic cell architecture requires a selector structure to be integrated in the BEOL

- Parasitic paths exist through neighboring cells

- Programming (and also reading) can perturb the array

## A Wide Range of Material Choices

For the selector structure several devices have been proposed so far, none have been "proven"

### Selector device options

- Homojunctions → polySi p/n junctions

- Heterojunctions → p-CuO/n-InZnO

- Schottky diode→ Ag/n-ZnO

- Chalcogenide Ovonic Threshold Switching (OTS) materials

- Mixed Ionic Electronic Conduction (MIEC) materials

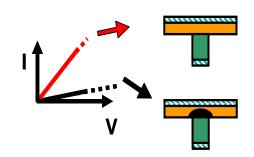

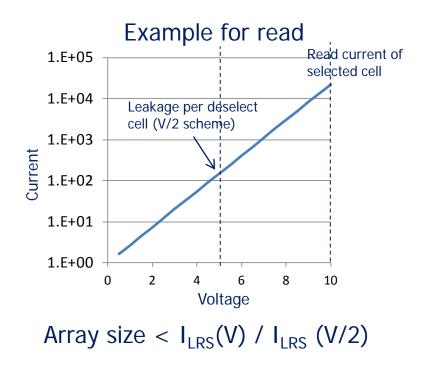

## **Cross-Point Switch Requirements**

- Very high forward bias current

- Greater than the switching current

- Low leakage through unselected cells

- Steep IV characteristic

- Bipolar operation may be required

- Necessary for bipolar RRAM

| Cell<br>Type | ~20nm Cell<br>Current | Current<br>density    |

|--------------|-----------------------|-----------------------|

| PCM          | 100uA                 | 10 MA/cm <sup>2</sup> |

| RRAM         | 10uA                  | 1 MA/cm <sup>2</sup>  |

# **Summary Scorecard**

|                        | Planar<br>NAND            | DRAM                     | РСМ                     | RRAM                    | STT-<br>MRAM            | FERAM  |

|------------------------|---------------------------|--------------------------|-------------------------|-------------------------|-------------------------|--------|

| Cost Overall           |                           |                          |                         |                         |                         |        |

| Cell size              | 4F <sup>2</sup><br>16nm   | 6F <sup>2</sup><br>2x nm | 4F <sup>2</sup><br>20nm | 4F <sup>2</sup><br>20nm | 6F <sup>2</sup><br>20nm | >100nm |

| Programming<br>energy  | Low                       | (Refresh)                | ~High I                 | Low - Med               | Med I                   | Low    |

| Multi-level /<br>layer | 1-3 BPC                   | None                     | Level/<br>Layer         | Level/<br>Layer         | Layer                   | Layer? |

| Latency<br>Overall     |                           |                          |                         |                         |                         |        |

| Fast read              | 10uS<br><sub>(page)</sub> | ~10ns                    | <100ns                  | <100ns                  | <30ns                   | ~10ns  |

| Fast write             | 1mS<br>(page)             | ~10ns                    | >100ns                  | ~10nS                   | ~10ns                   | ~10ns  |

| Endurance              | 1-100k                    | >1e15                    | 1e8                     | 1e8 ??                  | >1e15                   | >1e14  |

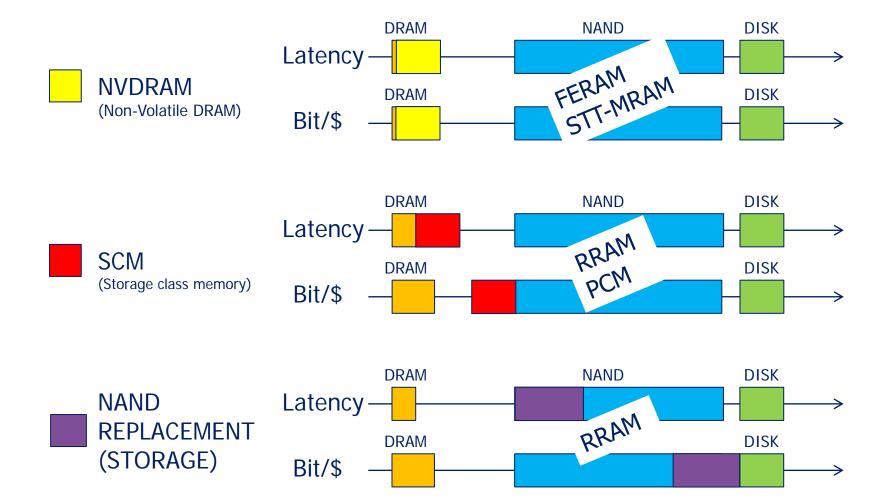

# Where can an emerging memory fit in?

# Summary

- Many new NVM technologies are attempting to gain a foothold in the computing devices

- While they have cost *or* performance advantages over NAND or DRAM, none beat the performance of DRAM or the cost of NAND

- The most direct fit would be a NAND/DRAM "blend" / SCM, but the system implementation for this type of memory is not yet established

- We need a few more advances in materials to make these a reality!

- Acknowledgments: Thanks to the Micron R&D team and the work of the authors presented here.