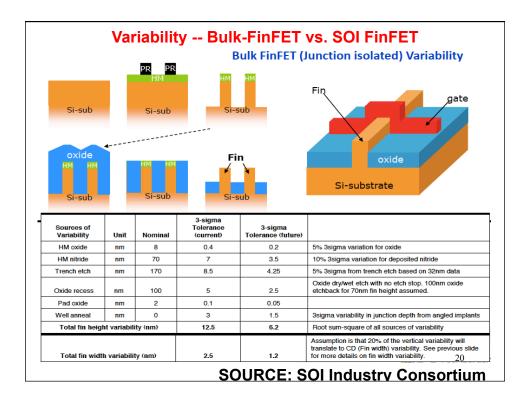

|                           | Va                                | riabilit                     | ty Bulk                           | -FinFET                          | vs. SOI FinFET                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|---------------------------|-----------------------------------|------------------------------|-----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SOI FinFE                 | TV                                | ariabi                       | lity                              |                                  | Fingate                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| SOI<br>BOX<br>Si-sut      | 2                                 | PR<br>HI<br>SC<br>BO<br>Si-s | X                                 | Fin<br>BOX<br>Si-sub             | BOX<br>Si-substrate<br>SOI-FinFET                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Sources of<br>Variability | Unit                              | Nominal                      | 3-sigma<br>Tolerance<br>(current) | 3-sigma<br>Tolerance<br>(future) |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| SOI Layer                 | nm                                | 70                           | 2                                 | 1                                | 5% 3sigma SOI thickness variability with future<br>improvements in high volume manufacturing                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Hardmask dep              | nm                                | 10                           | 1                                 | 0.5                              | 10% cross-wafer 3sigma                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Fin Etch                  | nm                                | 70                           | 4.2                               | 2.1                              | 5% cross wafer + 1% overetch                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Corner rounding           | nm                                | 2                            | 0.1                               | 0.05                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Total fin heigh           | Total fin height variability (nm) |                              |                                   | 2.4                              | Root sum-square of all sources of variability                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Total fin widt            | h variabil                        | ity (nm)                     | 1.0                               | 0.5                              | In 32nm technology, active area CD variability is 15nm<br>across iso-dense patterns, multiple pitchs and RIE<br>overetch from variability in vertical layers. For FinFETs,<br>most of the CD variability is expected to come from the<br>overetch to account for thickness variability in Fin<br>definition since the pitch will be fixed. Assumption is<br>that 20% of the vertical variability will translate to CD<br>(Fin width) variability. 19 |  |  |  |

|                           |                                   |                              | SO                                | URCE: S                          | OI Industry Consortium                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

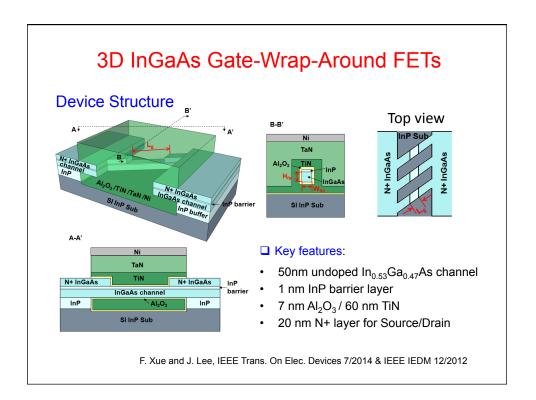

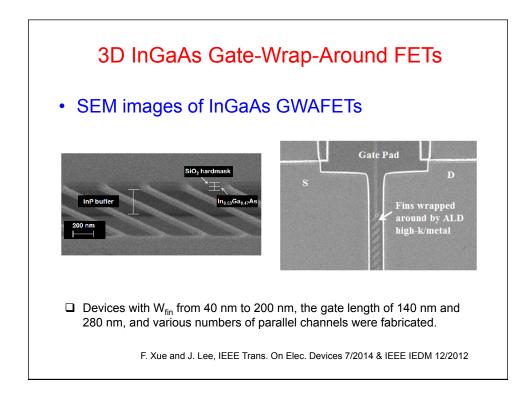

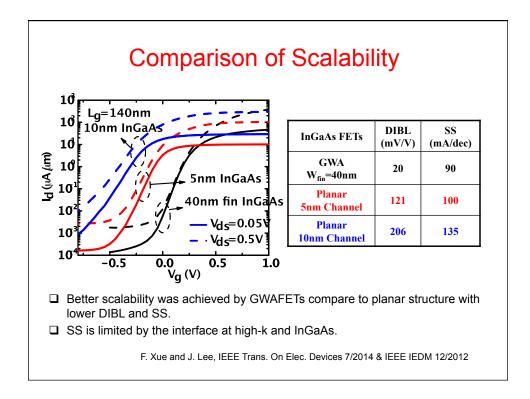

| Device                                                                            | Dielectric                                             | L <sub>g</sub><br>(nm) | W <sub>fin</sub><br>(nm) | I <sub>on</sub><br>(μΑ/μm)                                          | I <sub>off</sub><br>(nA/μm)   | DIBL<br>(mV/V) | SS<br>(mV/dec)               |

|-----------------------------------------------------------------------------------|--------------------------------------------------------|------------------------|--------------------------|---------------------------------------------------------------------|-------------------------------|----------------|------------------------------|

| In <sub>0.53</sub> Ga <sub>0.47</sub> As<br>GWAFET<br>(This work)                 | 7nm ALD<br>Al <sub>2</sub> O <sub>3</sub> /<br>1nm InP | 140                    | 40                       | 600<br>(V <sub>d</sub> =1V,<br>V <sub>g</sub> -V <sub>th</sub> =1V) | 6<br>(V <sub>d</sub> =1V)     | 20             | 90<br>(V <sub>d</sub> =0.5V  |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As<br>GAAFET<br>(Purdue, IEDM<br>2011)      | 10nm ALD<br>Al <sub>2</sub> O <sub>3</sub>             | 50                     | 30                       | 450<br>(V <sub>d</sub> =1V,<br>V <sub>g</sub> -V <sub>th</sub> =1V) | 4000<br>(V <sub>d</sub> =1V)  | 210            | 150                          |

|                                                                                   |                                                        | 110                    | 30                       | 355<br>(V <sub>d</sub> =1V,<br>V <sub>g</sub> -V <sub>th</sub> =1V) | 4000<br>(V <sub>d</sub> =1V)  | 180            | 140                          |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As<br>Tri-gate FET<br>(Intel, IEDM<br>2011) | High-k<br>Stack<br>EOT=12Å                             | 60                     | 40                       | 360<br>(V <sub>d</sub> =0.5V,<br>V <sub>g</sub> =0.5V)              | 100<br>(V <sub>d</sub> =0.5V) | 65             | 100<br>(V <sub>d</sub> =0.5V |

|                                                                                   |                                                        | 120                    | 30                       |                                                                     |                               | 35             | 85<br>(V <sub>d</sub> =0.5V  |

| In <sub>0.7</sub> Ga <sub>0.3</sub> As<br>FinFET<br>(NUS, EDL<br>2011 )           | 19nm<br>MOCVD<br>HfAlO                                 | 130                    | 220                      | 220<br>(V <sub>d</sub> =1V,<br>V <sub>g</sub> -V <sub>th</sub> =1V) | 10<br>(V <sub>d</sub> =1.2V)  | 135            | 230                          |

| In <sub>0.7</sub> Ga <sub>0.3</sub> As<br>Planer<br>QWFET<br>(UT, EDL 2012)       | 6nm ALD<br>Al <sub>2</sub> O <sub>3</sub> /<br>1nm InP | 40                     |                          | 476<br>(V <sub>d</sub> =1V,<br>V <sub>g</sub> -V <sub>th</sub> =1V) | 100<br>(V <sub>d</sub> =1V)   | 270            | 140                          |

|                                                                                   |                                                        | 130                    |                          | 430<br>(V <sub>d</sub> =1V,<br>V <sub>g</sub> -V <sub>th</sub> =1V) | 100<br>(V <sub>d</sub> =1V)   | 206            | 135                          |