# Integration of Disruptive Materials for Advanced Non-Volatile Memories

# Wilbur Catabay

NCCAVS PAG User Group Meeting

"Plasma Applications in Novel Materials Processing"

April 29, 2013

- TSI Semiconductor, TDCS Overview

- Non Volatile Memory Trends

- Solutions for NVM Memory Development

- Process Module Blocks

- Summary

- Who, What is "Telefunken"?

- German radio and television apparatus company, founded in Berlin 1903

Telefunken water boiling from 2011

A modern Telefunken RC 881 cassette, CD player, and radio

TELEFUNKEN Semiconductors International is a US company & Incorporated in State of Delaware

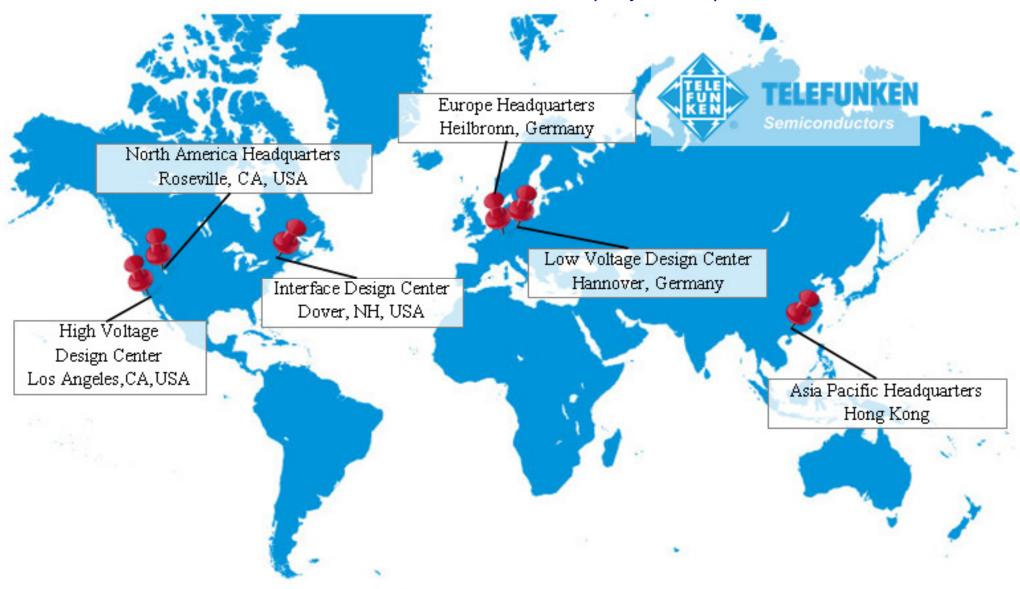

# World-Class Foundry Technologies in Smart-Power, Bipolar, High Voltage, Power MOSFET, IGBT, Embedded Flash, and High Frequency Platforms

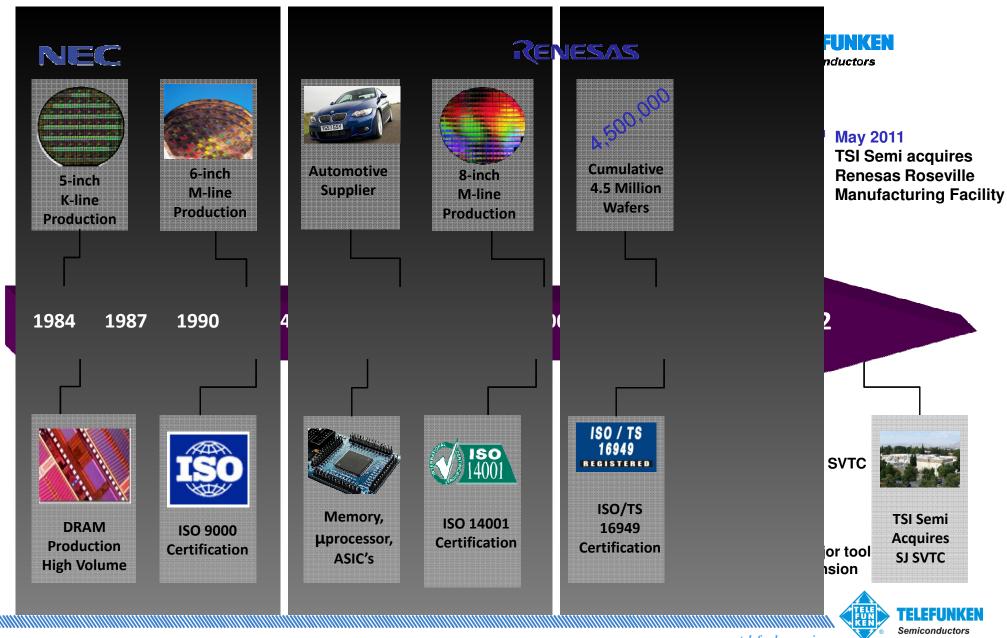

Foundry, Heilbronn, Germany

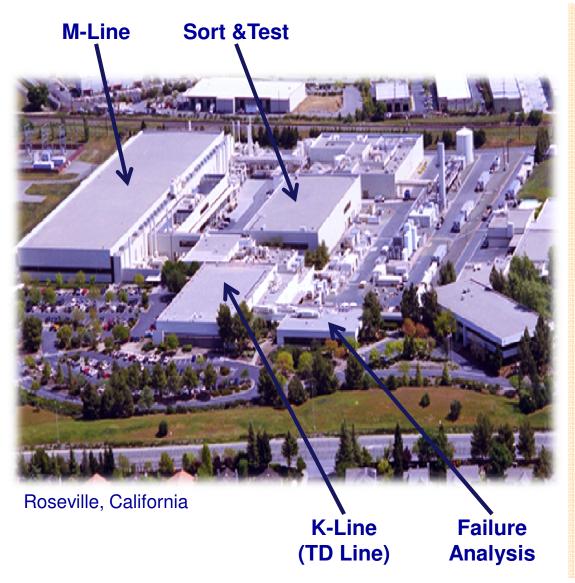

Foundry & <u>TDCS</u>, Roseville, California Corporate Headquarters

TDCS – <u>Technology Development & Commercialization Services</u>

### **Capabilities**

- Production grade tools in Class 3 Clean Rooms

- 84,000 square feet of Fab Clean Room Space

- Engineering Consultants and Program Managers

- 24/7 Engineering, Operations & Maintenance

- Manufacturing Execution Systems (MES)

- IP Secure Environments

- Robust Quality Systems

- Automotive Registered

- Onsite Analytical Tools & Labs

- Process Library

- Novel Materials

- AlSiCu BEOL

- Lithography Capable to 110nm

- Transparent Substrates

- Emerging Technology Capabilities

Provide World Class "More than Moore" Technology

leadership that establishes TDCS as the Premier

Nanotechnology partner from Lab to Commercialization

TDCS provides Technology Development & Commercialization Services in an open and flexible environment.

#### Infrastructure Access

Access to robust infrastructure for development & manufacturing needs

- R&D Wafer Processing

- Tool Hosting/ Clean Room Rental

- Hands on Access

- Tool Access

- Office Facilities

- Process Library

# **Engineering**

Utilize blended pool of engineering services to support development efforts

- **Blended Engineering Pool**

- **Project Management**

- Analytical Services

### **Manufacturing**

Pilot & low volume production or process transfer services to high volume partners

- Custom Process Flows

- Fast Transfer Services

- PDK's for High Voltage, MXS, Analog Devices

### **Value Chain**

Provide total solutions through a network of service and product partners

We create a collaborative relationship with customers to enable the fastest and most cost effective time to market for technology and product commercialization while enabling customer IP independence

Cost-Effective Fast Cycles of **IP** Flexible Capability Solutions Independence Learning **Technology Production** Customer **CAPEX Development Process Grade Tools Retained IP Avoidance Engineering Expertise Variable Cost Development IP Security** & Availability **Environment Processes** Access **Customer Program Support for New** Access to Integrated **Value Chain** Management **Materials** Recipe IP Operational Excellence Multi-disciplinary Engineering **Customer Program Management**

- TSI Semiconductor, TDCS Overview

- Non Volatile Memory Trends

- Solutions for NVM Memory Development

- Process Module Blocks

- Summary

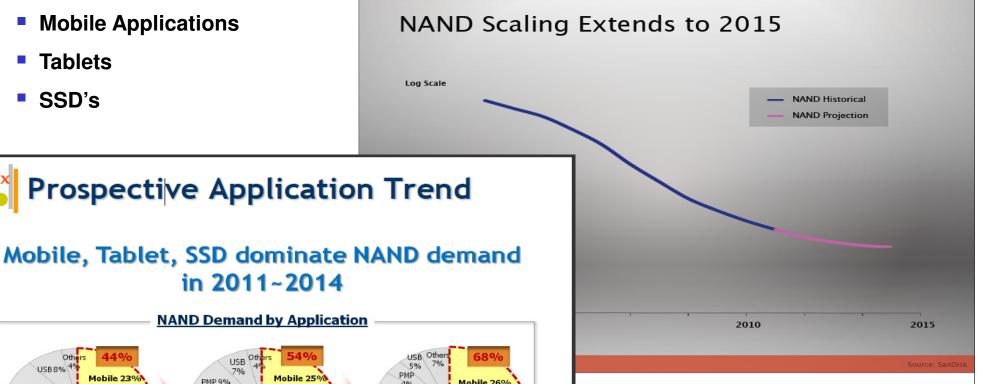

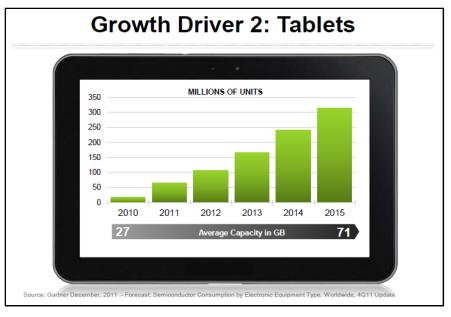

- **Mobile Applications**

- **Tablets**

- SSD's

in 2011~2014 **NAND Demand by Application** Mobile 23% Mobile 26% PMP 13% Flash Card `12 Tablet 10% Tablet 12% Flash Card Tablet 18% Flash Card [Source; Hynix Marketing 2011] Great company NUNIX

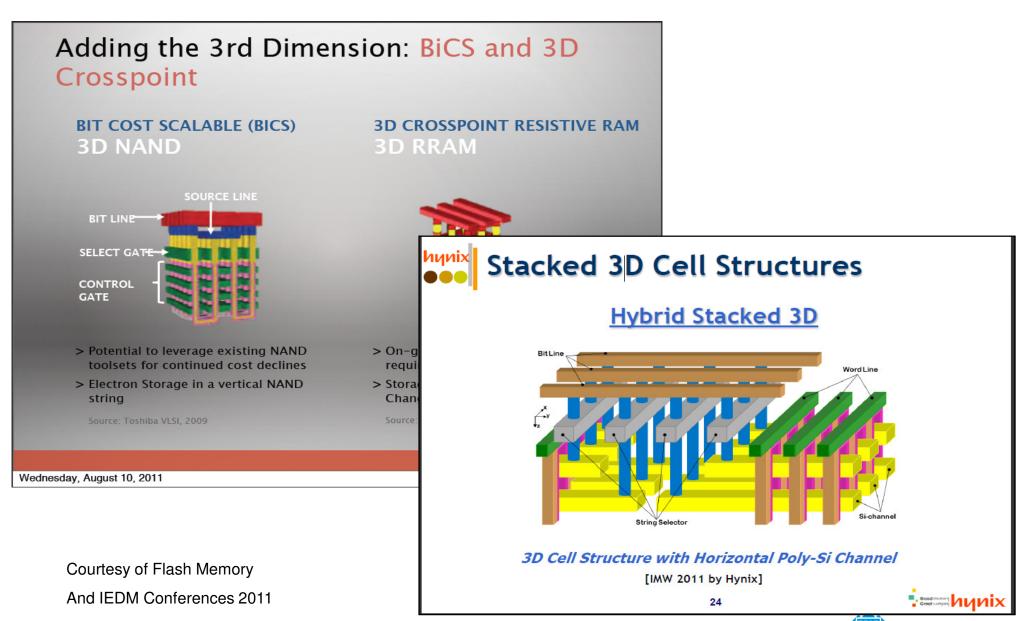

Courtesy of Flash Memory And IEDM Conferences 2011

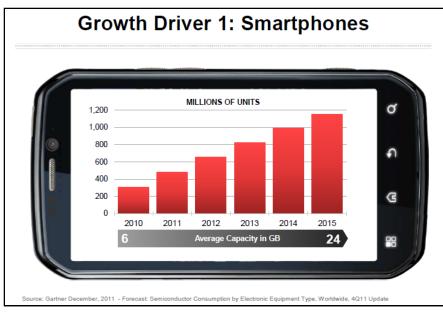

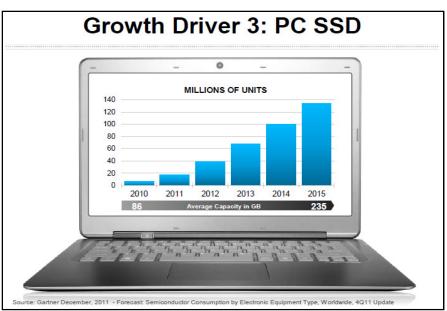

# **Growth Drivers for Memory Technology**

#### SPECIALIZED FOUNDRY SERVICES

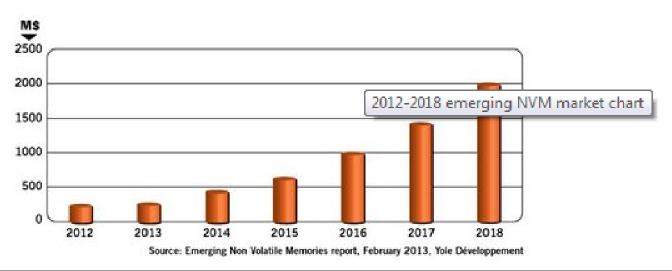

# Yole Développement sees the PCM and MRAM markets reaching \$1.6 billion in 2018

Yole Développement released a new report on Emerging Non-Volatile Memories (which include four major technologies: MRAM, PCM, RRAM and FERAM). They see the market increasing ten-fold in the next five years to \$2 billion by 2018 (of which STT-MRAM and PCM will take the major share of \$1.6 billion) - mostly due to improved scalability and chip density.

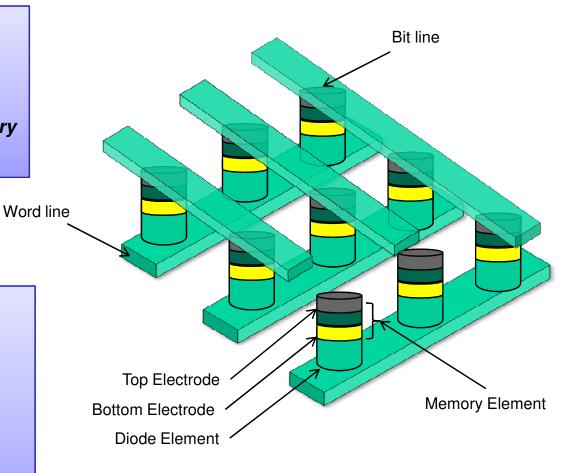

- Cross Point Memory (3D)

- Re-use of Interconnects

- Suitable for 3D Stacking

- Can be Integrated with CMOS circuitry

- Costs

- Cell Size

- Capable of Multi-level

- Performance and Reliability

- Scalability

- Re-use of Fabrication Techniques

- Costs

# **Emerging Memory Development**

| Device Type         | HDD                       | DRAM                   | NAND Flash            | FRAM                   | MRAM                   | STTRAM                 | PCRAM                 | NRAM                    |

|---------------------|---------------------------|------------------------|-----------------------|------------------------|------------------------|------------------------|-----------------------|-------------------------|

| Maturity            | Product                   | Product                | Product               | Product                | Product                | Prototype              | Product               | Prototype               |

| Present Density     | 400Gb/in <sup>2</sup> [7] | 8Gb/chip [9]           | 64Gb/chip [10]        | 128Mb/chip             | 32Mb/chip              | 2Mb/chip               | 512Mb/chip            | NA                      |

| Cell Size (SLC)     | (2/3)F <sup>2</sup>       | 6F <sup>2</sup>        | 4F <sup>2</sup>       | 6F <sup>2</sup>        | 20F <sup>2</sup>       | 4F <sup>2</sup>        | 5F <sup>2</sup>       | 5F <sup>2</sup>         |

| MLC Capability      | No                        | No                     | 4bits/cell            | No                     | 2bits/cell             | 4bits/cell             | 4bits/cell            | No                      |

| Program Energy/bit  | NA                        | 2pJ                    | 10nJ                  | 2pJ                    | 120pJ                  | 0.02pJ                 | لر100م                | 10pJ <sup>[11]</sup>    |

| Access Time (W/R)   | 9.5/8.5ms <sup>[8]</sup>  | 10/10ns                | 200/25us              | 50/75ns                | 12/12ns                | 10/10ns                | 100/20ns              | 10/10ns <sup>[11]</sup> |

| Endurance/Retention | NA                        | 10 <sup>16</sup> /64ms | 10 <sup>5</sup> /10yr | 10 <sup>15</sup> /10yr | 10 <sup>16</sup> /10yr | 10 <sup>16</sup> /10yr | 10 <sup>5</sup> /10yr | 10 <sup>16</sup> /10yr  |

| Device Type         | RRAM                      | CBRAM                  | SEM                   | Polymer                | Molecular              | Racetrack              | Holographic           | Probe                   |

| Maturity            | Research                  | Prototype              | Prototype             | Research               | Research               | Research               | Product               | Prototype               |

| Present Density     | 64Kb/chip                 | 2Mb/chip               | 128Mb/chip            | 128b/chip              | 160Kb/chip             | NA                     | 515Gb/in <sup>2</sup> | 1Tb/in <sup>2</sup>     |

| Cell Size           | 6F <sup>2</sup>           | 6F <sup>2</sup>        | 4F <sup>2</sup>       | 6F <sup>2</sup>        | 6F <sup>2</sup>        | N/A                    | N/A                   | N/A                     |

| MLC Capability      | A                         | A                      | NI-                   | 2bits/cell             | No                     | 12bits/cell            | N/A                   | N/A                     |

|                     | 2bits/cell                | 2bits/cell             | No                    | Zuitsreell             |                        |                        | 1071                  | 777.7                   |

| Program Energy/bit  | 26/ts/cell<br>2pJ         | 2bits/ceii<br>2pJ      | 13pJ                  | NA                     | NA                     | 2pJ                    | N/A                   | 100pJ <sup>[12]</sup>   |

|                     |                           |                        |                       |                        |                        |                        |                       | *****                   |

Kryder, et al. IEEE Transactions on Magnetics, Vol. 45, October 2009

- TSI Semiconductor, TDCS Overview

- Non Volatile Memory Trends

- Solutions for NVM Memory Development

- Process Module Blocks

- Summary

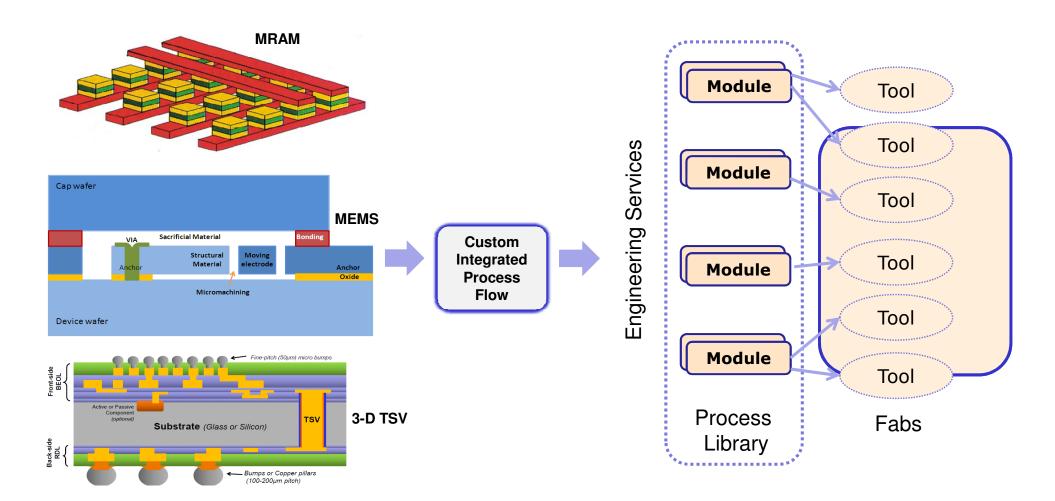

Process library, tool set and engineering expertise enable development of custom integrated process flows for novel silicon based process technologies

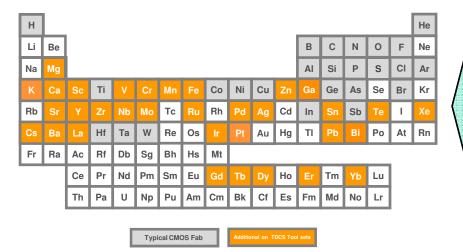

#### **Material Integration**

- DC ,RF & Co-Sputtering

- Metals, Metal Nitrides

- Mag Stack & Anneal

#### **Novel Materials**

- Atomic Layer Deposition

- Metals, Oxides, Nitrides

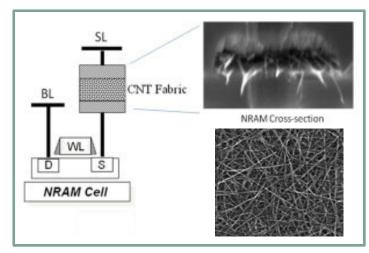

- Carbon Nanotubes

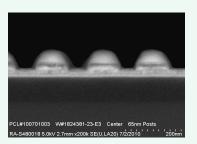

#### Lithography

- 110nm Lithography

- DP Spacer Techniques

- <110nm L/S, 110nm Posts</p>

#### **Novel Etch**

- Nobel Metals

- High Temp:170-350C

- Physical Ion Milling

#### **Low Temp Process**

- <200C Modules</p>

- Nitride, Oxide Films

- Ash & Cleans

#### **CMP**

- Selective Slurries

- Oxide, Tungsten

- Exotic Materials

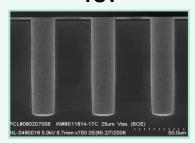

#### **TSV**

- DSiE

- Cu, W, Poly

- Barrier Materials

#### Interconnect

- Foundry CMOS

- Cu & Al interconnect

- Alignment

### **Memory Materials Development**

| Device | Materials                                                              | Process Module's                                                                                   |

|--------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| MRAM   | Co, Fe, B, Ni<br>Ta, Ti, Pt, Mn,<br>Ru, Mg, Ir, Al,<br>Metal Oxides    |                                                                                                    |

| PCRAM  | Ag, GeS2, GST<br>(Ge, Sb, Te)                                          | <ul><li>Low temp processing<br/>(&lt;200C)</li></ul>                                               |

| ReRAM  | Zr, Pr, Ca, Y,<br>Pd, La,<br>Complex Metal<br>Oxides                   | <ul><li>Nobel Etch and Cleans</li><li>AlCu Interconnect</li><li>Interconnect with CMOS</li></ul>   |

| FeRAM  | PZT (Pb, Zr, Ti,<br>O), SBT (Sr, Bi,<br>Ta, O), BLT (Bi,<br>La, Ti, O) | <ul><li>Materials Integration</li><li>CMP</li><li>Hardmask and Liner</li><li>Integration</li></ul> |

| NRAM   | CNT, W                                                                 | Double Patterning                                                                                  |

| SQC    | Nb/AlOx/Nb,<br>TiPt                                                    |                                                                                                    |

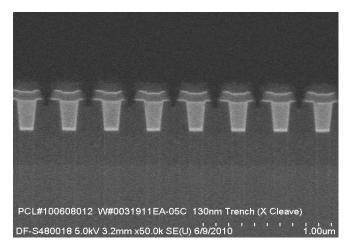

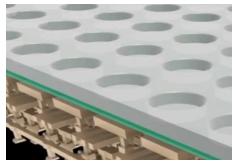

3-D Memory: Courtesy Sandisk

ReRAM Memory: Courtesy Company B

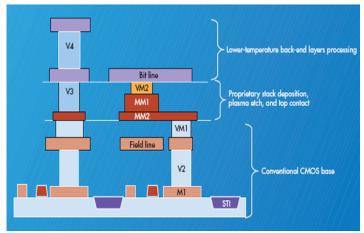

MRAM Memory: Courtesy Crocus

CBRAM Memory: Courtesy Adesto

# Case Example: Key Fabrication Elements

- Integration of CMOS Wafers to Memory

- Etch Integration

- Low Temperature Module Blocks

- Inter-Dielectric Planarity

|                    | Pro                                                                                                              | Con                                                                     |

|--------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Compact Solution   | <ul><li>Increase Chip Density</li><li>Smaller Devices</li></ul>                                                  | <ul> <li>Integration challenges</li> </ul>                              |

| Device Performance | <ul> <li>Less Interconnect</li> <li>Minimize parasitics</li> <li>Improved Device</li> <li>Performance</li> </ul> | <ul> <li>Challenge for devices with<br/>thermal requirements</li> </ul> |

| Cost               | <ul><li>Reduced Assembly</li><li>Reduced Packaging</li><li>Lower Cost of Ownership</li></ul>                     | Potential Yield Mis-match     between devices                           |

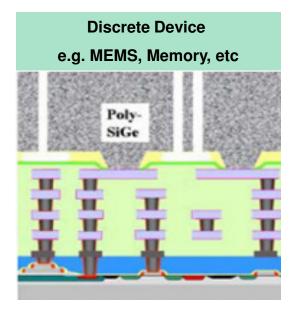

Monolithic integration of Discrete Devices and CMOS

**3-D Memory**: Courtesy Sandisk

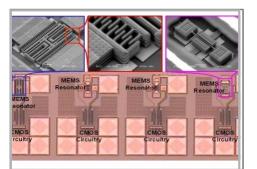

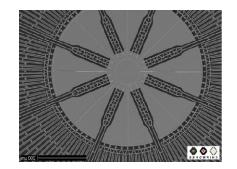

Lab-on-a-chip integrates microfluidics, sensors and logic to more rapidly perform gene sequencing oscillators, filters

MEMS Resonator on CMOS used imicro-Mirrors over CMOS (picture and mixers

RF domain: frequency references for courtesy of Spatial Photonics). Sample applications include Microdisplays

**TELEFUNKEN**

- Integration of CMOS Cu Wafers to Memory

- Etch Integration

- Low Temperature Module Blocks

- Inter-Dielectric Planarity

#### Spin Transfer Technologies raised \$36 million to accelerate its OST-MRAM technology development

Spin Transfer Technologies (STT) announced that they raised \$36 million in series A funding led by parent company, Allied Minds and Invesco Asset Management. STT will use the money to accelerate the development of its patented orthogonal spin transfer magneto resistive random access memory technology (OST-MRAM) - by scaling operation, hiring new employees and purchasing equipment.

#### Toshiba designed an STT-MRAM/SRAM hybrid cache for ultra-low power processors

Toshiba has a new hybrid cache design that uses STT-MRAM and SRAM combination. This is aimed towards next-generation low-power computer processors. These new computers will usually be off, and the time and power it takes to "wake up" is considerable. The new design can reduce the energy consumption by around half - and does not effect processing capacity.

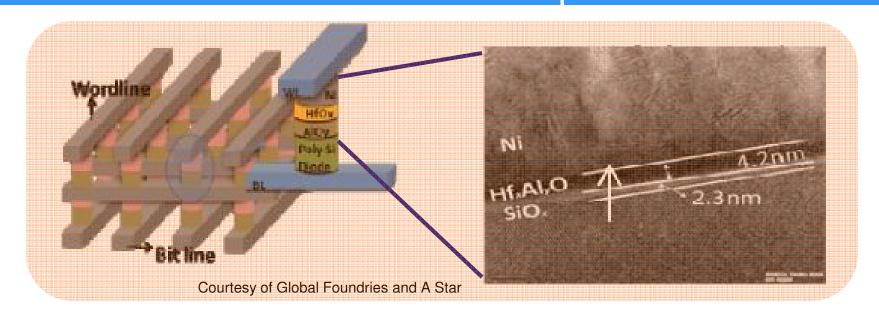

#### Micron and A\*STAR to jointly develop high density STT-MRAM

Micron and the A\*STAR Data Storage Institute (DSI) from Singapore announced that they will jointly develop STT-RAM. The two companies will invest in a 3-year joint-research program to develop high-density STT-MRAM devices.

#### Toshiba and Hynix to co-develop and produce MRAM products

Toshiba and Hynix announced an agreement to jointly develop MRAM products. Once the development is complete, the companies intend to establish an MRAM production plant together. We believe the companies intend to develop STT-MRAM technology.

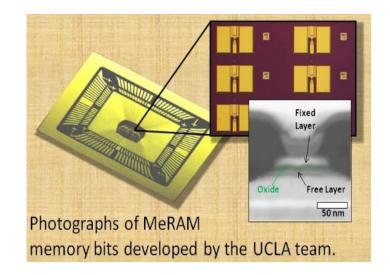

#### UCLA receives \$5.5 million to continue STT-RAM research

UCLA has been awarded \$5.5 million from DARPA to continue develop STT-MRAM technologies. This is the second grant for this project, which brings the total DARPA grants to \$10.5 million. The first stage has been completed a year early than planned - by meeting (and in fact significantly surpassing) speed, energy consumption and stability requirements of their STT-RAM (write times smaller than 5 nanoseconds and write energies lower than 0.25 picojoules per bit).

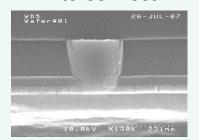

CBRAM Cell

Standard CMOS

Transistors

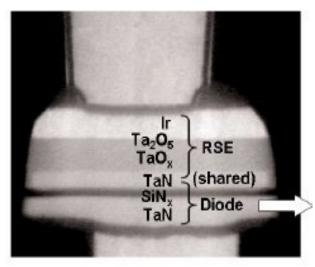

**Panasonic ReRam**

**Adesto CBRAM**

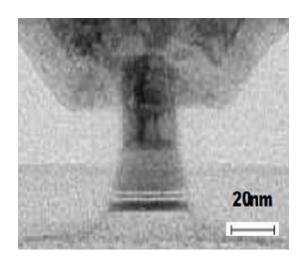

Samsung 17nm MTJ

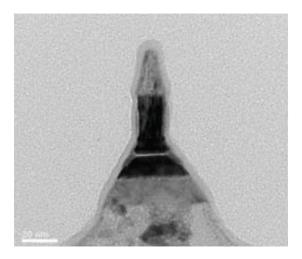

**Nantero NRAM**

**Toshiba MTJ**

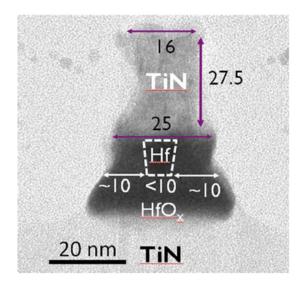

Courtesy of IMEC

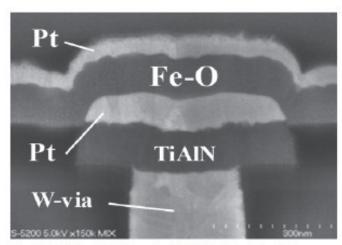

ReRAM Cell Using FeO Variable Resistance Cross-section of the ReRAM memory cell prototyped by Matsushita Electric Industrial. Top and bottom electrodes are Pt.

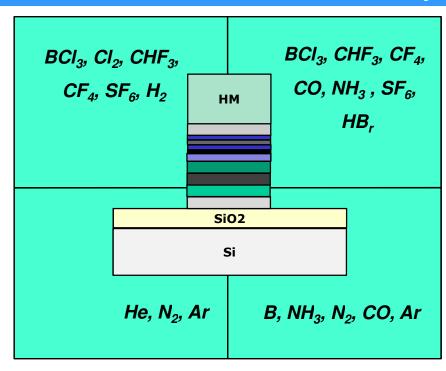

# Large Variation in Materials and Thicknesses, not one Etch Solution that fits all applications

### **Stack Thickness** 500A to 1000A

| Memory | Thickness<br>(A) |  |

|--------|------------------|--|

| Ta     | 100 - 500A       |  |

| CoFeB  | 30A              |  |

| MgO    | 15A              |  |

| Ru     | 10A – 60A        |  |

| CoFe   | 40A              |  |

| PtMn   | 125A             |  |

| GST    | 500A             |  |

| Ag     |                  |  |

| La     |                  |  |

### **Stack Thickness** 1000A to 2.2um

| Life<br>Sciences | Thickness<br>(A) |  |

|------------------|------------------|--|

| Ta               | 50A              |  |

| Ru               | 10A - 20A        |  |

| NiFe             | 20A              |  |

| CoFe             | 475A             |  |

FIG. 46a

FIG. 46b

**Stack Thickness** 1000A to 1.4um

| MEMS<br>Compass | Thickness<br>(A) |

|-----------------|------------------|

| Со              | 500A             |

| CoNi            | 600A             |

| Ni              | 1000A            |

| NiFe            | 500A             |

| Al              | 10kA             |

### **Stack Thickness** 500A to 2.2um

| Other | Thickness<br>(A) |

|-------|------------------|

| Pt    | 1000A            |

| PZT   | Up to 2.2um      |

| Nb    |                  |

Chemical Etch

| Pressure Ranges   |                                     |  |  |

|-------------------|-------------------------------------|--|--|

| Etch Types        | Torr                                |  |  |

| Ion Milling       | 10 <sup>-4</sup> – 10 <sup>-3</sup> |  |  |

| Reactive Ion Etch | 10 <sup>-3</sup> – 10 <sup>-1</sup> |  |  |

| Plasma Etch       | 10 <sup>-1</sup> - 5                |  |  |

**Physical Etch**

<100 mTorr

**Higher Energy**

# **Physical Etch (Sputtering)**

- Physical momentum transfer

- Anisotropic etch profile

- Low etch rate

- Poor selectivity

- Radiation damage possible

# **RIE (Reactive Ion Etch)**

- Physical(ion) and chemical

- Anisotropic, controllable etch profile

- More selective than sputtering

# **Plasma Etching**

- Chemical, thus faster by 10-1000X

- Isotropic etch profile

- High etch rate

- Good selectivity

- Less prone to radiation damage

# **Etching of Novel Materials**

|                     | LAM 9600                                                                      | AMAT DPS2                                                                                             | Tegal 6540                                                                                      | Veeco Ion Mill                 |

|---------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|

| Gases<br>Available  | Chamber A (60C): BCl3,Cl2, Ar, N2, O2,SF6,He,O2 Chamber B (250C): DSQ O2, H20 | Chamber A (250C):<br>BCl3,Cl2, Ar<br>Chamber B (65C):<br>CF4, HeO2,HBr,Cl2                            | HRe 2.1 (30-80C): BCl3, Cl2, CHF3, CF4, Ar, O2 HRe 4.0 (170-350C): CO, Cl2, NH3, CF4, Ar, O2    | Single Chamber: Ar             |

| Materials<br>Etched | AI, TiN/AI/Ti,<br>TiW/TiAI, GST                                               | Chamber A: High-k,<br>Al2O3, TiN, TaN, Ru<br>Chamber B: Metal Gate<br>Stacks - Poly & metal<br>alloys | HRe 2.1: Oxide, Ti, TiN, W, Ta, GST  HRe 4.0: Ti, TiN, Nb, Pt, AlOx,Ta, PtMn, CoFe, MgO, Ru, Ag | Oxide, Ti, TiN, W,<br>Ag, CoFe |

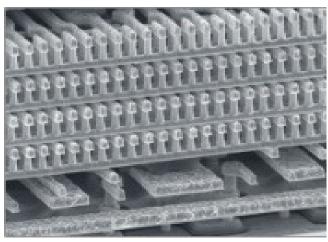

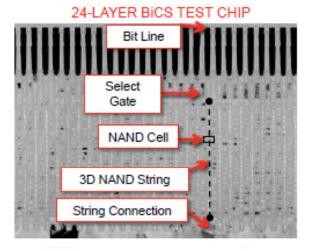

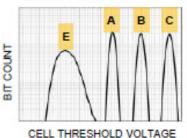

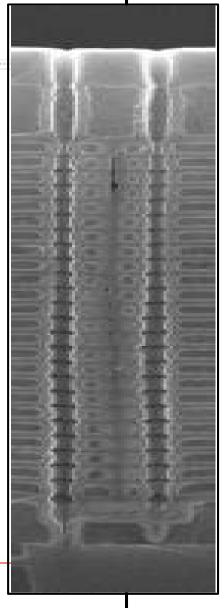

# **Update on BiCS 3D NAND**

- VERTICAL 3D NAND STRING STRUCTURE

- UTILIZES EXISTING WAFER FAB INFRASTRUCTURE

- **DOES NOT NEED EUV**

- KEY DEVELOPMENTS

- 24-layer array development vehicle

- Multi-level cell (MLC) functionality shown

- BRIDGE TO 3D ReRAM

ANALYST DAY || FEBRUARY 16, 2012

- We continue to see innovative and disruptive materials development for next generation NVM technologies

- The challenge for NVM developers is to find a suitable replacement for existing NAND performance for capacity, performance, reliability and costs

- TDCS offers a comprehensive set of capabilities to develop and integrate Novel Memory technologies

- There will be one winner (or more), but it's still in the validation stage!

# **Thank You**

## **Wilbur Catabay**

VP Technology & Engineering TSI Semiconductor, TDCS

7501 Foothills Blvd.

Roseville, CA 95747

Tel: 408-218-9771

www.telefunkensemi.com

wilbur.catabay@telefunkensemi.com