Dual Damascene Etch; Challenges at the 65nm Node and Beyond

> Makarem Hussein Portland Technology Development Intel Corporation email: makarem.hussein@intel.com

### Outline

Integration Scheme

About the "environment"

Selectivity during etch stop layer etch

Conclusions

### Outline

# Integration Scheme About the "environment" Selectivity during etch stop layer etch Conclusions

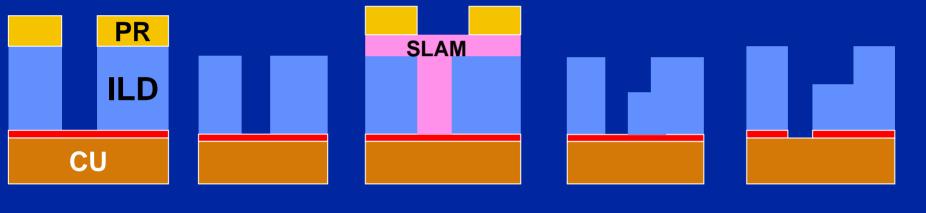

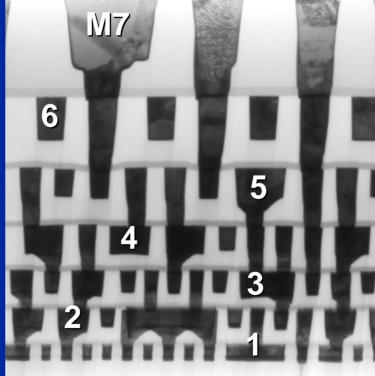

### Via-First Patterning

1. Via Patterning

2. Trench Patterning

3. Etch-stop layer etch

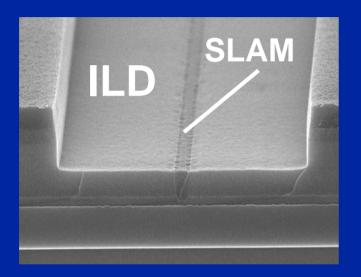

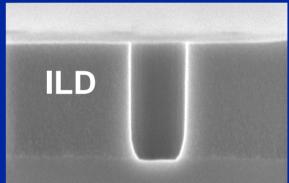

### **Post Trench Etch**

SLAM fills the vias and protect the ESL during trench etch→ No ES selectivity needs

SLAM etch characteristics → Control via profile

### **Role of Etch-Stop**

Copper diffusion barrier

Protect copper during processing

A layer on which via etch terminates

### **Proven Technology**

#### Intel's 130nm Technology

#### Intel's 90nm Technology

### Outline

Integration Scheme

About the "environment"

Selectivity during etch stop layer etch

Conclusions

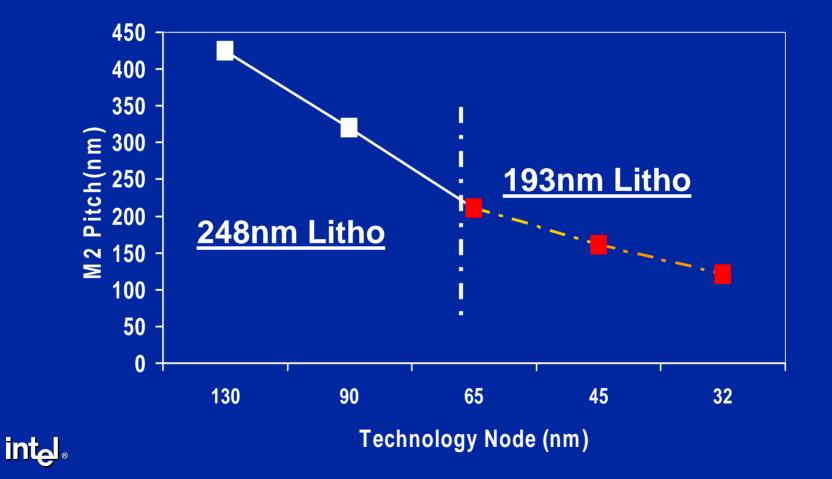

### Always ~30% Smaller

M. Hussein-- Plasma Etch Users Group, 5/13/04

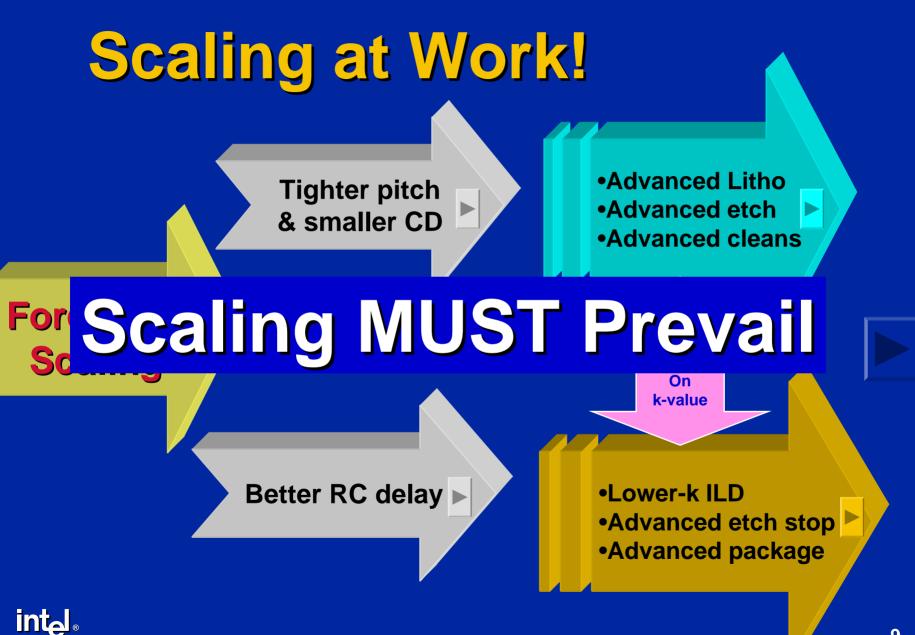

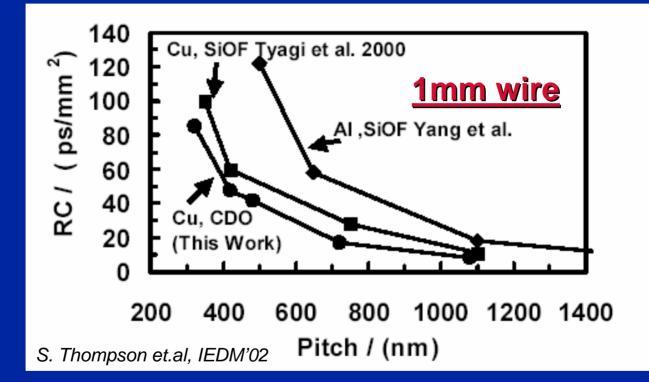

### **Quest for Shorter RC-Delay**

#### Shorter delay → (1) Low resistivity metal (2) Low-k ILD

#### intel

### **Conductor?** Anyone?!

Copper becomes more resistive as metal line width decreases below 200nm

Liner is occupying a "significant" portion of the metal wire area

### What Does Low-k Mean?

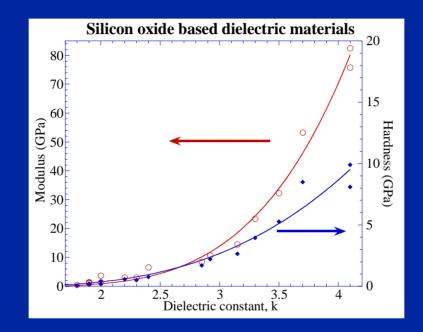

Low-k ILDs possess a lower dielectric constant and weak mechanical properties

Weak mechanical properties

Negatively impact etch and cleans

Limit packaging choices

intal

### **Processing Vs. k- Value** Degradation

• Low-k ILD has a "memory"! • Ashing post via and trench etch: Impacts the out come of the dual damascene patterning >May affect k-value

#### No impact to ILD's k-value adds to etch complexity intal 14

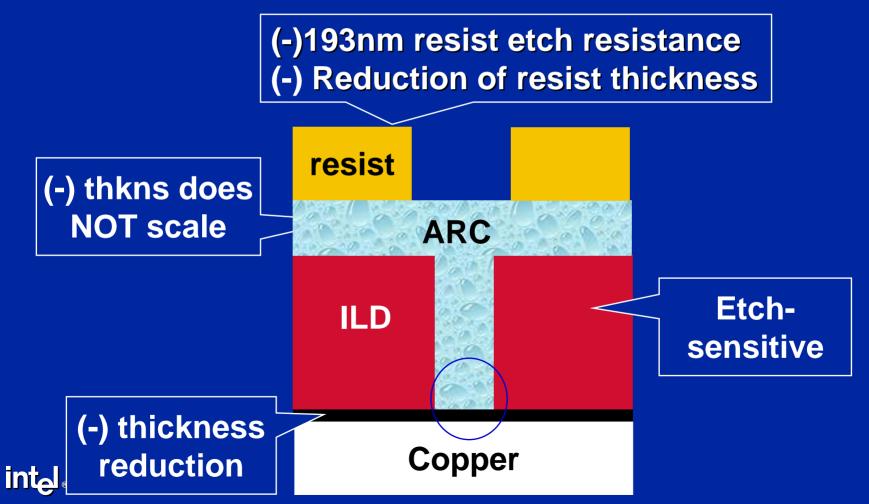

### Harder Patterning with ArF Litho

#### **Before etch**

#### Post trench etch & cleans

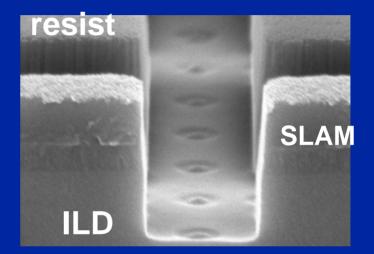

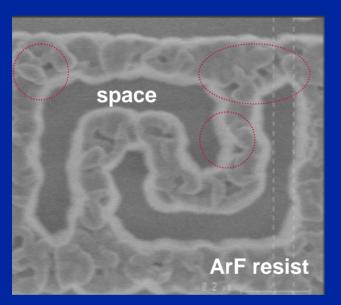

- ArF resist is needed for  $\lambda$ =193nm lithography

- ArF resist "agglomerates" under plasma conditions

- Etch performance of ArF resist is poor

### Harder Patterning with ArF Litho

#### **ArF Patterning**

#### **KrF** Patterning

SAME Via etch process. SAME cleans.

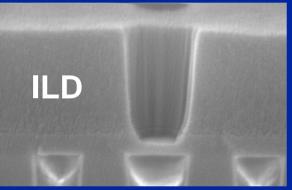

Etching under ArF resist is more susceptible to generating deep striations in the ILD

Balancing selectivity to etch-stop and intel. maintaining profile and CD is getting harder

### **More Challenging Cleans**

Cleans are influenced by:

Nature of the ILD

Dry etch chemistry / strategy

Dealing with low-k ILD and ArF resist significantly complicates the cleans

### Outline

Integration Scheme

About the "environment"

Selectivity during etch stop layer etch

Conclusions

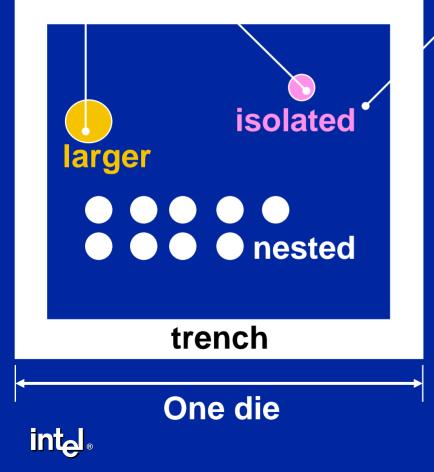

### Have Enough Selectivity?

M. Hussein-- Plasma Etch Users Group, 5/13/04

### **More Selectivity Demands**

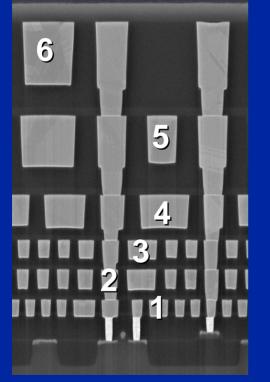

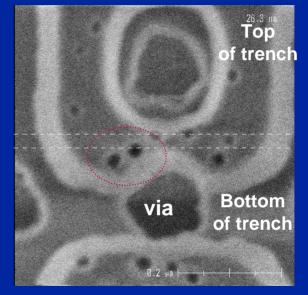

Etch-stop layer (ESL) etch is performed with dual damascene pattern as MASK

Requires etch rate of ESL >> Etch rate of ILD

Minimum to erosion of exposed edges

#### **Experimental Set-up** μ-wave 2.45 GHz Substrate: 300mm Wafer **Undercut** $\alpha =$ SiC etched ILD ESL Plasma **LD:** Low-k, carbon-doped oxide **ESL:** Silicon carbide 400 KHz RF intel 21

## ESL ER: X-section

|               | -  | +   |

|---------------|----|-----|

| CF4 (sccm)    | 50 | 200 |

| CO2 (sccm)    | 0  | 200 |

| Pressure (Pa) | 1  | 3   |

- <u>Design</u>: Three factors, central composite with on-face axial points

- <u>Response</u>: ILD ER, ESL ER, under-cut in ESL

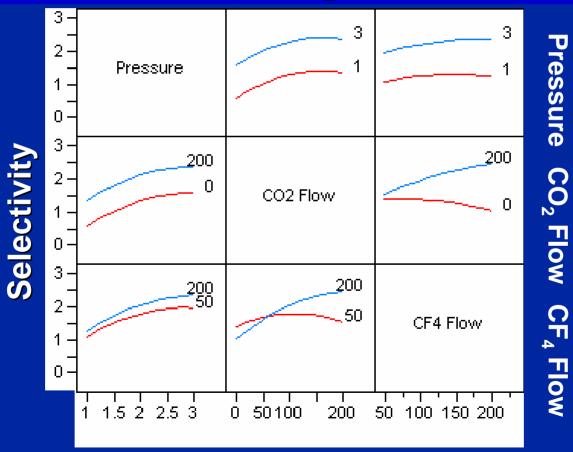

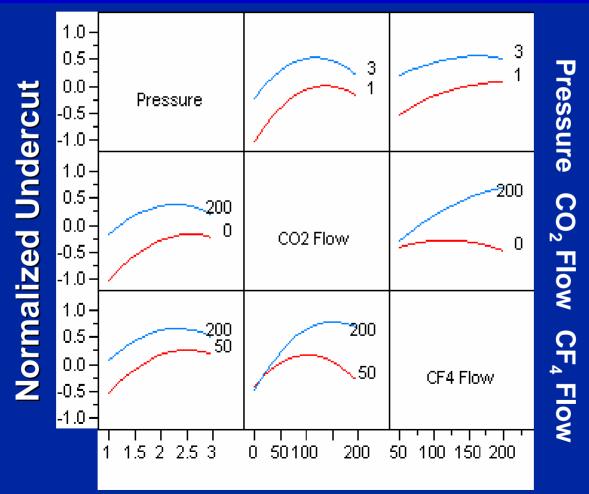

### **Selectivity: Interactions**

High pressure and High CO<sub>2</sub> flow enhance selectivity

intel

M. Hussein-- Plasma Etch Users Group, 5/13/04

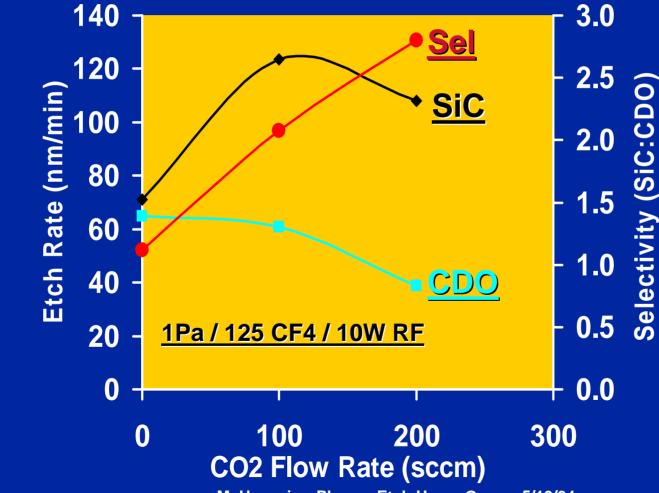

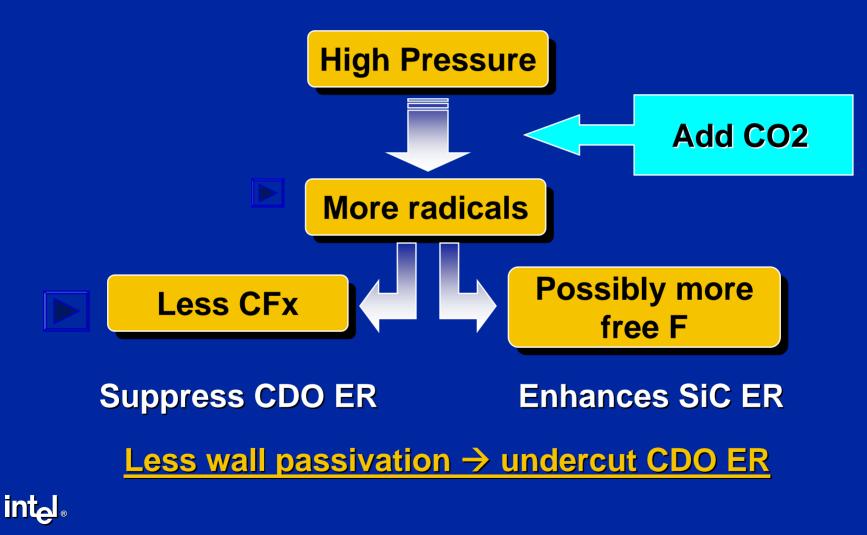

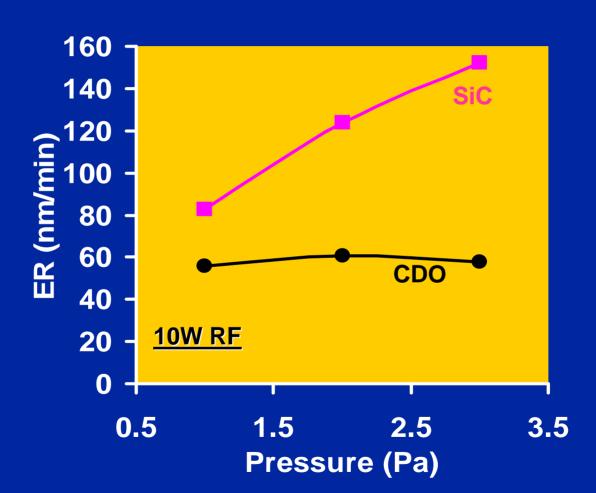

### Effect of CO<sub>2</sub> Addition

SiC ER is more responsive to oxygen addition than CDO

intel

M. Hussein-- Plasma Etch Users Group, 5/13/04

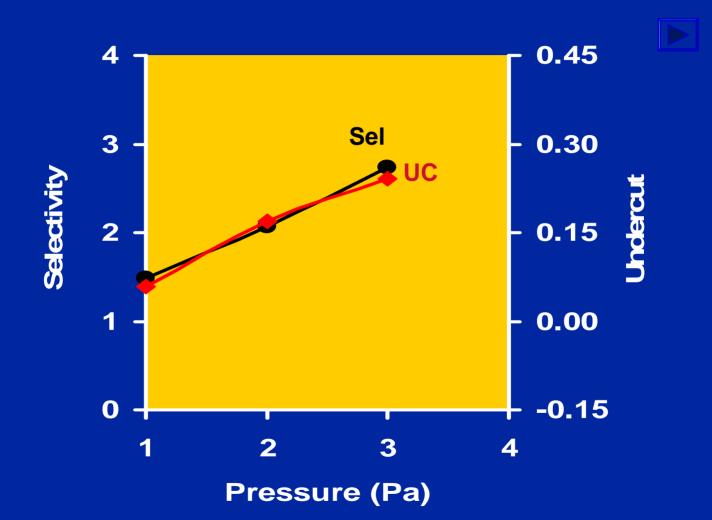

### **Under-Cut: Interactions**

High pressure and CO<sub>2</sub> flow enhance undercut

intal

M. Hussein-- Plasma Etch Users Group, 5/13/04

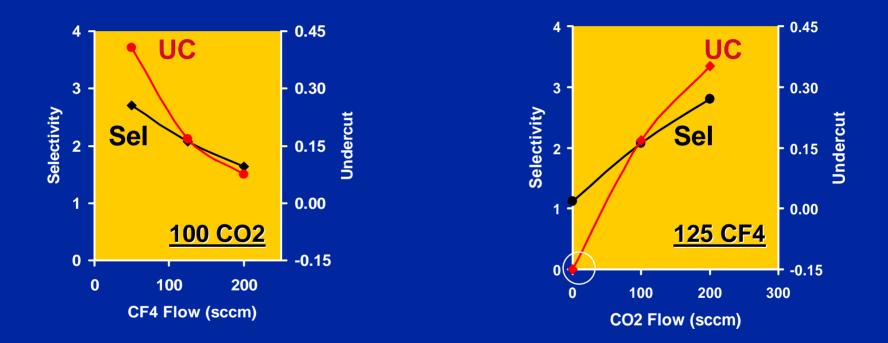

### **General Trends: Flows**

#### Addition of CO2 improves selectivity at the expense Of undercut

#### intel

M. Hussein-- Plasma Etch Users Group, 5/13/04

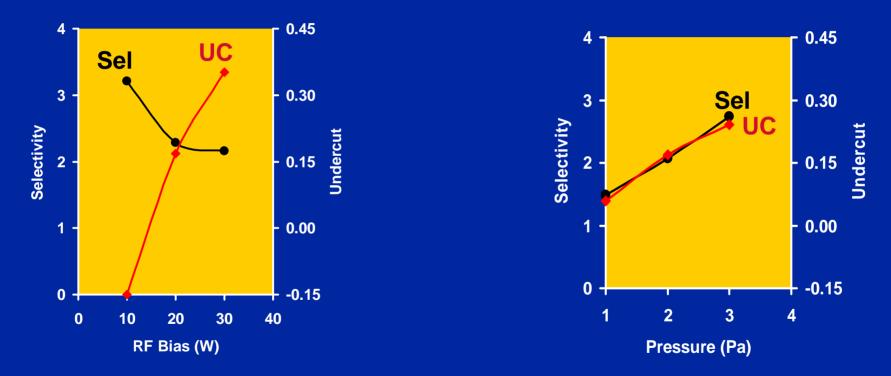

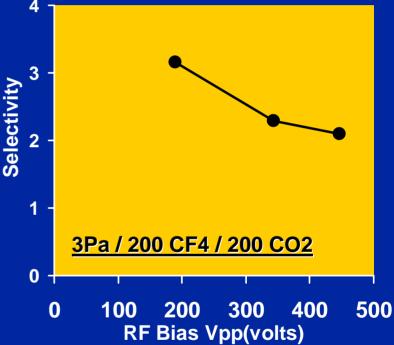

### **General Trends: RF & Pres**

Selectivity improves at higher pressure Undercut increases with RF bias

intel

M. Hussein-- Plasma Etch Users Group, 5/13/04

### Model: Selectivity & UC

### On The Role Of RF...

#### • Observations:

► Undercut increases with RF

- Selectivity degrades with RF

- **ER** increases with RF bias

- No threshold for ER of either SiC or CDO

#### • Conclusions:

SiC etching exhibits appreciable chemical behavior

Passivation, rather than ion bombardment, is the intel. source of anisotropy

### Conclusions

- Scaling will prevail, making patterning more challenging than ever.

- In a downstream high density etch system, it is difficult to attain high selectivity without undercut between CDO ILD and SiC ESL.

- Selectivity is becoming a serious challenge and basic understanding is much needed:

Impact of plasma on ArF resist

Selectivity modulation

### Acknowledgement

- Data and discussions with the following colleagues significantly contributed to this work:

- Dry Etch: Satyarth Suri, Max Heckscher, and James Jeong

- Wet Etch: Lourdes Dominguez, Lana Jong, and Mike Nashner

- Integration: Phucahn Nguyen, and Peter Moon

Quality & Reliability: Jun He and Barbra Miner

intel

M. Hussein-- Plasma Etch Users Group, 5/13/04

intel

M. Hussein-- Plasma Etch Users Group, 5/13/04