## **NOVELLUS**

## Impact of SiOC Low K Materials on Dual **Damascene** Patterning

Gary Ray, Ph.D Director, Integration Novellus Systems, Inc. Lam Research, Inc.

Steve Lassig Sr. Manager, Integration

## The members of the integration organizations of Lam Research, Inc. and Novellus Systems, Inc.

Novellus and Lam Research Confidential

2

### **Presentation Outline**

- > Dual damascene process flow.

- > Dual damascene etch challenges.

- > Photoresist poisoning.

- Trench etch.

- Via etch.

- Trench-over-via etch.

- Barrier open etch.

- ► Summary

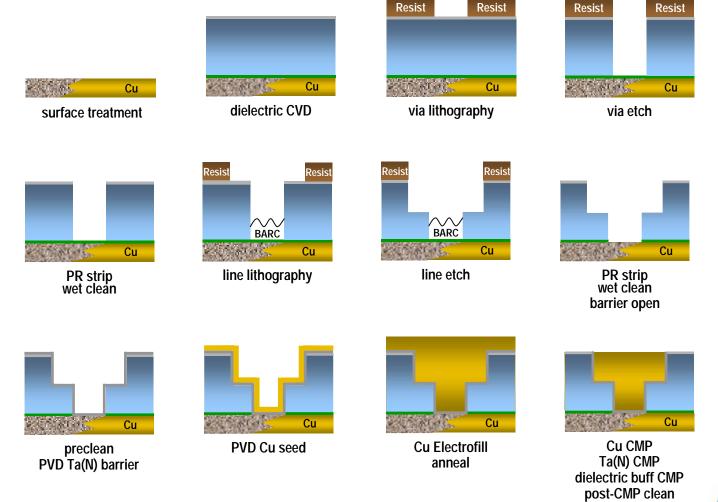

## Dual Damascene Process Flow Via First

NOVELLUS

Novellus and Lam Research Confidential

*2-14-02* **4**

## **Dual Damascene Etch Challenges**

#### **General Dual Damascene Etch Challenges**

- Profile control

- Trench bottom profile

- Striations

NOVELLUS

- Etch selectivity

- Microloading

- No endpoint

- Uniformity

- ► Veils

- Strips selective to dielectrics

- k increase

- **CVD SiOC Low k Film Issues**

- Carbon content

- Chemical reactivity

- Reduced density

- > Amines poison DUV photoresist, preventing development.

- > Amines enter dielectric stacks from a number of sources.

- > The phenomenon has been reported for most classes of low k films.

- > Amines diffuse rapidly in low density low k films.

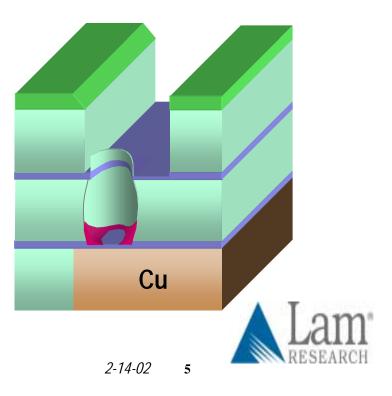

After trench etch.

Cu

X-section view Novellus and Lam Research Confidential

2-14-02

6

- Nitrogen in dielectric deposition processes (N<sub>2</sub>O, NH<sub>3</sub>) is the primary cause of DUV resist poisoning.

- Nitrogen can enter SiOC layers during barrier film predeposition set-up steps and during the actual depositions.

- Etch and strip steps are of secondary importance at best.

10 µm

The source material, as well as the reactor must not inject N<sub>2</sub> into the process chamber.

ILD stack with NH<sub>x</sub> contamination

NH<sub>x</sub> eliminated from stack

Novellus and Lam Research Confidential

2-14-02 7

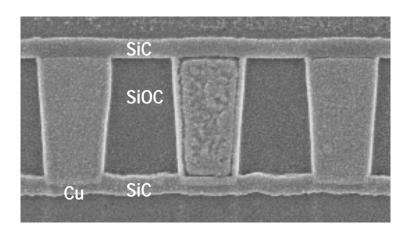

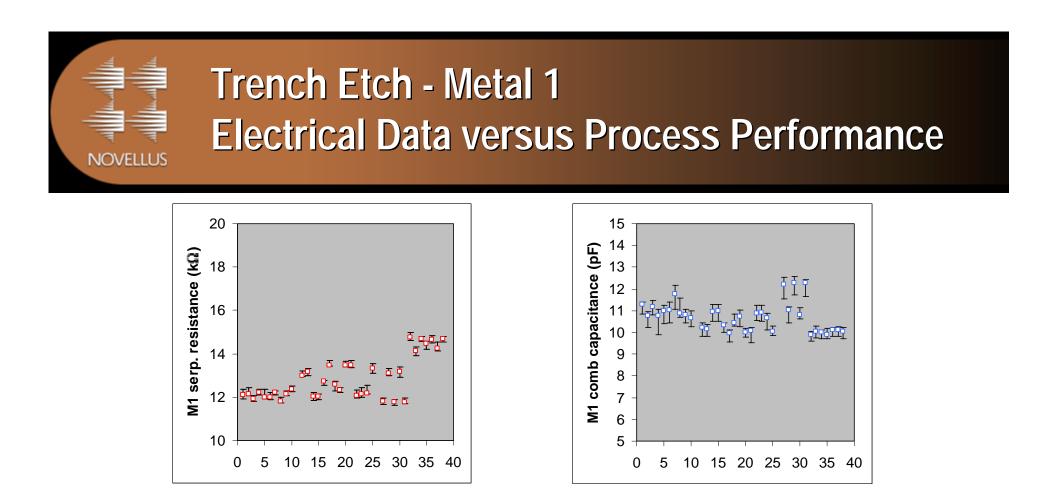

### Metal 1 trench etch is the least demanding process.

- Low aspect ratios.

- Etch stops used.

- M1 Etch Issues

- CD control.

- Profile control.

- Microloading.

- Uniformity.

- Selectivity to barrier film.

#### Followed by barrier open step to expose W plugs.

8

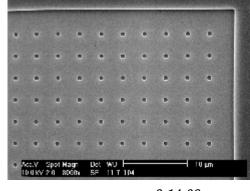

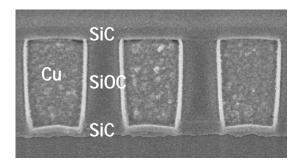

M1 Lines in SiOC low k film.

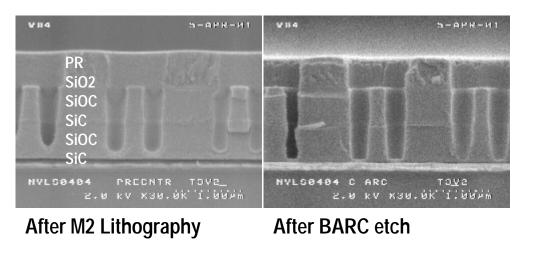

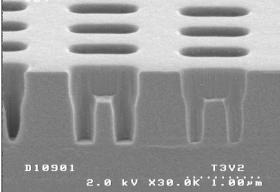

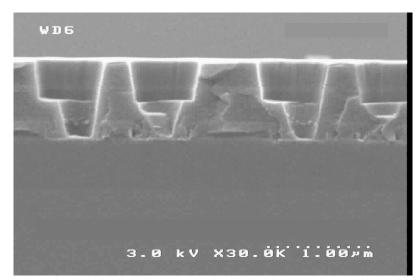

M1 lines in SiOC low k film. Bowing and cusping. Novellus and Lam Research Confidential SiC SiOC SiC

M1 lines in SiOC low k film. Optimized process. 2-14-02 9

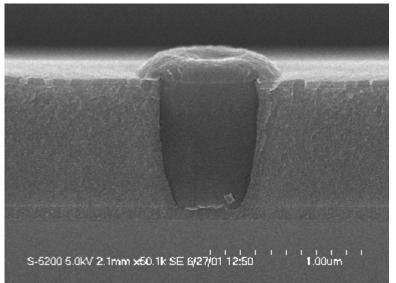

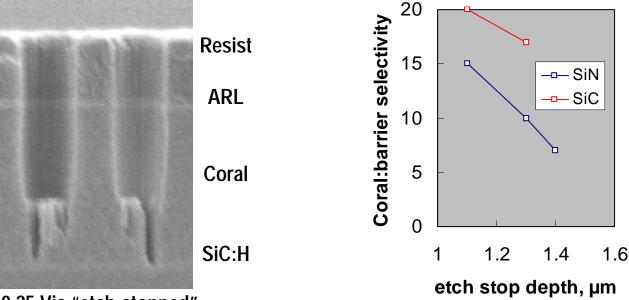

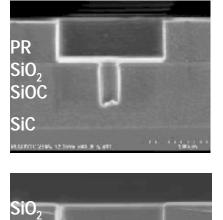

0.25 Via "etch-stopped" at a depth of ~0.6µm

The carbon content of CVD SiOC films can cause "etch stop."

- Attainable etch depth is dependent on etch selectivity.

- Multi-step via etches are often employed.

Independent control of plasma density and ion energy is desirable.

## Via Etch Challenges Chemical Reactivity

- The Si-CH<sub>3</sub> groups in CVD SiOC films are susceptible to attack by fluorine and oxygen atoms.

- Protective polymer thickens toward the via bottoms.

- Overetch process must be optimized for minimal bowing.

ARL 0.25 Via etched to a depth of 1.0µm Coral

Via bowing caused by overetch step.

SiC:H

Resist

Novellus and Lam Research Confidential

*2-14-02* 11

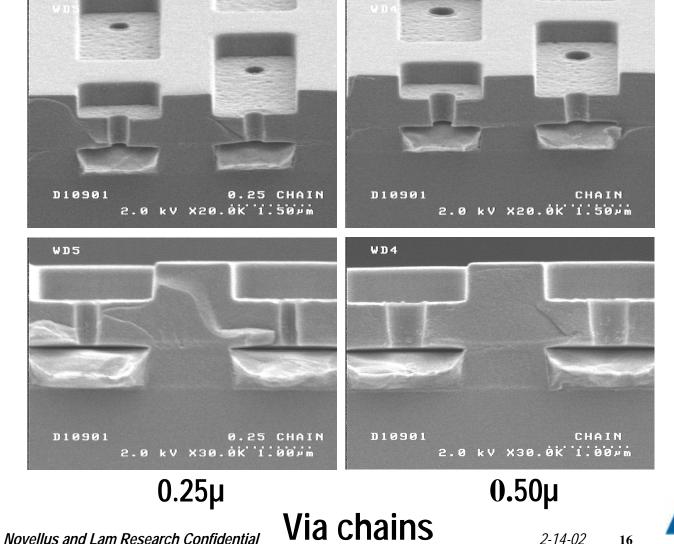

# Trench-over-Via Etch: The most demanding process.

- Many demands must be met simultaneously.

- Trench profile and CD control.

- Smooth trench bottom.

- Protection of barriers in vias.

- ► Via profile maintenance.

- Control of "terracing" and veil formation.

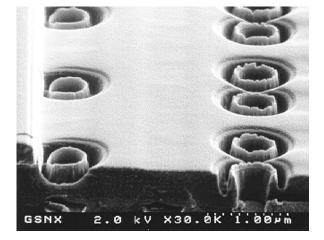

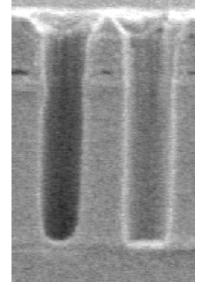

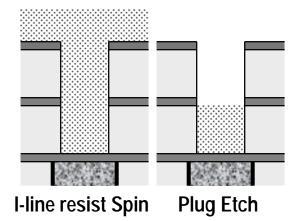

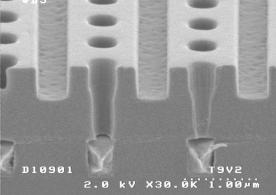

Progression of T/V etch in 0.25µm via chain feature, Resist and I-line plugs have been stripped in-situ.

- Dual damascene processes with oxide or FSG ILDs often rely on spin-on "BARCs" to protect etch stop/diffusion barriers.

- SiOC:barrier selectivity is too low for this scheme to work.

## **Trench-over-Via Etch: Barrier Protection**

- An alternative is to form thick plugs of organic material in the vias.

- Trench etch may be optimized for trench properties rather than selectivity to barrier.

- Via profile can be maintained without etch stop layer.

- Veils and terraces may also be controlled.

- Control of plug height is important.

NOVELLUS

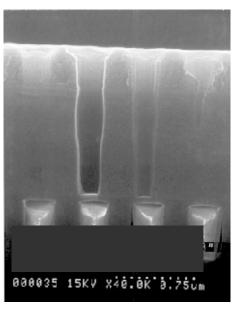

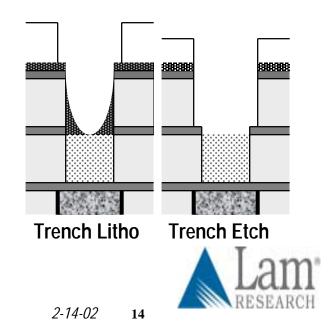

## **Trench-over-Via Etch:** No trench etch stop layer.

- Advanced dual damascene processes do not use etch stop layers.

- Reduced cost.

- Reduced effective k.

- Trench bottom profile and depth control challenging.

- Via profile protection challenging.

NOVELLUS

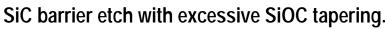

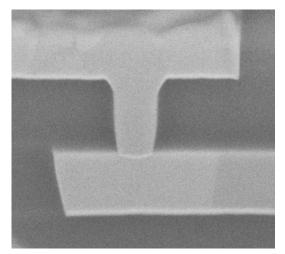

Low density SiOC films sputter more easily.

Novellus and Lam Research Confidential

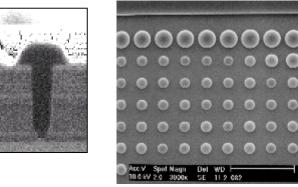

SiN trench stop layer.

1000 Vias in SiOC films taper rapidly during trench etch.

5000A

FSG DD without trench stop layer.

SiOC

SiC

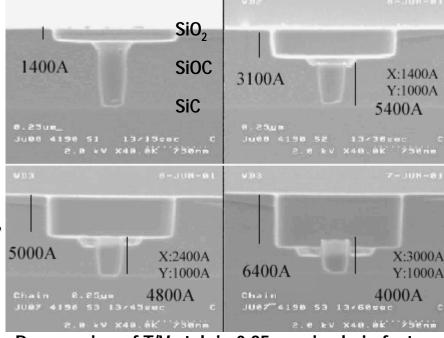

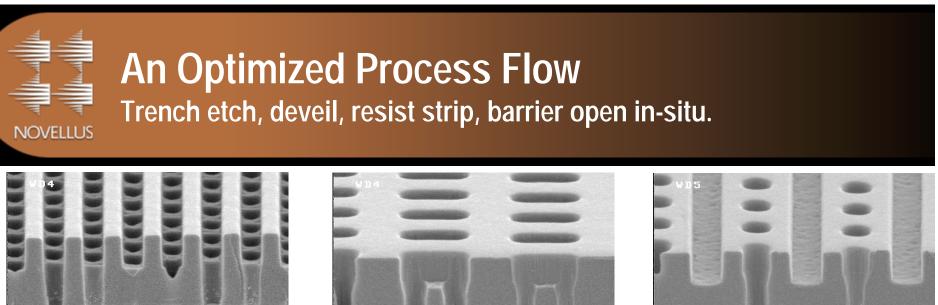

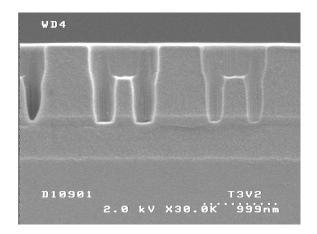

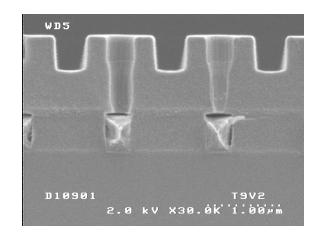

## **An Optimized Process Flow** Trench etch, deveil, resist strip, barrier open in-situ. NOVELLUS

2-14-02 16

D10901 **T2V2** 2.0 kV X30.0K 1.00,m

#### Various trench dimensions over 0.25µ vias

Novellus and Lam Research Confidential

2-14-02 17

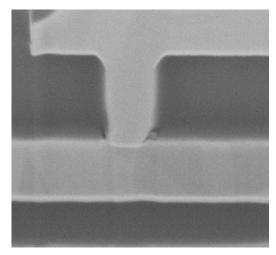

- Seemingly simple etch, however excessive sputter enhanced feature tapering can

- Alter CDs

- Reduce yield

#### ► Isotropic barrier open processes compromise

- Barrier and seed step coverage.

- ECD copper fill.

Directional barrier etch allows good via fill by ECD Cu.

Isotropic barrier etch causes poor barrier/seed step coverage and voids in ECD Cu.

Vias with Cu voids fail during normal thermal cycling.

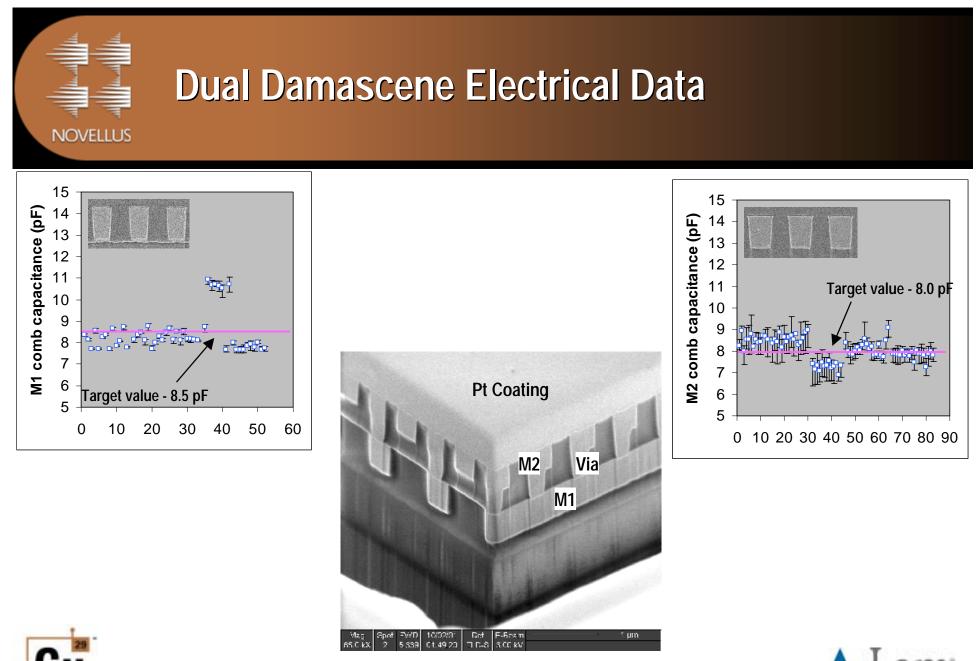

0.25 µm 2-level Metal Structures

- The introduction of the dual damascene architecture eliminated old challenges,

- Aluminum etch

- Dielectric gap fill

- And replaced them with the new dielectric etch challenges that were discussed here.

- > New challenges are here,

- 193nm photoresist

- Thinner barriers

- Porous dielectrics