# NCCAVS Joint Users Group Virtual Meeting "Advanced Packaging Technology" June 10, 2020

# Heterogeneous Integration Roadmap The Revolution Enabling Future Progress

Presented by Bill Bottoms PhD

#### **Technology Roadmapping History**

#### 1991

World's first Open Source Technology Roadmap, the National Technology Roadmap for Semiconductors (NTRS) sponsored by the US Semiconductor Industry Association (SIA).

#### 1998

NTRS expanded forming the first Global Technology Roadmap. Europe, Japan, Taiwan, and Korea joined. It was renamed International Technology Roadmap for Semiconductors (ITRS).

#### 2014

The benefits of Moore's Law scaling diminishing and decision was made to end ITRS.

#### 2016

The last edition of the ITRS was published July 8, 2016

### **Technology Roadmapping History**

In March of 2015, the ITRS Heterogeneous Integration Focus Team signed a Memorandum of Understanding with the IEEE CPMT Society initiating the formation of the Heterogeneous Integration Roadmap.

HIR was founded with initiative from three IEEE Societies (Electronics Packaging Society, Electron Devices Society, Photonics Society) together with SEMI and ASME EPPD.

It is dedicated to embrace innovation wherever it arises and promote collaboration wherever possible to accelerate progress in the microelectronics market landscape.

## Heterogeneous Integration Roadmap Technical Working Groups

#### **HI Market Applications**

- High Performance Computing & Data Center

- Mobile

- Medical, Health & Wearables

- Automotive

- in the Executive Summary

#### **Heterogeneous Integration Components**

- Single Chip and Multi Chip Integration (including Substrates)

- Integrated Photonics

- Integrated Power Electronics

- MEMS & Sensor integration

- 5G RF and Analog Mixed Signal

#### **Cross Cutting topics**

- Materials & Emerging Research Materials

- Emerging Research Devices

- Test

- Supply Chain

- Security

- SiP

- 3D +2D & Interconnect

- WLP (fan in and fan out)

#### Design

- Co-Design

- Simulation Tools & Practice

Use the link below to download the Chapters that interest you.

http://eps.ieee.org/hir

From the same link you will also find information of how you can volunteer to join the effort to produce HIR 2020 which is in process in the fall and will be released in September.

# 54 Years After Moore's Law The World Has Changed...

# CMOS Scaling Is no longer Driving The Pace Of Progress The ITRS Is Over

....the world has evolved and is changing in ways never imagined.

We are entering a period of technology chaos driving new ideas that increase the pace of innovation

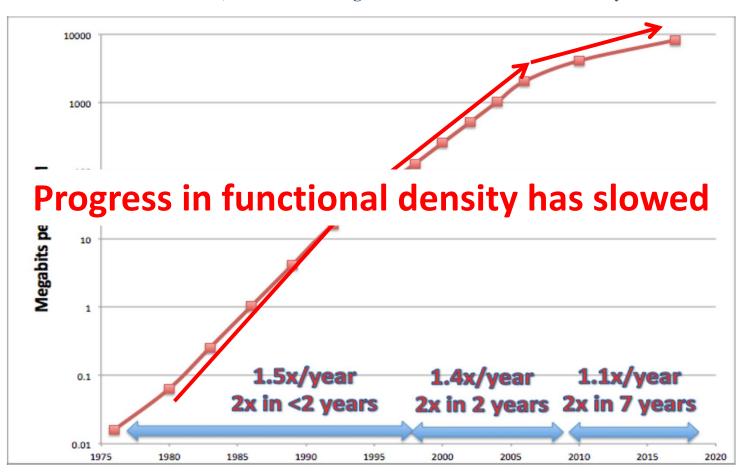

### **40 Year DRAM Memory Capacity Increase**

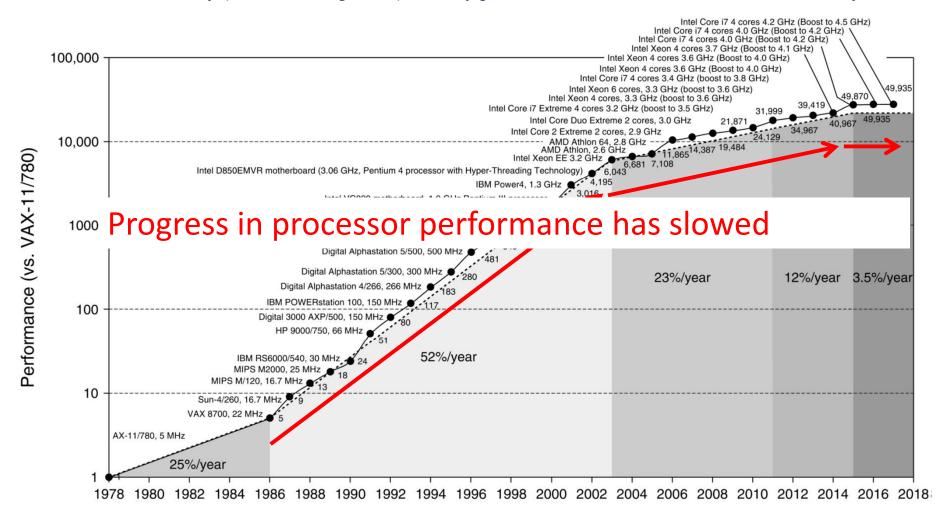

Source: John Hennessy (Chairman Alphabet) Plenary presentation "End of Moore's Law, a New Golden Age" at DARPA ERI Conference July 23 2018

### **40 Years Of Progress In Computing**

Source: John Hennessy (Chairman Alphabet) Plenary presentation at DARPA ERI Conference July 23 2018

# Companies In The Increasingly Connected World World's 10 Largest Companies by Market Capitalization

(Source: The Economist, Statista March 2020)

#### 2006

- Exxon Mobil

- General Electric

- Gazprom

#### 2020

- Microsoft

- Apple

- Amazon

## Structure of the Global Economy has Changed

- Bank of America

- Royal Dutch Shell

- BP

- Petro China

- HSBC

- Facebook

- Tencent

- Berkshire Hathaway

- Visa

- Johnson & Johnson

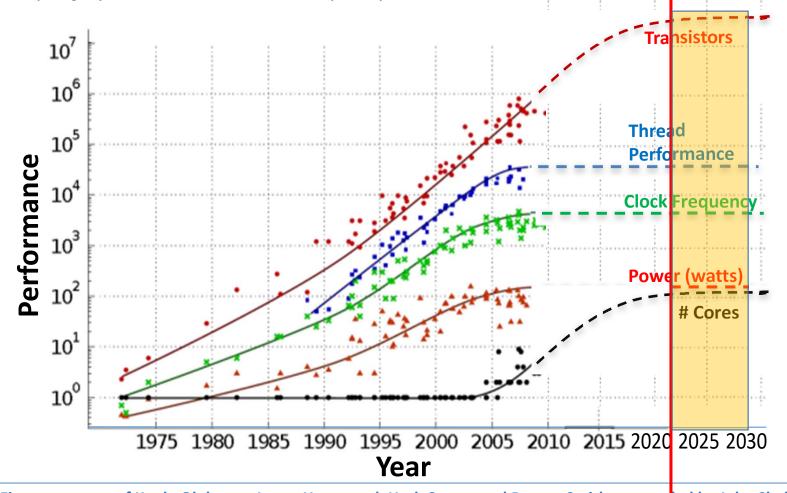

#### Technology Scaling Trends: Exascale in 2021... and then what?

John Shalf (LBNL) "Computing Beyond Moore's Law" International Supercomputer Conference June 18 2019

Figure courtesy of Kunle Olukotun, Lance Hammond, Herb Sutter, and Burton Smith – extended by John Shalf

#### Moore's Law Cannot Maintain the Pace of Progress

#### What happens Next?

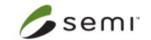

Technology Chaos Drives Innovation Enabling a transition from Evolution to Revolution in Electronics

- Packaging is taking place at wafer and panel level

- Heterogeneous integration by material, circuit type and process

- 3D Systems level integration in a package now in production

### **Opportunities to continue Progress**

Many unproven candidates to maintain progress are yet to be fully implemented Most are disruptive to our current ecosystem.

Source: Partially adopted from LBNL Beyond Moore's Initiative

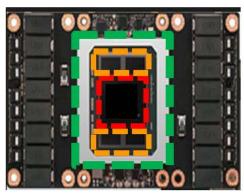

# The leading Edge of Heterogeneous Integration in 2019

#### System Advantages of AMD 2.5D Heterogeneous Integration

Advantages of AMD 2.3D ficter ogeneous integration

- 16 nm

- DDR: 484 GB/s

- 12 nm

- HBM2: 900 GB/s

- Advanced node ASIC

- High Bandwidth memory stacks

- Advantages of Smaller size, lower power, and higher bandwidth

### Apple Watch Series 2: S2 SiP

#### In Production

- WLCSP, FCCSP, QFN and passives in SiP

- PVD based FML2 compartment shield

- 98-layer substrate, 340µm thick

- 35-40µm vias

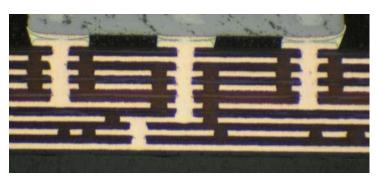

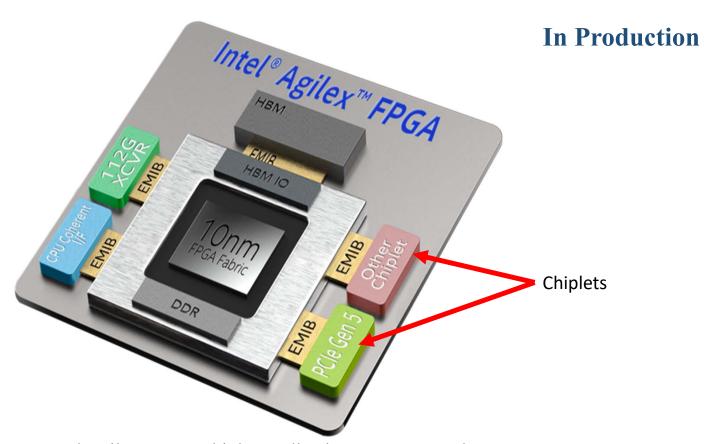

#### Intel's Embedded Multi-die Interconnect Bridge

+ chiplets

Intel Agilex FPGA Chiplet application. Source: Intel

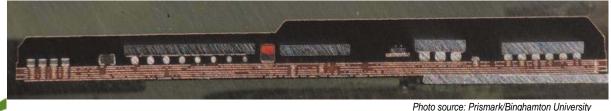

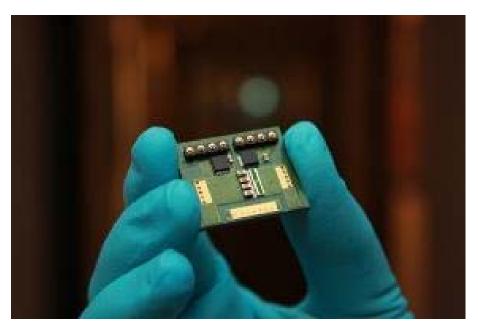

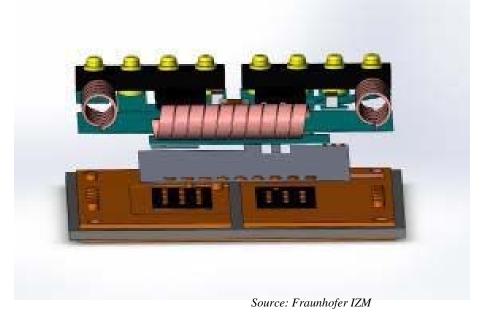

### **Embedded Half-Wave Bridge Module**

EMI-optimized SiP SiC Module

Chapter 8 (Single Chip and Multichip Packaging)

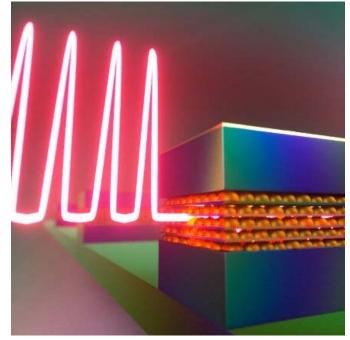

### **Quantum Dot Lasers**

#### **Advantages**

- Better temperature stability

- Can be deposited on Si with MBE

- More power efficient than conventional junction lasers

- Compatible with CMOS processing

- Wide operating temperature range

A quantum dot laser is a mode-locked laser which can passively generate ultrashort pulses less than one picosecond in duration

Credit: Peter Allen

S. A. Kazazis et al, Optical properties of InGaN thin films in the entire composition range, *Journal of Applied Physics* (2018)

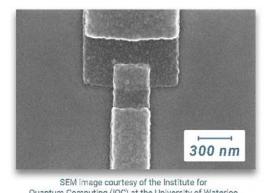

### The Quantum Computer

# Thin Film Deposited Al/Al<sub>2</sub>O<sub>x</sub>/Al Josephson Junction Aluminum Oxide Aluminum Substrate

# Qubits in a computer

The materials are common but Qubits are extremely sensitive to contaminants and special processes are required.

Operating temperatures are near absolute zero bringing new challenges for thermal management.

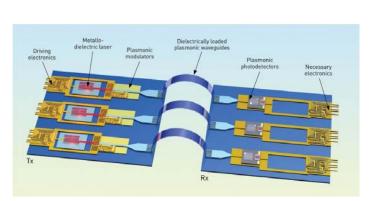

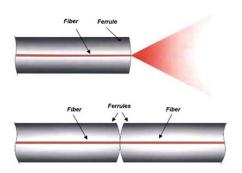

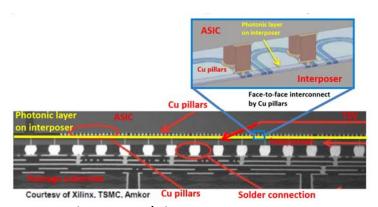

# Many New Devices are Coming Addressing Difficult Challenges for Integrated Photonics

Plasmonic Laser W. Zhu et al. NIST *Science Advances* (2017)

Plasmonic Communication J. Leuthold et al. *Optics & Photonics News*(2013), pp. 28-35.

Low-loss Photonic Connectors

Quantum Dot Laser S. Chen et al. Vol. 25, No. 5 | 6 Mar 2017 | OPTICS EXPRESS 4632

Electronic/Photonic Interposer

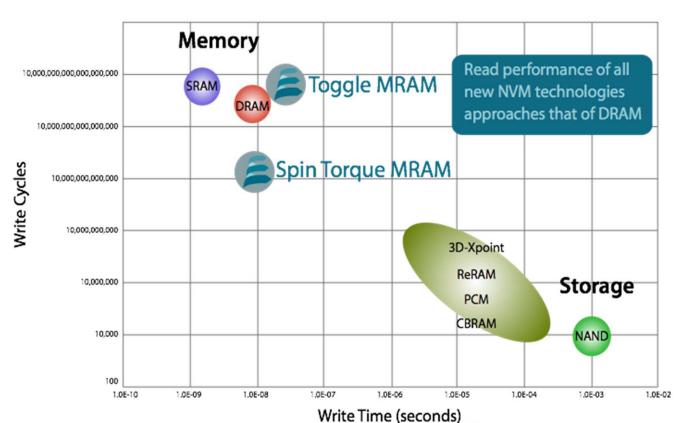

#### Heterogeneous Integration in Photonic/Electronic Systems

#### Components that will be assembled into complex 3D-SiPs may include:

- Monolithic photonic ICs (incorporating photonics, electronics and plasmonics)

- Other discrete optical components that are not integrated in the Silicon/photonic integrated circuits (SiPh-ICs).

- Si based logic and memory ICs

- MEMS devices

- LEDs, MicroLEDs and other optical emitters

- Plasmonic Components

- Sensors (including a growing list of photonic sensors)

- GaN power controller circuits

- RF circuits

- Compound (direct bandgap) semiconductor lasers

- Optical interconnects to and from the outside world

- Electrical interconnects to and from the outside world

- Passive components (including integrated passive devices)

- New devices and new materials that will be invented over the next 15 years

Many have unique thermal, electrical, mechanical characteristics that will require specialized materials and system integration (packaging) processes and equipment

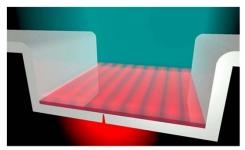

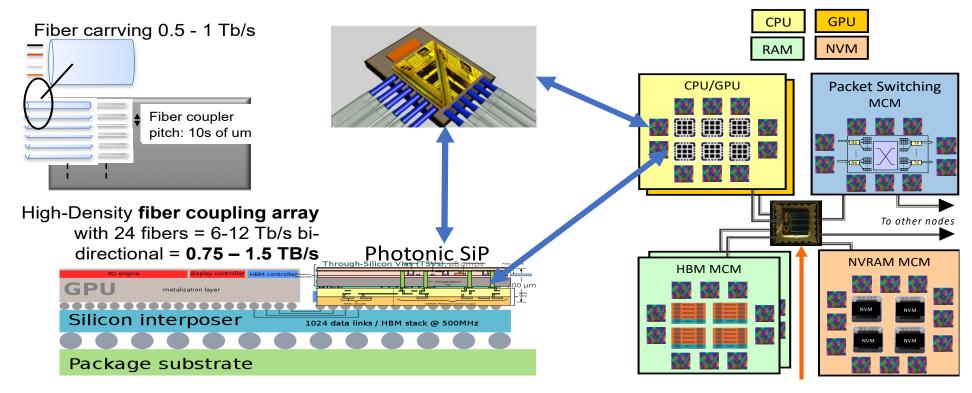

### Silicon Photonics Co-Package Integration

Si Photonics Integration Concept. Source: John Shalf (LBNL) [10]

Chapter 9 (Integrated Photonics)

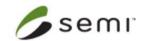

Thermal Management Reaching Limits of

**Imagination**

Source: Raytheon Avi Bar-Cohen

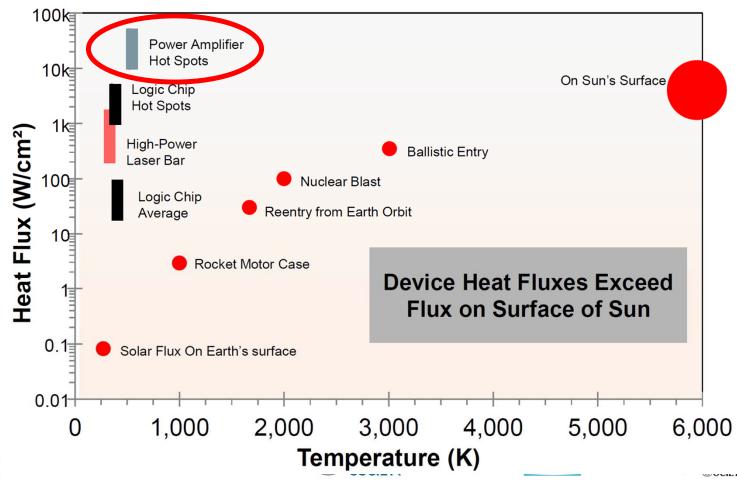

### Diamond Microchannel Bonded to GaN Amplifier

GaN-on-Diamond with diamond microchannels and wafer-bonded Si microchannel liquid manifold

Source: Raytheon Avi Bar-Cohen

## New Components We Can Imagine Today

Integrated Photonics for quantum Info processing Harvard Jan 2019

Photonic Devices for nanoelectromechanical metamaterials on-chip acoustic at 10s MHx Cal Tech Jan 2019

From HIR 2019 Chapter 16 Figure 1

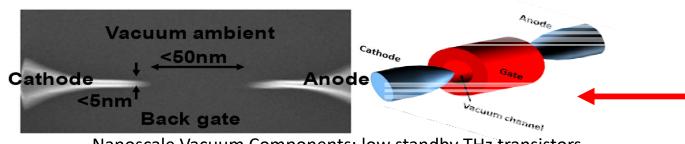

Nanoscale Vacuum Components; low standby THz transistors

NASA Ames 2018

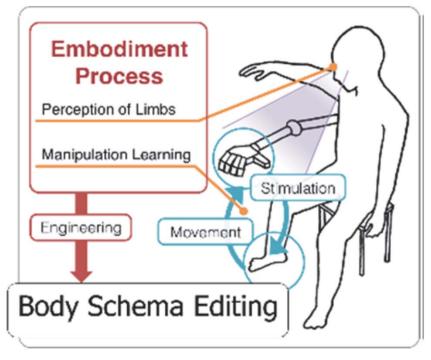

### Robots are Coming and they will be Intelligent Today they are even developing a personality

"Meta-Limbs" – a system that allows us to control extra limbs.

The Concept of Body Schema Editing

Source: Tokyo University

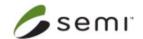

# **Emerging Fast Non-Volatile Memory Chapter 2, Fig 6**

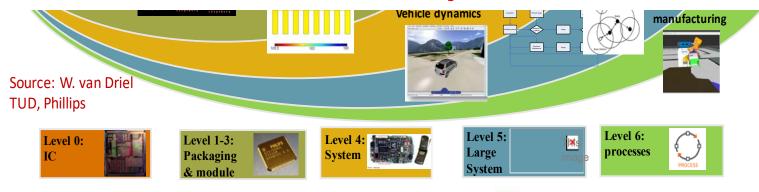

## Where SiP is Heading

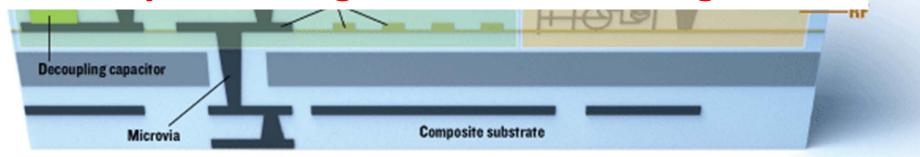

**Chapter 3 Figure 15**

Full 3D System Integration at the Package Level

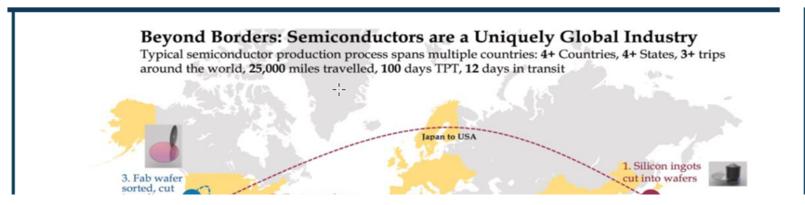

#### We are a Uniquely Global Industry Chapter 6 Figure 11-1

### **Global Supply Chain is in Place and Expanding**

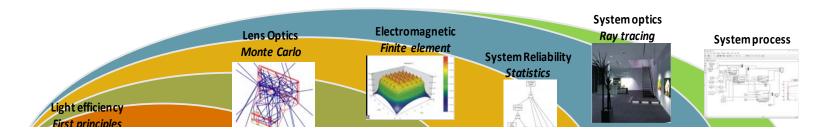

# Modeling & Simulation Including Photonics Chapter 14 Figure 3

# Modeling & Simulation Complexity Increases as HI is adopted

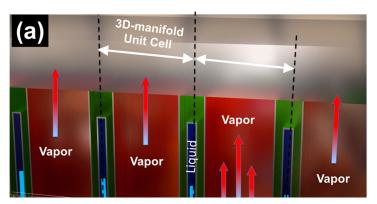

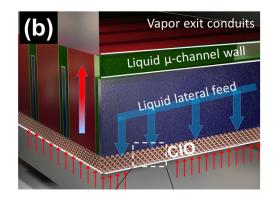

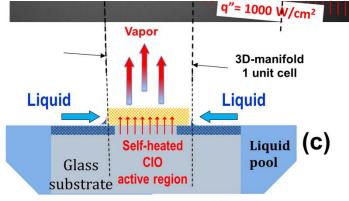

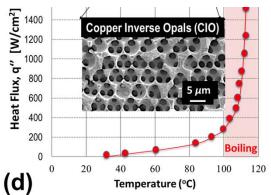

# Proposed Cost Effective Extreme Heat Flux μ-Cooler Chapter 20 Figure 22

### 3D manifold bonded to Si for Heat Flux >1 kW/cm<sup>2</sup>

#### What's Next?

The HIR has established a Webinar Series with presentation from each of our 2019 Roadmap Chapters. These Webinars provide the opportunity for a live discussion with the HIR Chapter Chairs.

We are following the pattern of ITRS with even numbered years providing an update and odd numbered years will be a full rewrite.

The 2020 edition is in process today and it will focus on cross-collaboration of the technical working groups to address overlap and gaps as well as addressing major new developments that have occurred since the initial HIR publication in 2019.

You are invited to join the effort for the 2020 Chapter and the information about how to start is located at <a href="http://eps.ieee.org/hir">http://eps.ieee.org/hir</a>.

# Thank you for your kind attention

Use the link below to download your personal copy of HIR Chapters <a href="http://eps.ieee.org/hir">http://eps.ieee.org/hir</a>