## Low Temperature Plasma Technologies for Advanced Packaging Applications

NCCAVS - Northern California Chapter AVS Joint User Group Meeting (CMP, PAG, & TFUG)

**David Lishan**

June 12, 2018

Plasma-Therm Confidential ©2017 All Rights Reserved

## Outline

**Plasma-Therm Introduction**

Deep Silicon Etching / TSV

Low Temperature Strip / Clean

**TSV Isolation and Seed Layer**

**Surface Activation**

**Plasma Dicing**

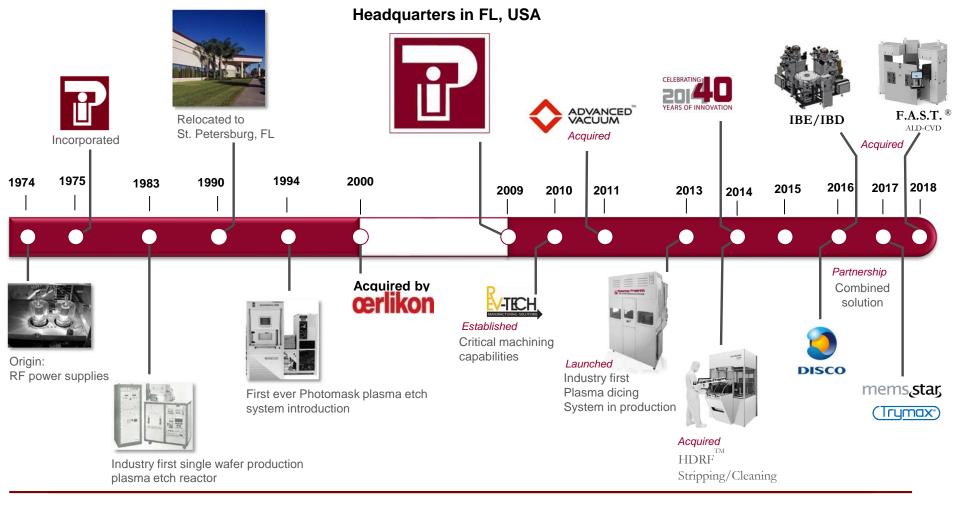

## Plasma-Therm Semiconductor equipment manufacturer

## Etch and Deposition Solutions Lab-to-Fab

#### **DEEP SILICON ETCHING / TSV**

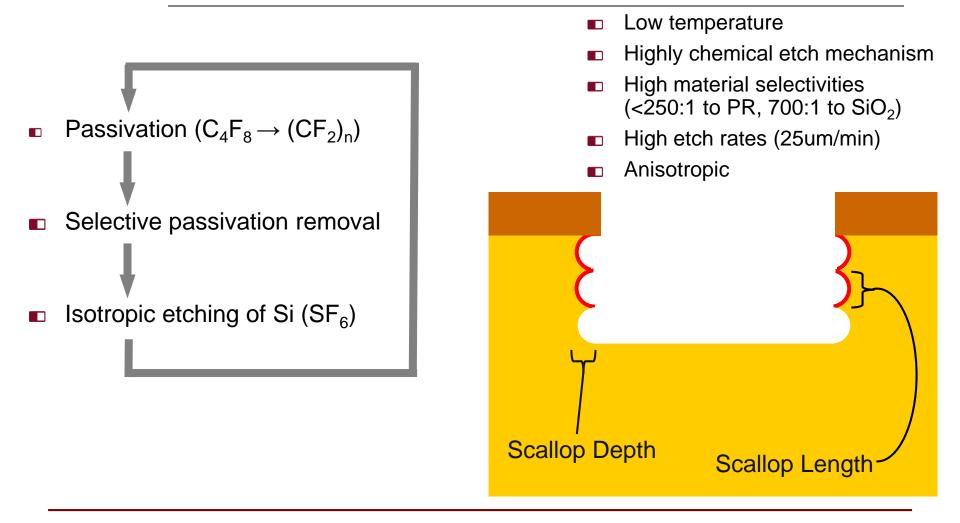

## DRIE – Deep Reactive Ion Etching

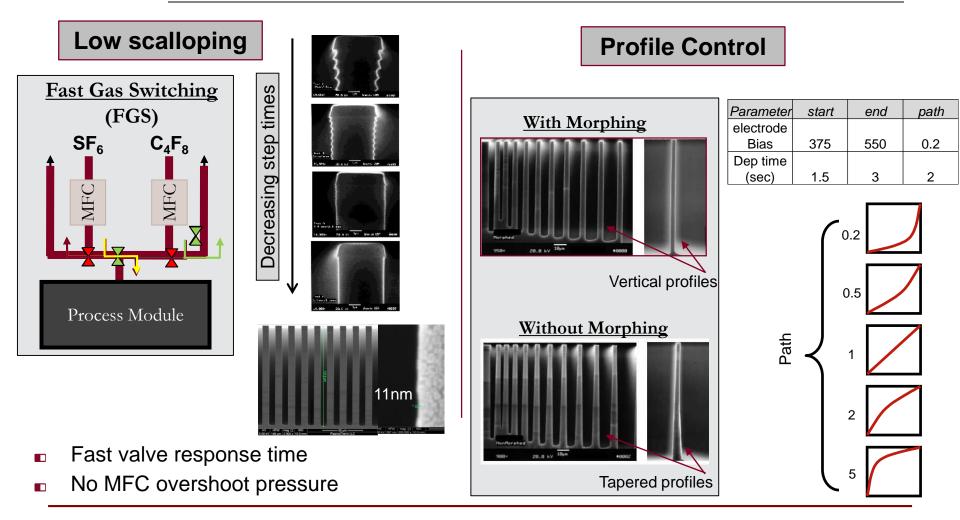

## DRIE – High F Radical Concentrations Fast Process Steps and Process Control

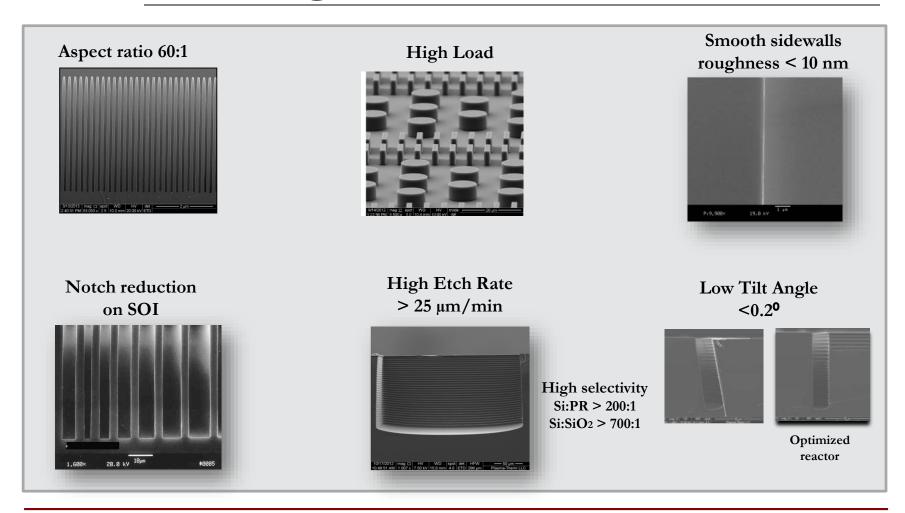

## DRIE Wide range of etch capabilities

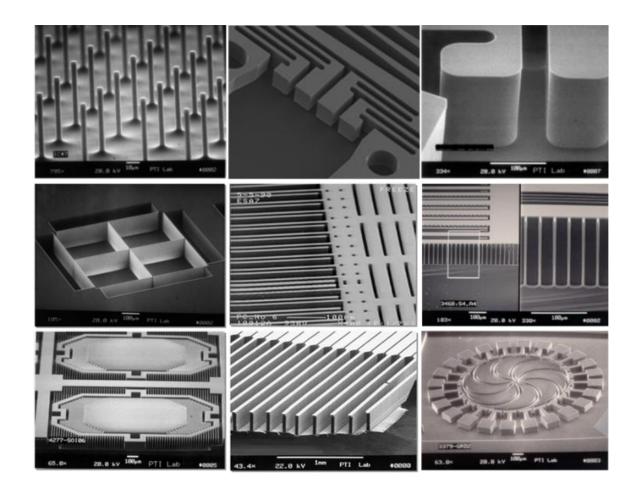

## DRIE Wide range of applications

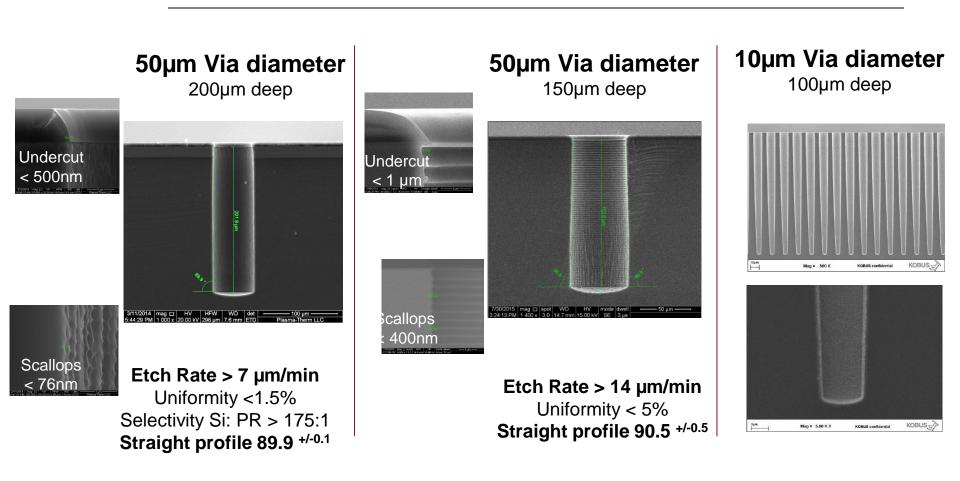

## DRIE – TSV Applications

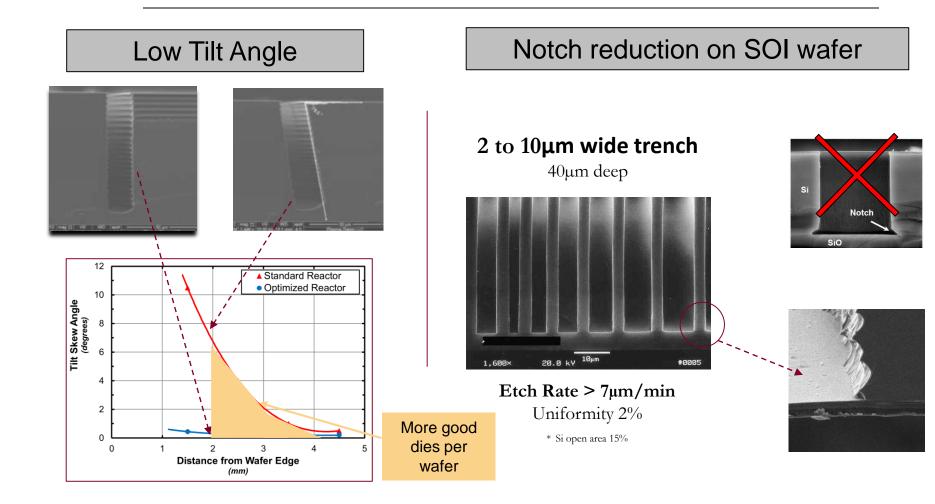

## Low Tilt & SOI Applications

#### LOW TEMPERATURE STRIP / CLEAN

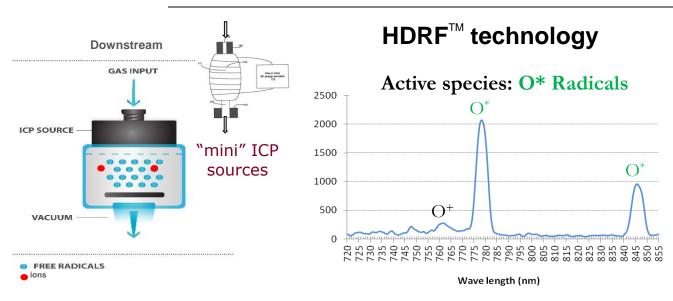

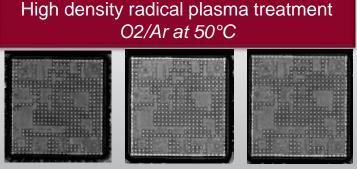

## Plasma-Therm: HDRF<sup>TM</sup> High Density Radical Flux

#### **Conventional RF**

#### High plasma density ICP source

- Radicals density > 1E17 cm<sup>-3</sup>

- Mainly O\* radicals at wafer level

#### Low damage on sensitive devices

- Low ions at wafer level

- $\square$  Low temperature processing < 80°C

#### 🖬 Plasma-Therm

Active species: O<sup>\*</sup> + lons

lons = damage, heating

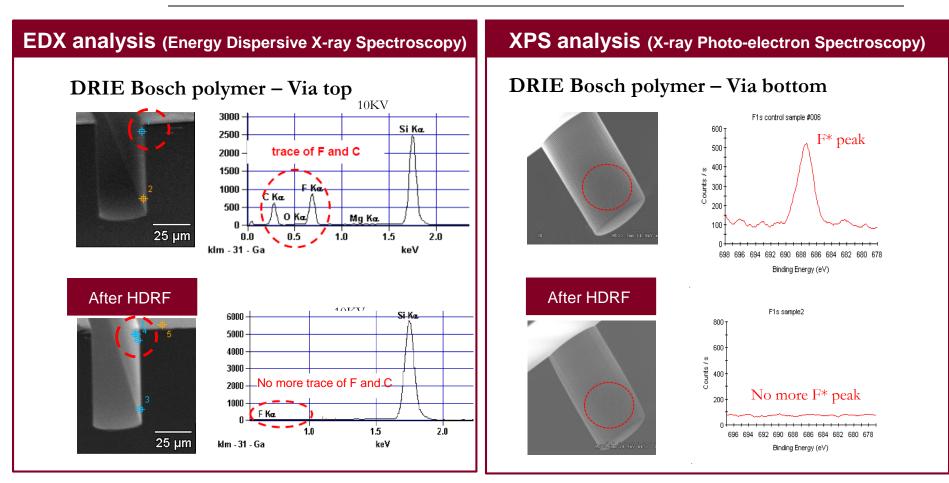

## DRIE polymer removal

Efficient dry cleaning technology, to remove fluor-carbon polymers

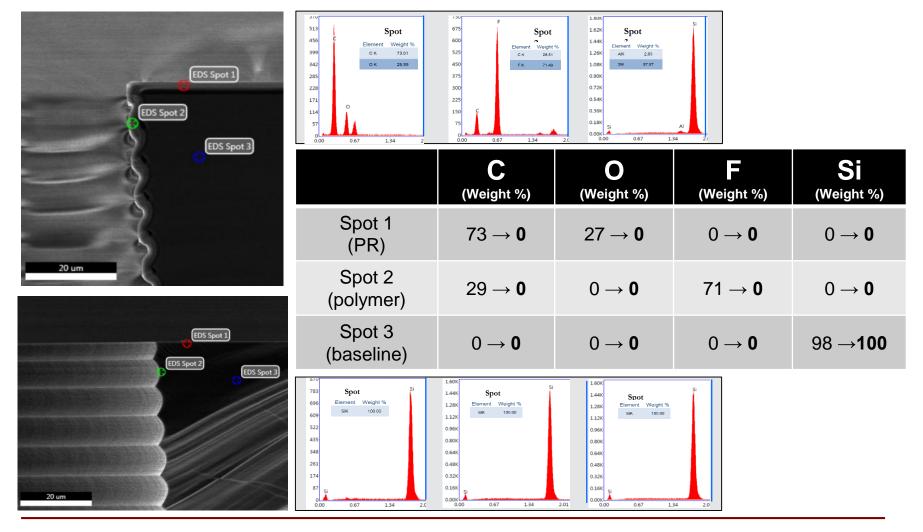

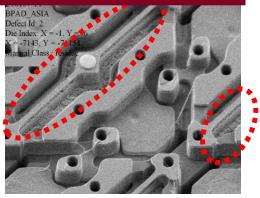

## PR & Polymer removal SEM and EDAX Pre → Post measurement

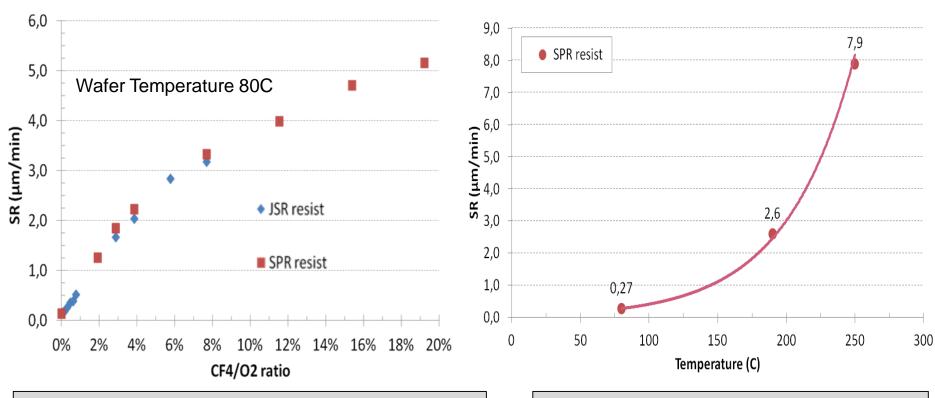

## Low-temperature PR (and polymer) strip

Low temperature HDRF process For temperature sensitive applications

Higher strip rate with increasing temperature

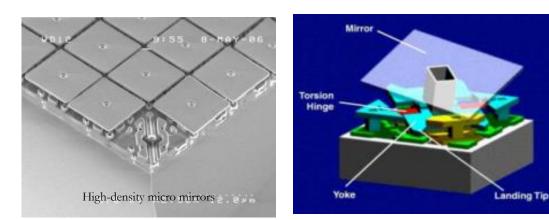

## Micro Mirrors Cleaning

- Elimination of mirror tilt due to residues

- Damage-free. No electrical charging

- Yield improvement

#### Wet treatment

With plasma treatment

#### **TSV ISOLATION and SEED LAYER**

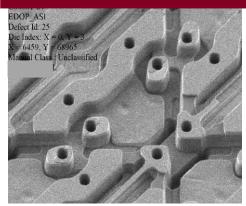

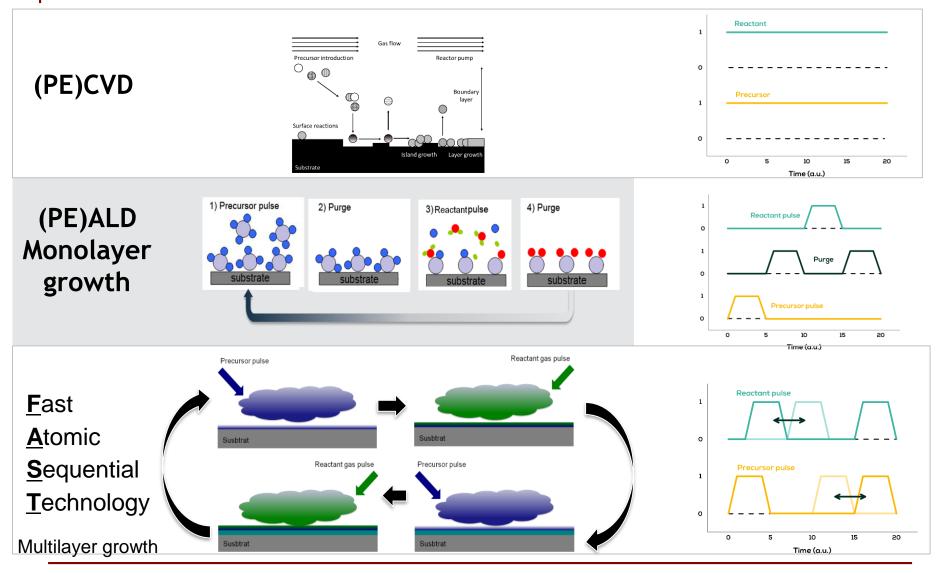

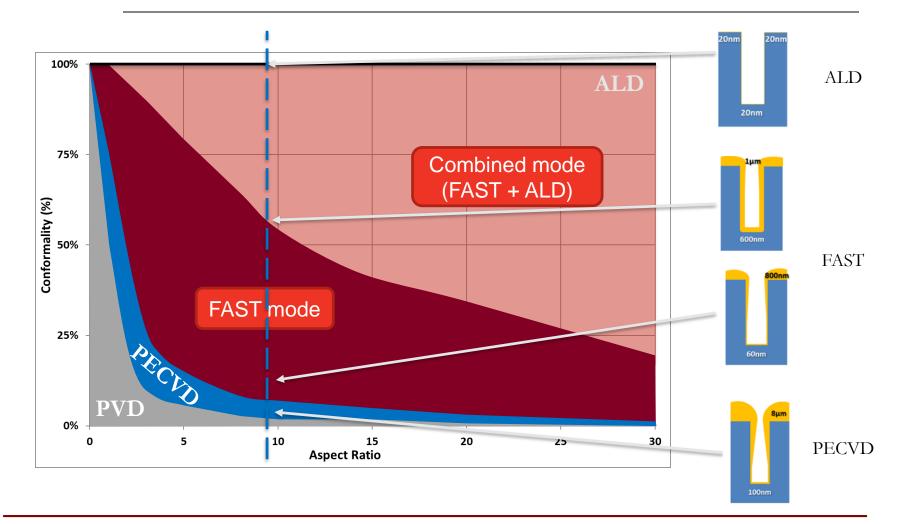

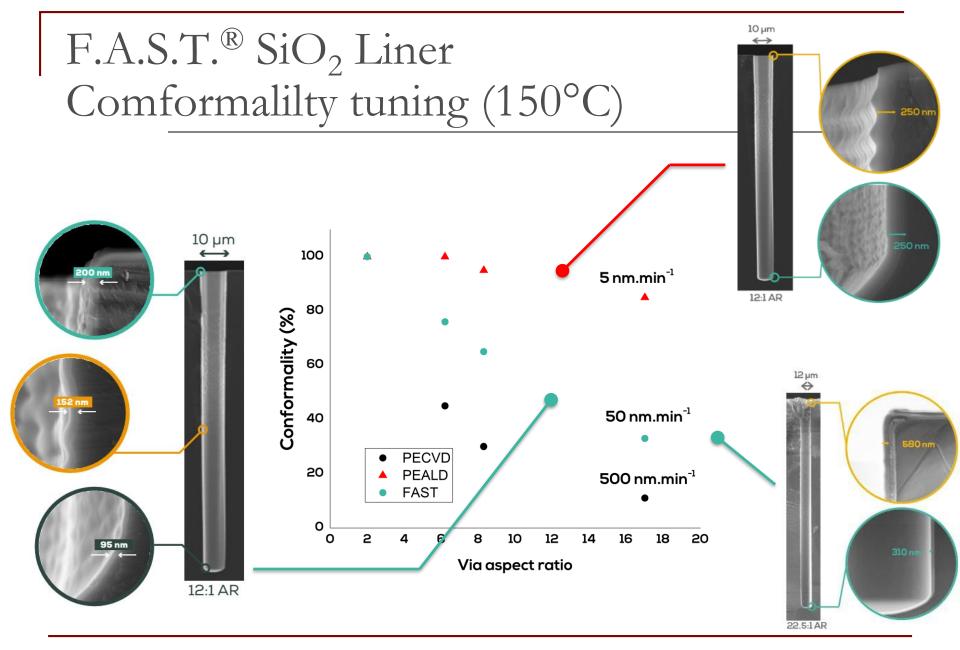

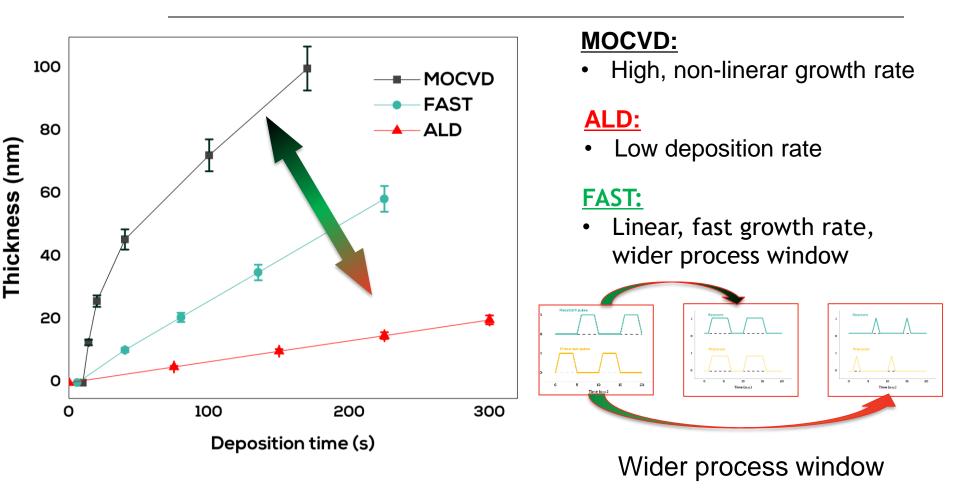

## $F.A.S.T.^{\textcircled{R}}\ Crossroads\ of\ ALD\ and\ CVD$

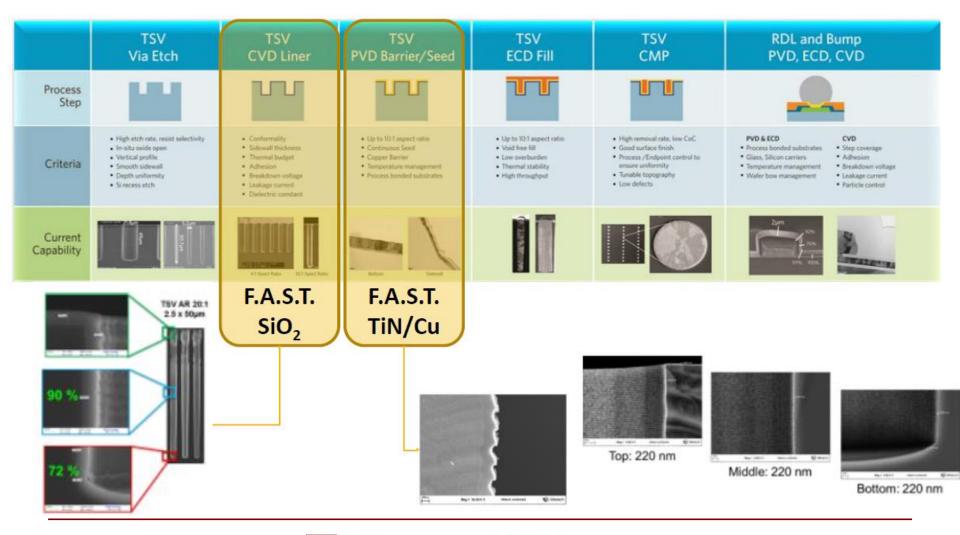

## 3D Technology Approaches for TSV

#### Provides increased conformality vs. PECVD, PVD

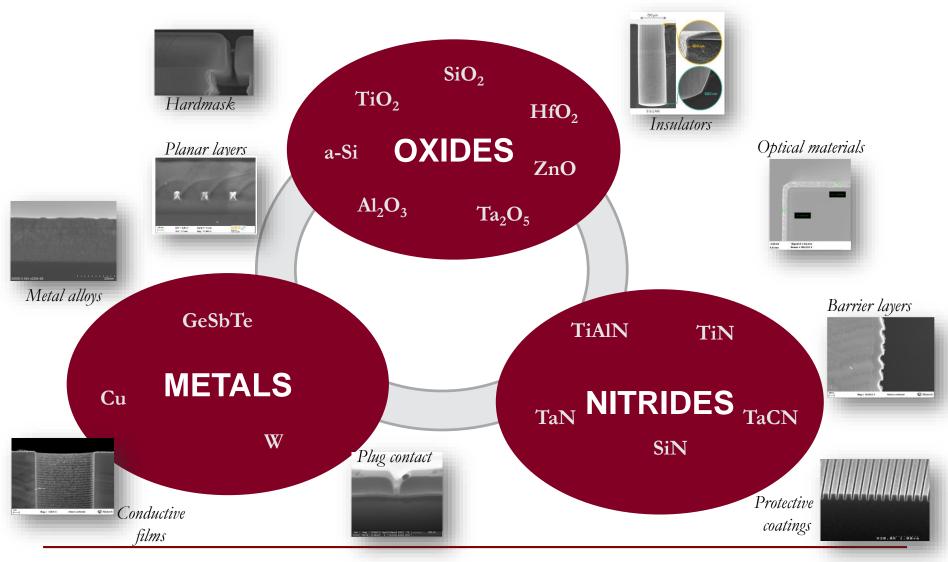

## Wide material range and applications

## 3-D Integration

## TiN example with FAST (375C)

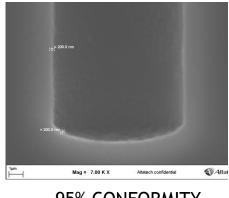

## Cu film performances

Deposition rate 30nm/min

Using Cupraselect<sup>®</sup> precursor and H<sub>2</sub>

Deposition temperature below 200°C

200

Temperature (°C)

Deposition

۲

۲

50

40

30

20

10

0

Cu bulk

160

180

140

Resistivity (µΩ.cm)

# With a state of the state Mage 7 20 KZ

95% CONFORMITY 10:1 AR

220

CVD

-FAST

240

## Surface Activation and Cleaning for Wafer Bonding

150mm wafer Scanning Acoustic Microscope

Silicon to Silicon and Silicon to Quartz. Si-OH + HO-Si  $\rightarrow$  Si-O-Si + H<sub>2</sub>0

HDRF plasma: reduced ion-impact allowing longer exposure to radicals. Lower surface activation energy promotes bonding

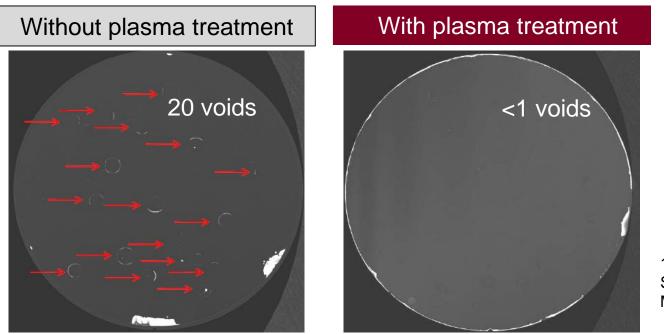

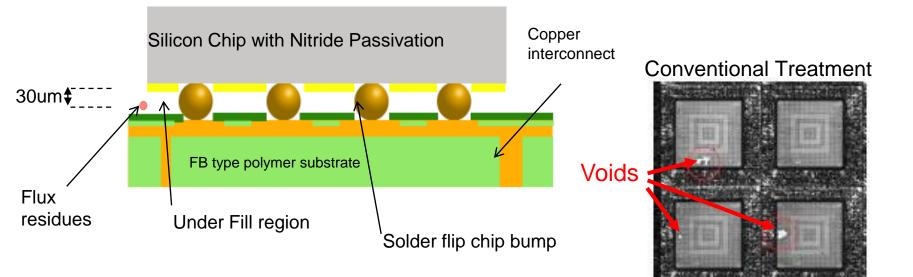

## Underfill – surface activation at low temperature

#### Benefits:

- · Better epoxy wetting and reflow

- Fewer voids, increased yield

Chemical, low UV and ions, low temp

Void-free underfil distribution

Example: contact angle from  $60-80^{\circ}$  to  $10^{\circ}$  with O\* radical exposure

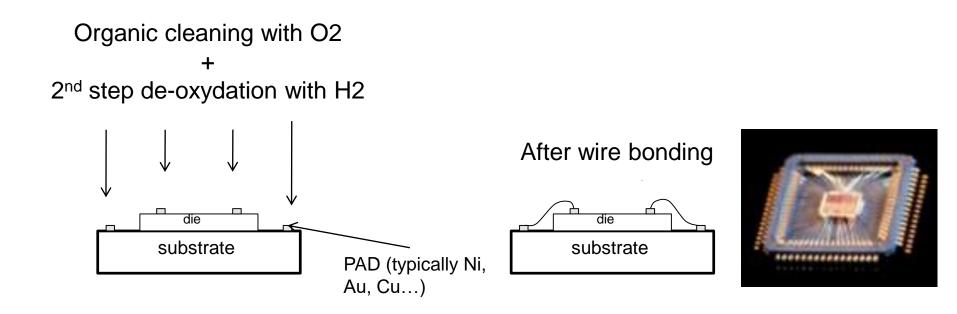

## Wire Bonding Pad Cleaning

Contamination and/or oxidation removal from the bond pads prior to wire bonding to increase reliability and yields

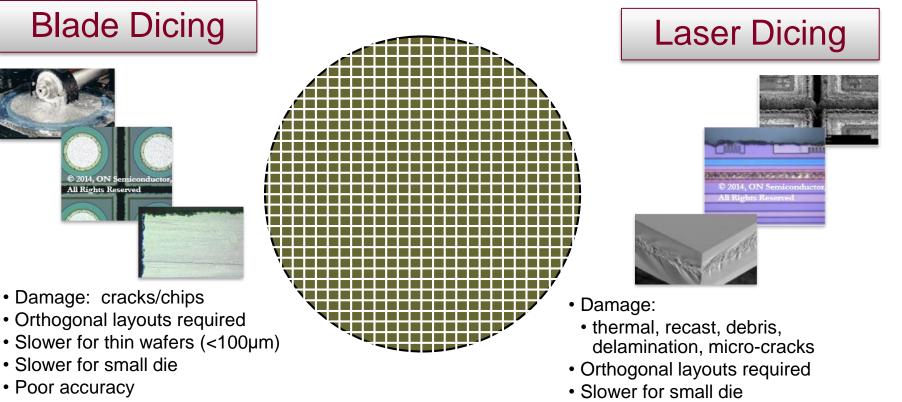

## Current Wafer Dicing Technology - Sequential Processes

- Debris and water residues

- 🖻 Plasma-Therm

Multiple passes for thicker wafers

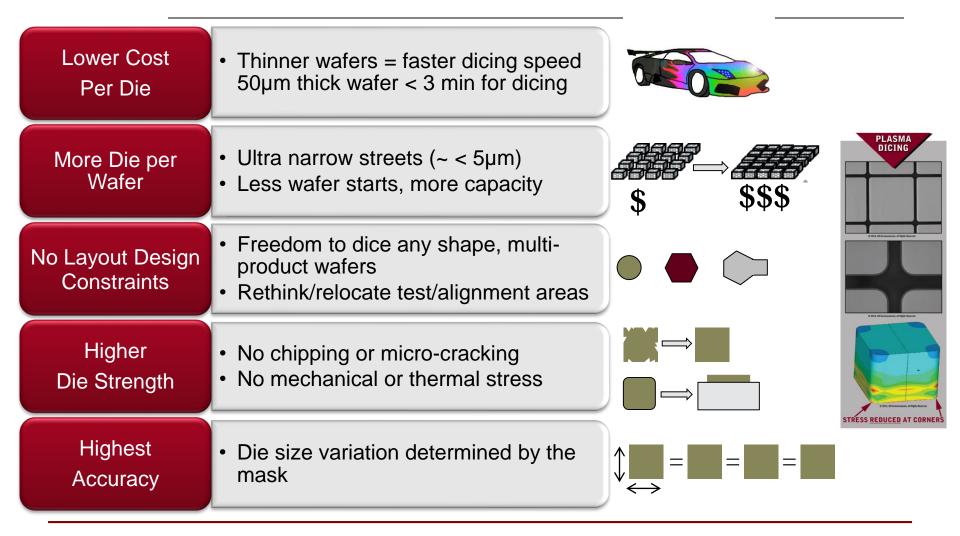

## Plasma Dicing: Parallel Process

- Chemical process low temperature

- No silicon damage

- Thinner wafers = shorter process

- High selectivity = low setup cost

- No additional mask required

- No tape damage

- Accurate and precise ontrol of die sze

- Dice any shapes/layouts

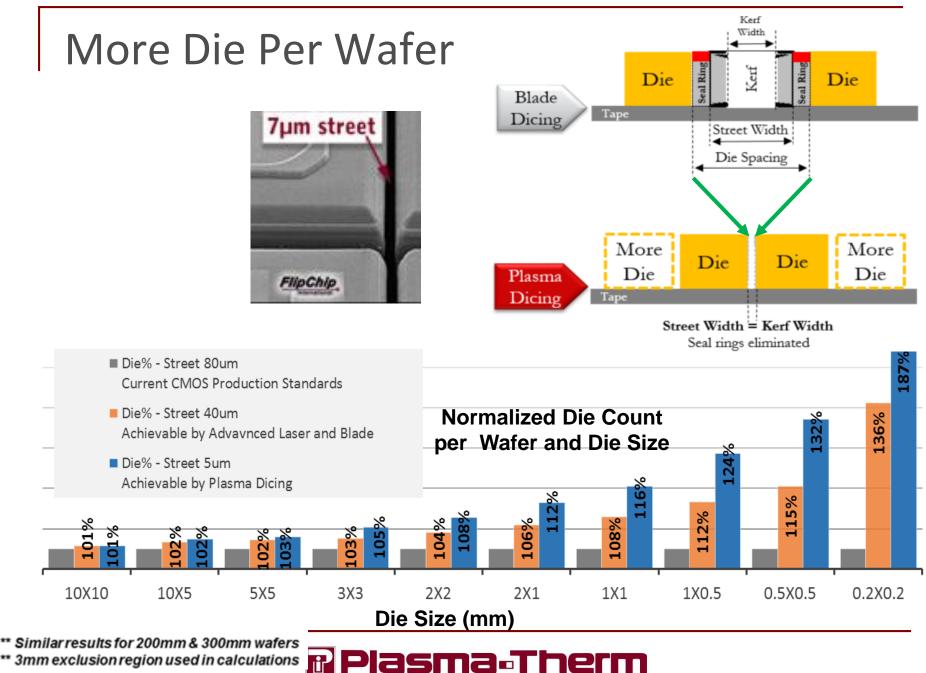

## Plasma Dicing Benefits

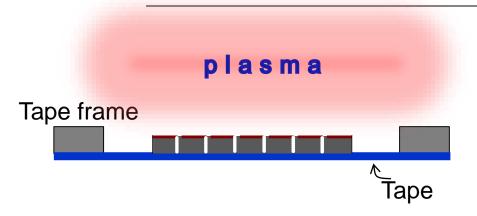

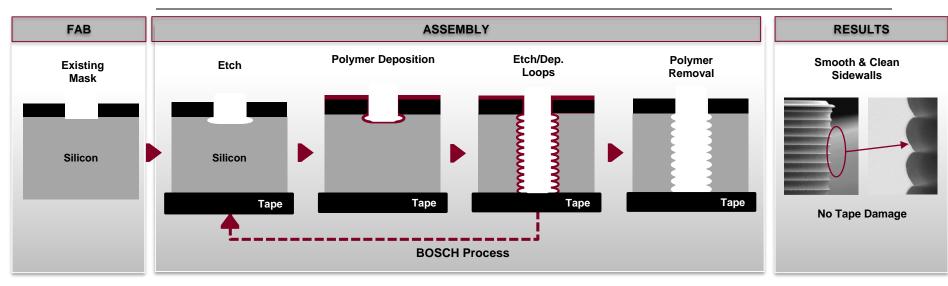

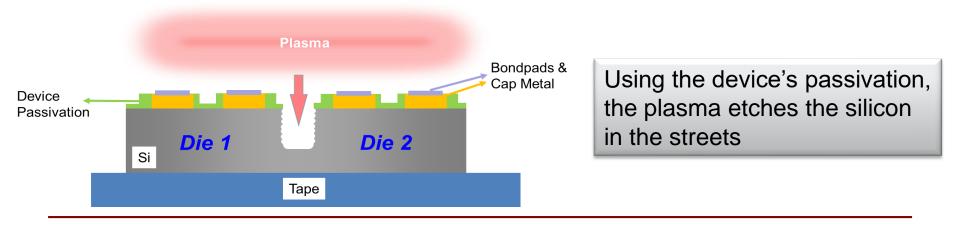

## Plasma Dicing on Tape Low temperature, highly selective DRIE Bosch

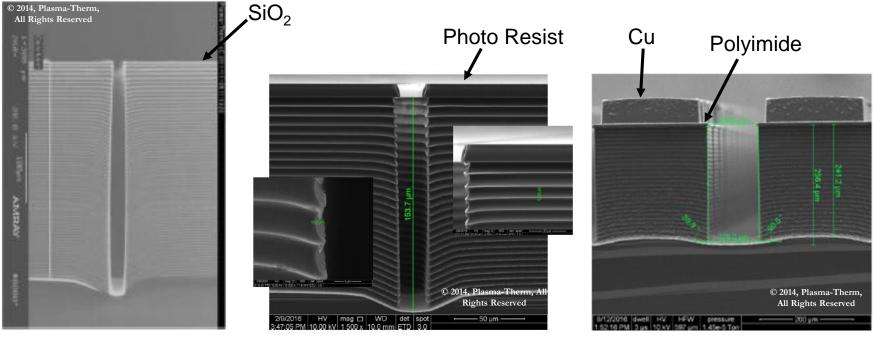

## A Variety of Passivation Materials Can Serve as Masks

- SiO<sub>2</sub> Mask

- Depth: 300μm

- Width: 15μm

- Selectivity: >800

- No notching

- PR Mask

- Depth: 150μm

- Width: 15μm

- Selectivity: >430

- No notching

- PI and exposed Cu

- Depth: 250μm

- Width: 100μm

- Selectivity: >250

- No notching

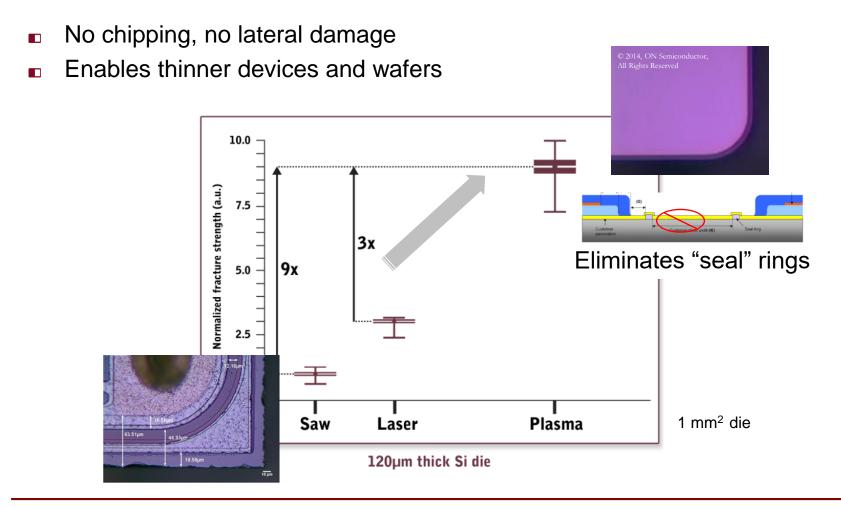

## Better dicing → Better die quality Superior Die Strength

\*\* 3mm exclusion region used in calculations

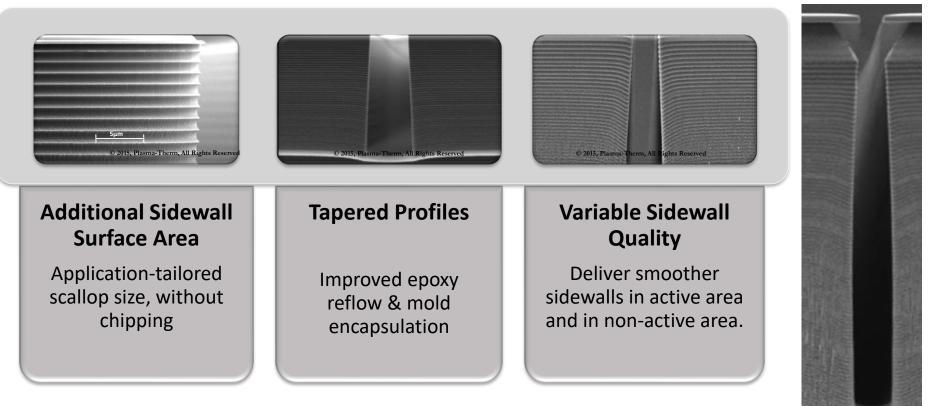

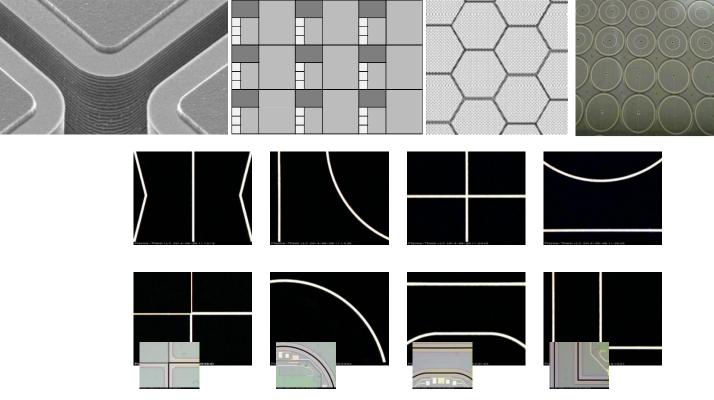

## New Dicing Capabilities with Sidewall Profile Control

Plasma dicing provides smoother sidewalls, a ndnew sidewall profile capabilities which can solve downstream packaging challenges

## New Dicing Capabilities Dice any shape or layout

**Examples:** Power devices, multi-product wafers, RF devices, LEDs, image sensors, microphones

© 2014, Plasma-Therm LLC, All Rights Reserved

## Plasma Dicing Adoption

|                    | Qualified (in production on MDS)                 |                                            |            |                          | Under Qualification      |                                            |                                            |

|--------------------|--------------------------------------------------|--------------------------------------------|------------|--------------------------|--------------------------|--------------------------------------------|--------------------------------------------|

|                    | Power                                            | LED                                        | RFID       | IR Image<br>sensor       | 3D MEMS                  | III-V                                      | CMOS                                       |

| Wafer size         | 6 & 8"                                           | 4 & 6"                                     | 8"         | 8"                       | 8"                       | 3 & 4"                                     | 8" & 12"                                   |

| Wafer type         | Si,<br>GaN/Si                                    | Si,<br>Ge                                  | Si         | Si                       | Si                       | GaAs                                       | Si                                         |

| Street size        | 10µm                                             | <5µm                                       | 7µm        | Round die                | 20µm                     | 30µm                                       | 10µm                                       |

| Wafer<br>thickness | >50µm                                            | ≤120µm                                     | 100µm      | 400µm                    | 100+300µm                | 300µm                                      | 50 to<br>750µm                             |

| Assembly           | Wirebond<br>Flip Chip                            | Wirebond                                   | Flip Chip  | Confidential             | Flip Chip                | Wirebond                                   | Flip Chip                                  |

|                    | © 2014, ON Semiconductor,<br>All Rights Reserved | © 2015 Plasma Therm<br>All Rights Reserved | 7µm street | Customer<br>confidential | Customer<br>confidential | © 2015 Plasma Therm<br>All Rights Reserved | © 2015 Plasma Therm<br>All Rights Reserved |

## Acknowledgements

Christopher Johnston, Plasma Therm Thierry Lazerand, Plasma Therm Dr. Marco Notarianni, Plasma Therm Dr. Kenneth Mackenzie, Plasma Therm Yannick Pilloux, Plasma Therm Julien Vitielo, Plasma Therm Gordy Grivna, ON Semiconductor Jason Doub, ON Semiconductor Dr. Tomotak Tabushi, DISCO Dr. Frank Wei, DISCO Hideyuki Sando, DISCO JS Jung, DISCO

Thank your for your contributions and materials to prepare this presentation

## Thank you

Contact: david.lishan@plasmatherm.com