NCCAVS CMPUG/TFUG/PAG Joint Meeting ADVANCED PACKAGING TECHNOLOGY Tuesday June 12, 2018

Equipment and Process Challenges for the Advanced Packaging Landscape

Veeco Precision Surface Processing

Laura Mauer

June 2018

» Advanced Packaging Market Landscape

» Packaging Concepts and Equipment Challenges

» Approaches and Examples

» Summary

2

# Advanced Packaging Landscape - Markets

- Smartphones

- Memory

- Connectivity

- Data centers

- Automotive

- Smart Home

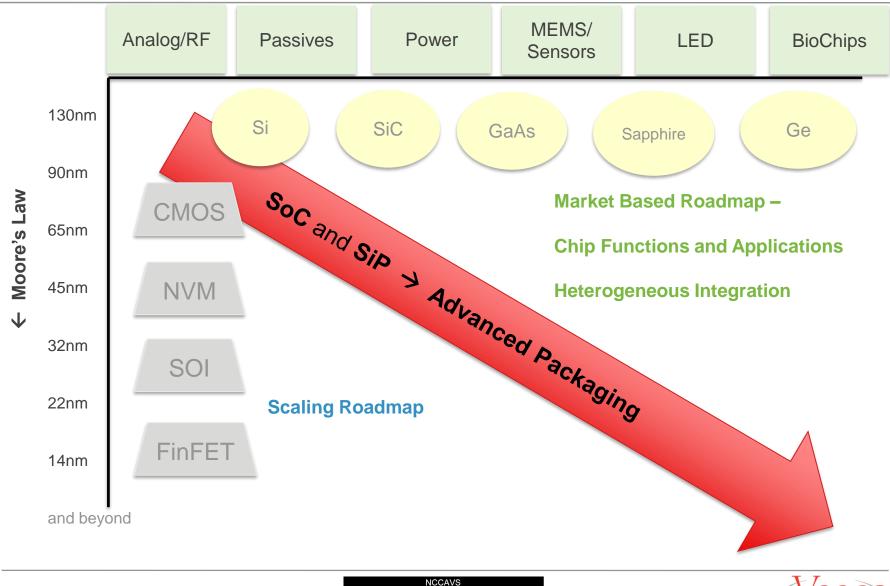

# Moore's Law and More than Moore

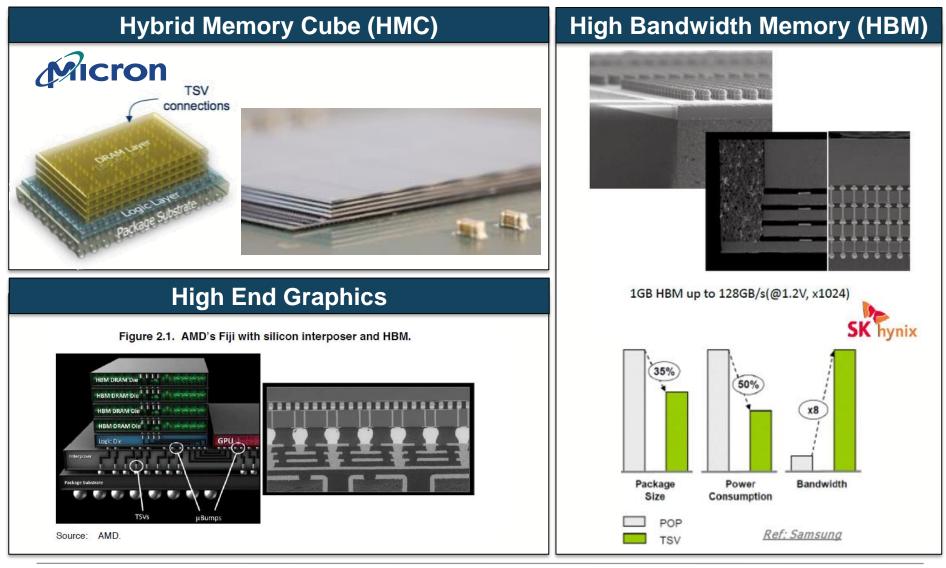

# 3D High Performance Devices Require TSV

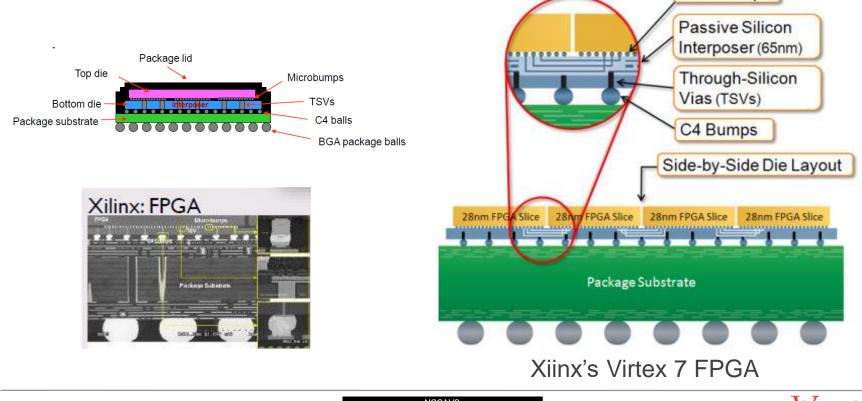

# 2.5D Interposers for Heterogeneous Integration

A configuration where dies are mounted side by side on one side of a thin (~ 100 um) <u>silicon, glass, or organic interposer</u> using through *silicon* vias (TSV), through *glass* vias (TGV) or through *organic* vias (TOV), respectively through the interposer to connect the dies with the package substrate.

Microbumps

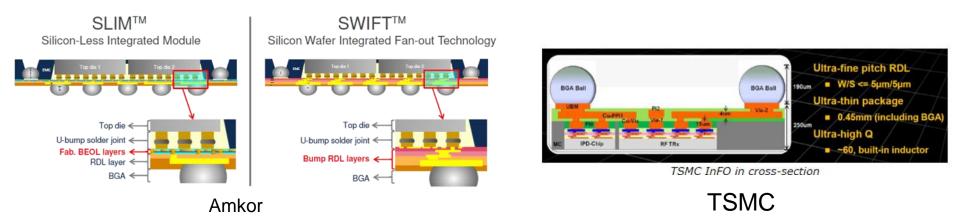

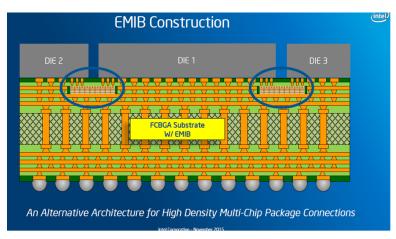

# Other Technologies for Heterogeneous Integration

Source: ASE.

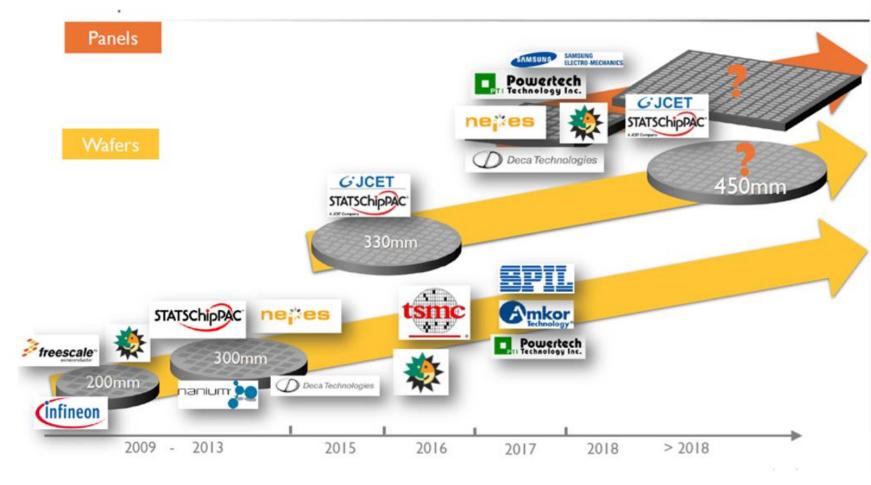

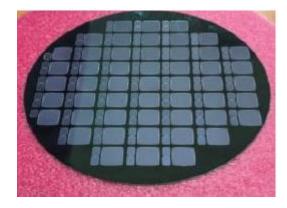

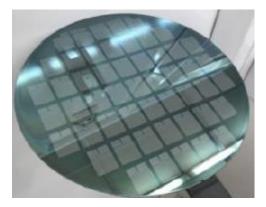

# Wafers / Panels / Sizes for Advanced Packaging

Source: Yole

YOLE

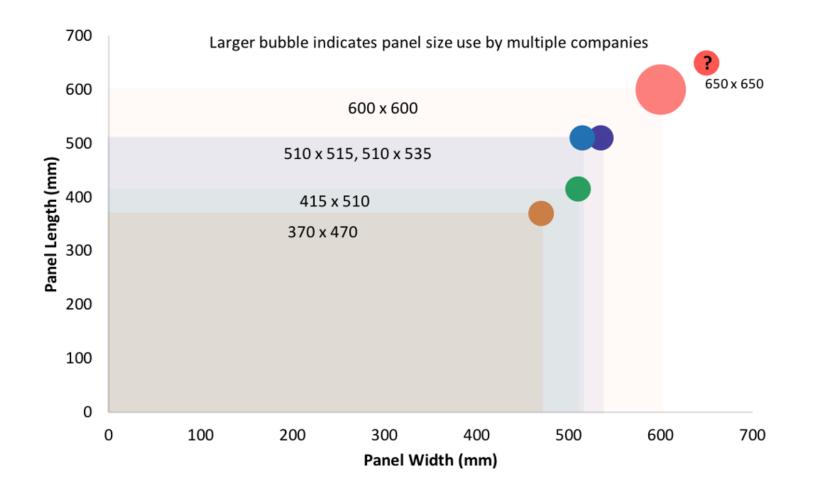

# Panel Size Uncertainty for Large Area Fan-Out

Source: TechSearch International

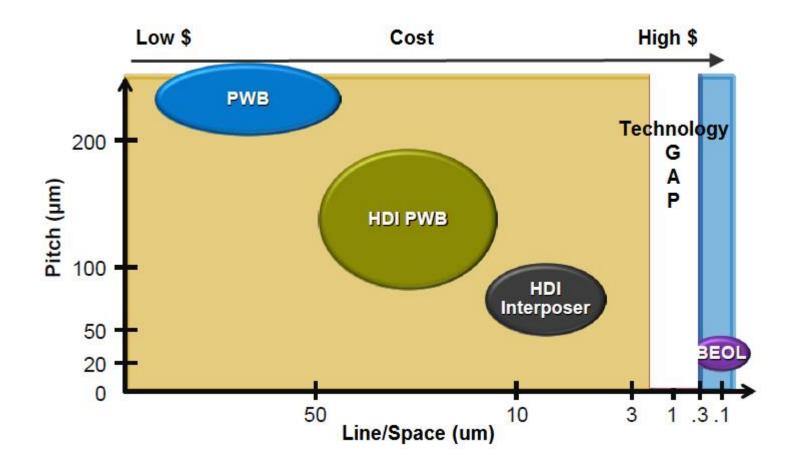

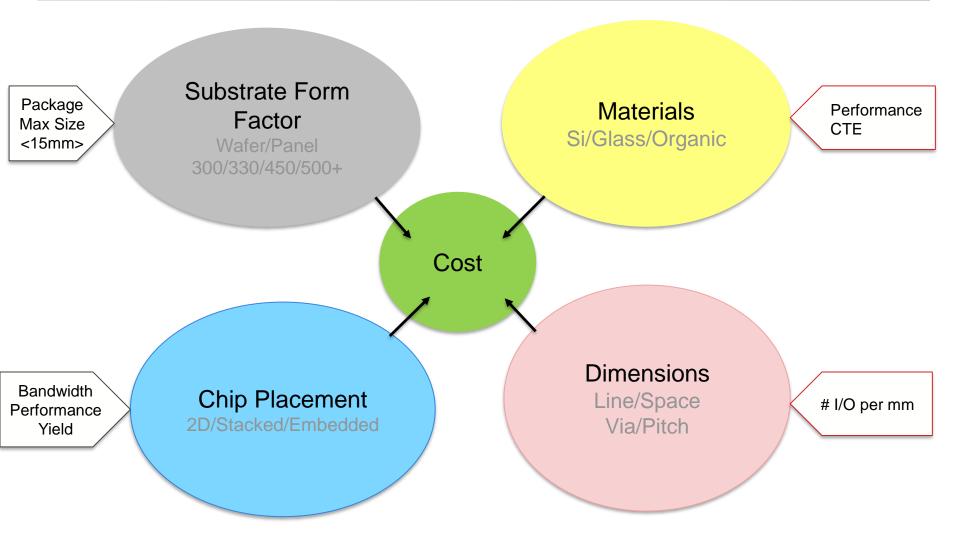

# **Dimensions and Cost**

# **Advanced Packaging Options**

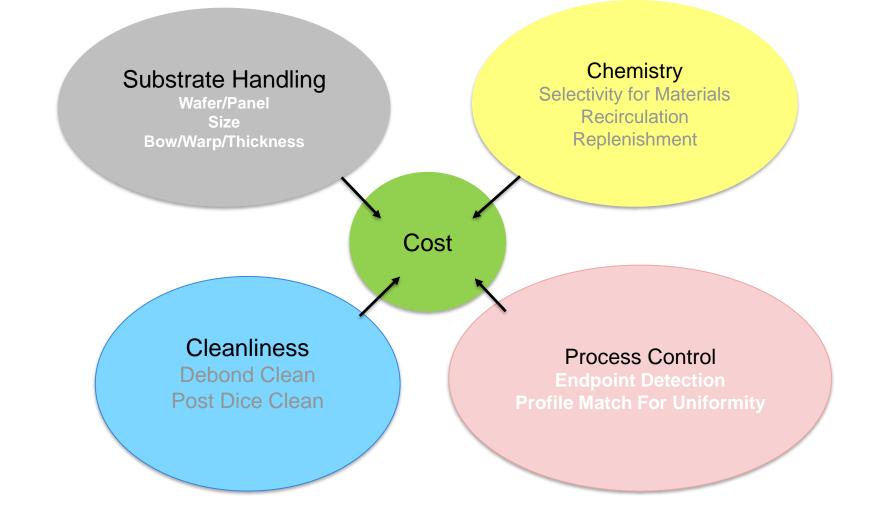

### Equipment and Process Flexibility for Advanced Packaging Options

# Chemistry Example: Wafer Thinning

13 Copyright © 2018 Veeco Instruments Inc.

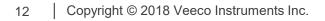

## Requirements for 2.5D and 3D Wafer Thinning Applications

# Silicon Wet Etch Options

### > KOH (Potassium Hydroxide)

- » Good etch rate and selectivity (Silicon to Oxides /Cu)

- » Ionic contamination (K+)

- > TMAH (Tetramethyl Ammonium Hydroxide)

- » Safety concerns (toxicity) at high concentration

- » Slow etch rate

- > HF / Nitric based chemistry "Spinetch"

- » High etch rates but poor selectivity (Silicon to Oxides /Cu)

# > SACHEM Reveal Etch™

- » Lower toxicity than TMAH

- » Higher etch rate and good selectivity (Silicon to Oxides /Cu)

# Etch Selectivity

> Ability to etch silicon and stop on a variety of materials without causing damage

| HF/Nitric Mixture* |                       |                           | SACHEM Reveal Etch™ |                       |                           | SACHEM ST2011 |                       |                           |

|--------------------|-----------------------|---------------------------|---------------------|-----------------------|---------------------------|---------------|-----------------------|---------------------------|

| Material           | Etch Rate<br>(nm/min) | Selectivity<br>to Silicon | Material            | Etch Rate<br>(nm/min) | Selectivity<br>to Silicon | Material      | Etch Rate<br>(nm/min) | Selectivity<br>to Silicon |

| Si                 | 9000                  |                           | Si                  | 711                   |                           | Si            | 150                   |                           |

| SiO2               | 50                    | 180                       | SiO2                | 0.5                   | 1422                      | SiO2          | 0.5                   | 300                       |

| Si3N4              | 2.7                   | 3333                      | Si3N4               | 0                     | > 10000                   | Si3N4         | 0                     | >10000                    |

| Cu                 | 2400                  | 3.8                       | Cu                  | 12                    | 59                        | Cu            | 0                     | >10000                    |

| Ti                 | 750                   | 12                        | Ti                  | 0                     | >10000                    | Ti            | 0                     | >10000                    |

| TiW                | 144                   | 63                        | TiW                 | 1.9                   | 374                       | TiW           | 0                     | >10000                    |

| PI                 | 0                     | >10000                    | PI                  | 5.6                   | 95                        | PI            | 0                     | >10000                    |

| PBO                | 0                     | >10000                    | PBO                 | 7.5                   | 126                       | PBO           | 0                     | >10000                    |

\* Spinetch D 1:6:2:1 HF:Nitric:Phosphoric:Sulfuric

16

Veeco

Copyright © 2018 Veeco Instruments Inc.

# > Step 1

- » Spinetch D (HF / Nitric mixture)

- » To smooth surface and eliminate grind marks

- » Contour silicon thickness for improved uniformity

# > Step 2

- » SACHEM Reveal Etch™ (or ST2011)

- » Selective etch of silicon

- » TSV oxide liner and Cu via

- » Other materials present at end of silicon etch for FOWLP

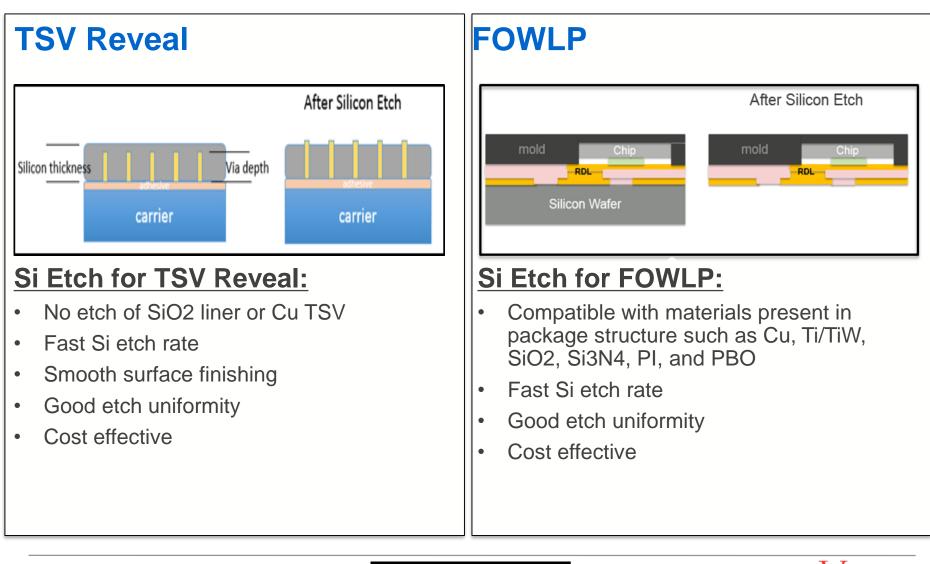

# **Etch Uniformity**

- Post Grind non-uniformities can have radial dependence

- » Center to edge variations

- Single wafer etch process can compensate for radial nonuniformities

- » More/Less etch in center of wafer

- Resulting Silicon wafer thickness is more uniform

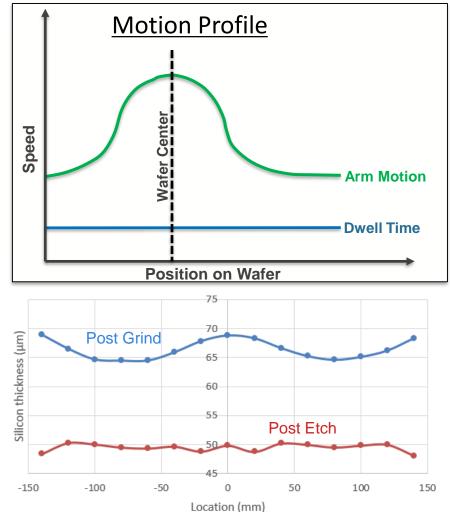

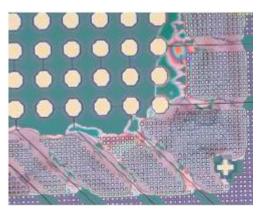

# Integrity of Via and Oxide Liner for TSV Reveal

# **FOWLP Silicon Etch Results**

Strong Alklaine Etch (TMAH) caused damage to underlying RDL structure

Use of acid etch or 2 step etch process provides good results with no damage to underlying structure

"High Density TSV-Free Interposer (TFI) Packaging with Submicron Cu Damascene RDLs for Integration of CPU/GPU and HBM" IME presentation at ECTC 2018

# Process Control: Etch and Undercut

21 Copyright © 2018 Veeco Instruments Inc.

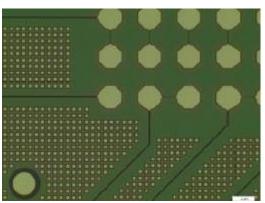

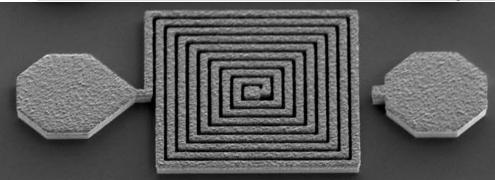

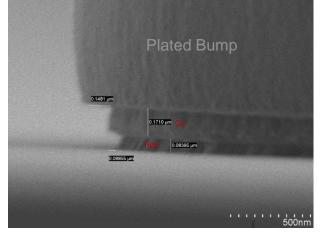

# **UBM/RDL Etch and Dimensions**

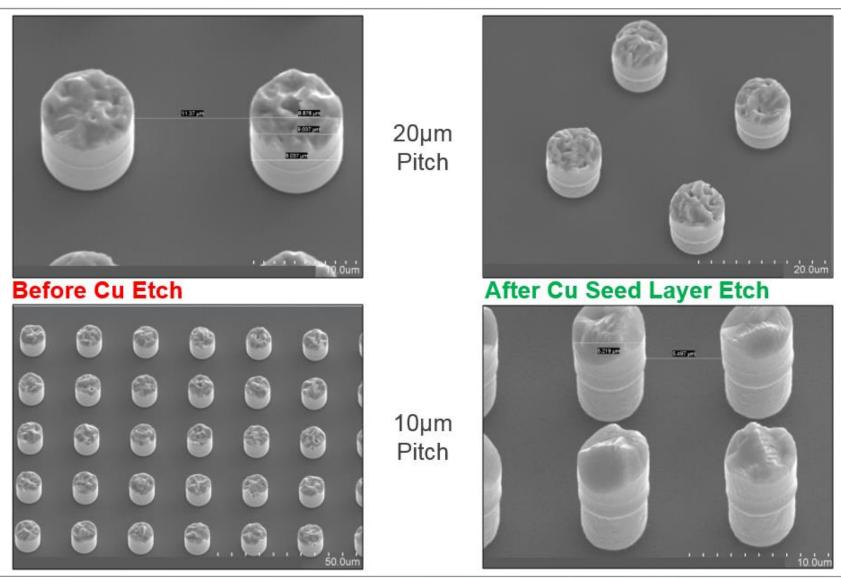

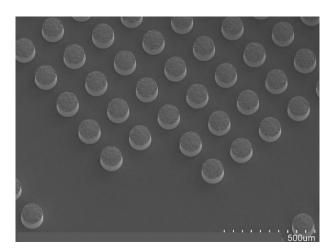

- > Smaller bumps with increased density

- > Need for less undercut and controlled etch

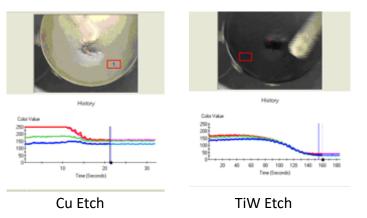

- » PSP WaferChek® Process Monitor for endpoint detection

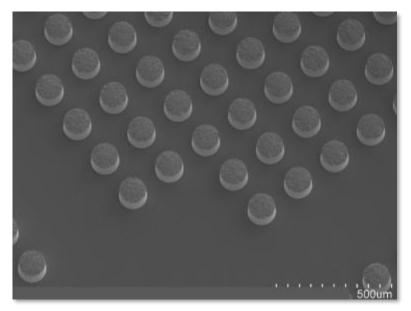

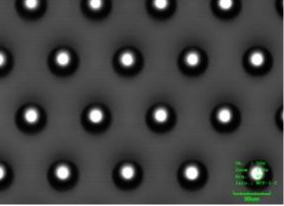

- > Recent demonstration on 10 and 20µm pitch bumps

#### **Current Products**

22

#### Future

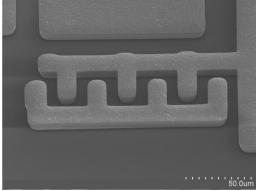

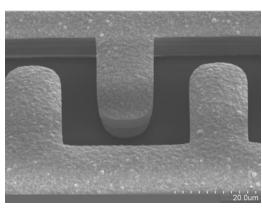

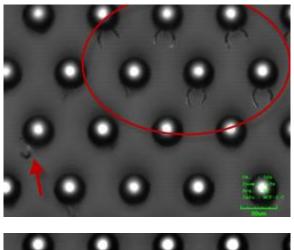

# UBM Etch – smaller bumps and higher density

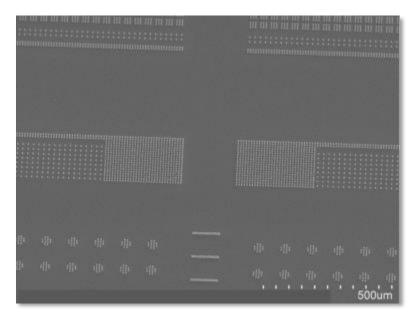

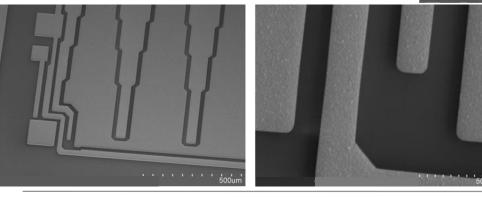

# RDL Etch – Pattern Density Challenges

**Isolated and Dense Features**

### **Embedded structures**

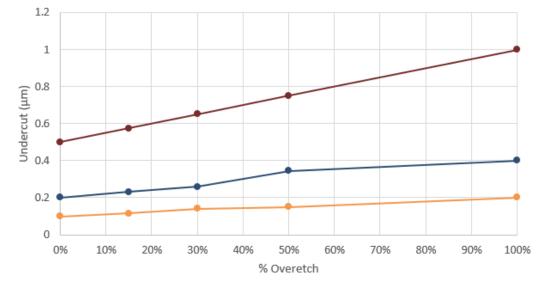

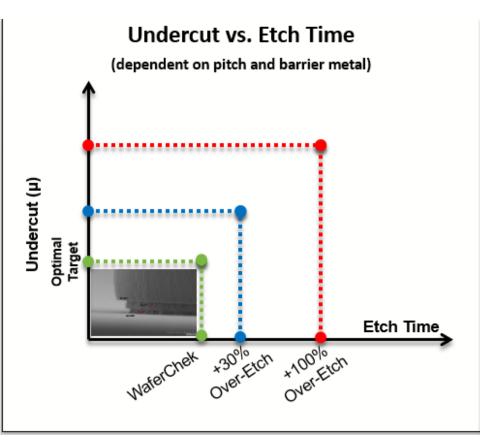

# Undercut and Overetch

- > Isotropic etch results in undercut equal to thickness of film if etch stopped at endpoint

- > For narrow Line/Space dimensions undercut must be minimized

- » Reduce Thickness of seed layer

321137-

» Eliminate / Reduce overetch

Seed Layer Overetch and Undercut

0 3704 (#

# WaferChek® In-Situ Process Control for Endpoint Detection

#### UBM Etch : Cu Over TiW

### **Process Requirements**

- Completely etch away field metal (barrier and seed metals)

- Keep overetch to a minimum for bump integrity, electrical performance and throughput

- ➢No substrate attack

- Low Cost \$/wafer processed

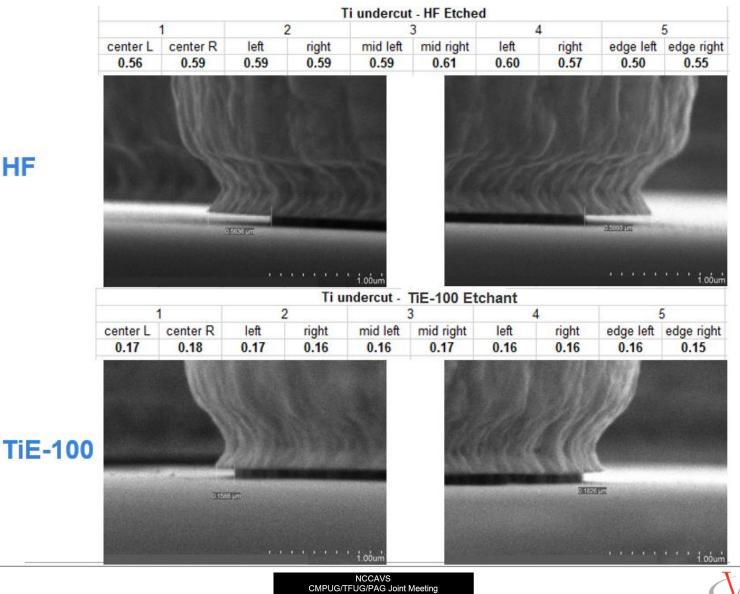

# **Undercut and Etchant Selection**

HF

Copyright © 2018 Veeco Instruments Inc. 27

ADVANCED PACKAGING TECHNOLOGY Tuesday June 12, 2018

## Quantifying the Impact of Over-Etch on WPY Under Bump Metallization (UBM) Etch Example

### Example: Over-Etch Impact on T/P

| Etch Example*                                              | Cu or Ti Etch | Production<br>Loss |  |  |  |  |  |

|------------------------------------------------------------|---------------|--------------------|--|--|--|--|--|

| Etch Time (sec)                                            | 60            | 2000               |  |  |  |  |  |

| SRD Time                                                   | 60            |                    |  |  |  |  |  |

| Overall Process Time (chambers in Parallel)                | 120           |                    |  |  |  |  |  |

| Handling (wafers in/ out)                                  | 24            |                    |  |  |  |  |  |

| Number of Chambers                                         | 1             |                    |  |  |  |  |  |

|                                                            |               |                    |  |  |  |  |  |

| Throughput (wph) with WaferChek                            | 25            | Baseline           |  |  |  |  |  |

| Impact of 30% over-etch (wph)                              | 22            | 11%                |  |  |  |  |  |

| Impact of 100% over-etch (wph)                             | 18            | 29%                |  |  |  |  |  |

|                                                            |               |                    |  |  |  |  |  |

| Available Production Hours                                 | 7,862         |                    |  |  |  |  |  |

|                                                            |               |                    |  |  |  |  |  |

| Wafers Per Year with WaferChek                             | 196,560       | Baseline           |  |  |  |  |  |

| Wafers Per Year at 30% over-etch                           | 174,720       | 11%                |  |  |  |  |  |

| Wafers Per Year at 100% over-etch                          | 138,748       | 29%                |  |  |  |  |  |

| * Process times will vary depending on feature dimensions, |               |                    |  |  |  |  |  |

| barrier metals, thickness, etchant                         |               |                    |  |  |  |  |  |

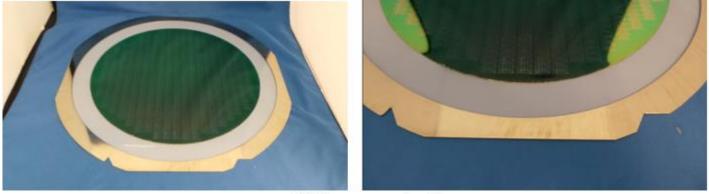

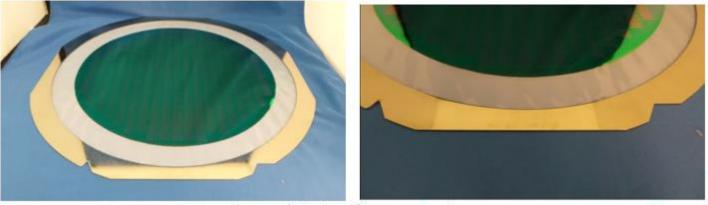

## Substrate Handling Example: Cleaning on Film Frame

# Cleaning Wafers on Film Frames – post debond from carrier

Larger than 300mm wafer ~380mm

Removing residual adhesive without affecting tape film frame  $\rightarrow$  combination of appropriate chemistry and physical force

# Removing thick layer of adhesive without damage

PRE - as received

Immediately after processing

31

# Cleaning post debond on film frames

- > Fixturing to handle and support wafer on film frame

- Chemistry for cleaning/stripping residual and compatible with tape

- > Use of physical force (high pressure spray / high velocity spray) to assist in cleaning

# Summary

- > No single road being followed for Advanced Packaging

- > Many different types of packages depending upon application requirements

- > Equipment flexibility and versatility will be needed to address

- » Substrate size and form factor

- » Shrinking dimensions

- » Materials

- > Process solutions combine equipment and chemistry