Electrical Engineering, Stanford University, CA, U.S.A.

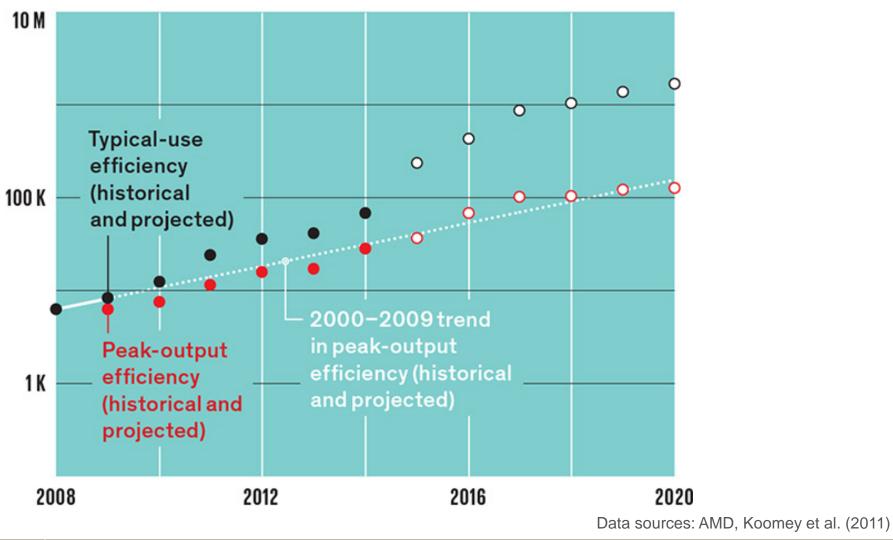

#### 50 years of Moore's law, "how about energy?"

#### ENERGY EFFICIENCY RELATIVE TO 1985 (1985 = 1.0)

2015.09.10.

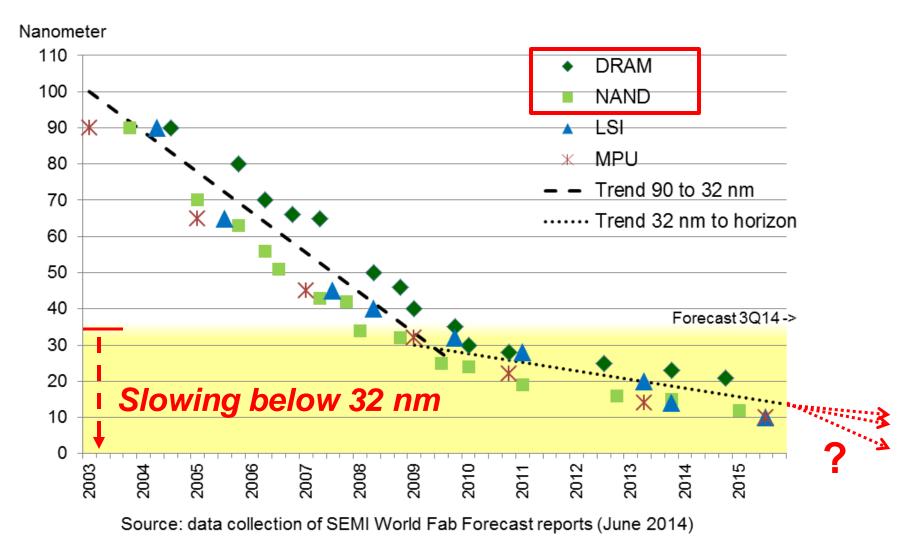

#### "Technology node transitions (volume production)"

#### "What's the difference?"

\$ 299

VS.

2015. 09. 10. Department of Electrical Engineer

## "Adding more NAND"

Ethan C. Ahn

VS.

#### **64 GB** (DRAM + *MORE NAND*)

2015.09.10.

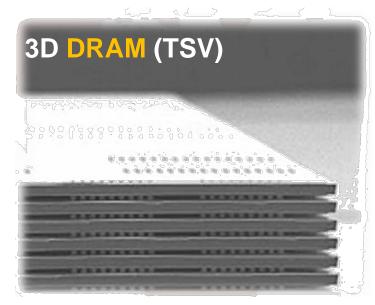

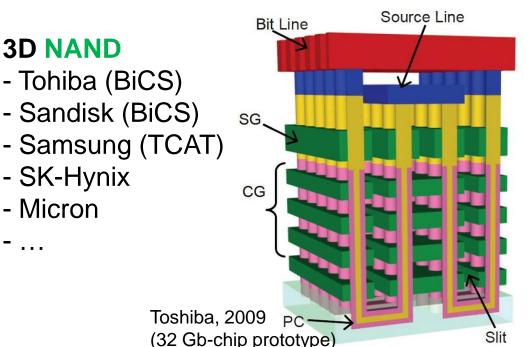

#### "New tricks to further increase density"

SK Hynix, 2013 (product)

## "Fundamental solution"

# Emerging non-volatile memory (NVM) ; sub-10 nm scalability & low cost (<0.1\$/GB)</pre>

- ...

#### "New" Players in NVM

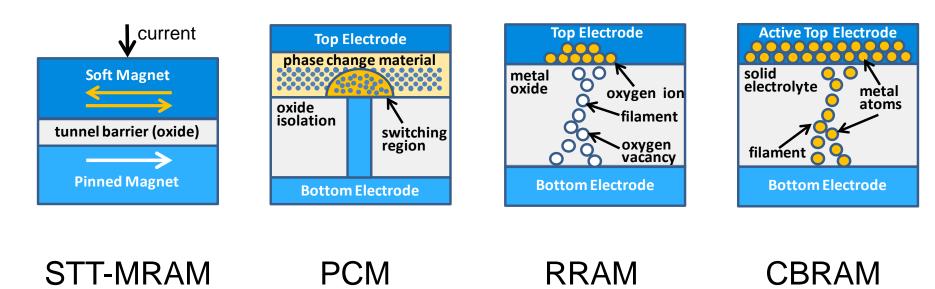

Spin torque transfer magnetic random access memory <u>P</u>hase <u>c</u>hange <u>m</u>emory <u>Resistive switching</u> <u>random access memory</u> <u>Conductive</u> <u>bridge</u> random access memory

#### Random access, non-volatile, no erase before write

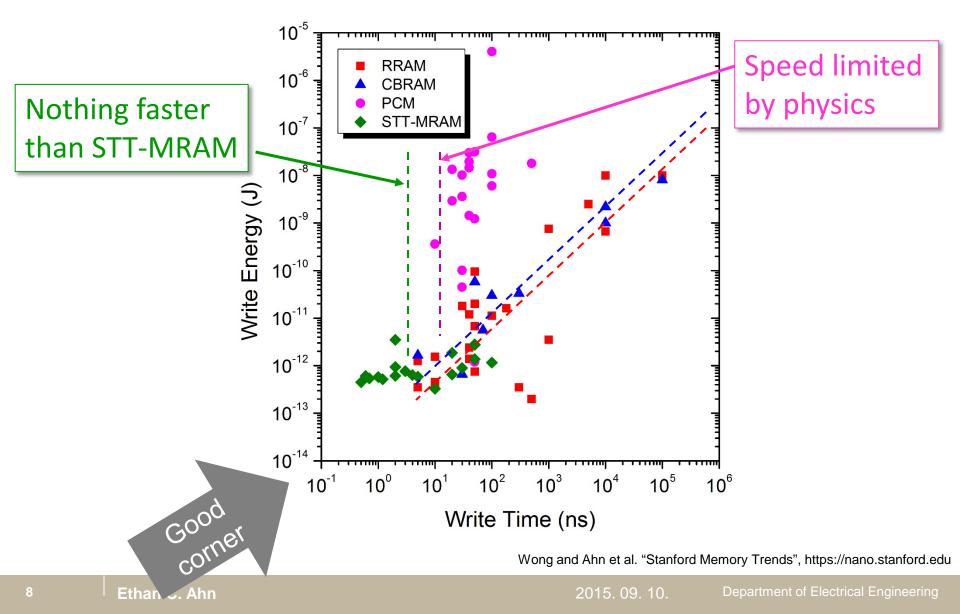

#### Energy vs Speed Trade-Off @ Device Level

# 2. Energy-efficient Architecture design

2015.09.10.

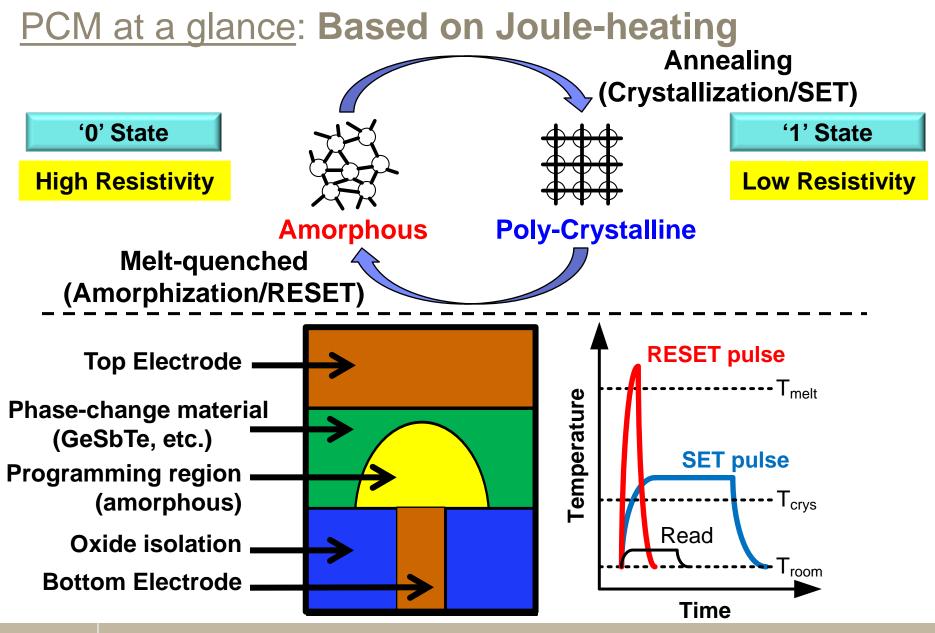

#### "How hot is Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>?"

2015. 09. 10. Departm

#### Example:

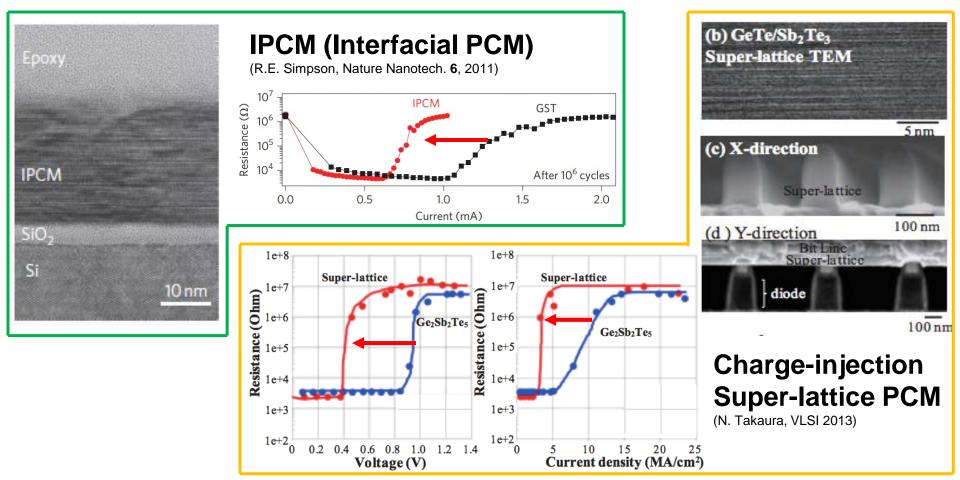

#### Recent studies with GeTe/Sb<sub>2</sub>Te<sub>3</sub> super-lattice structure

2015.09.10.

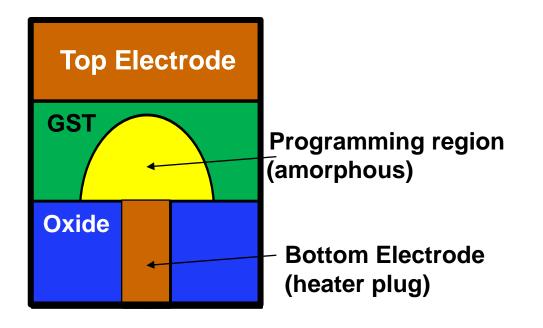

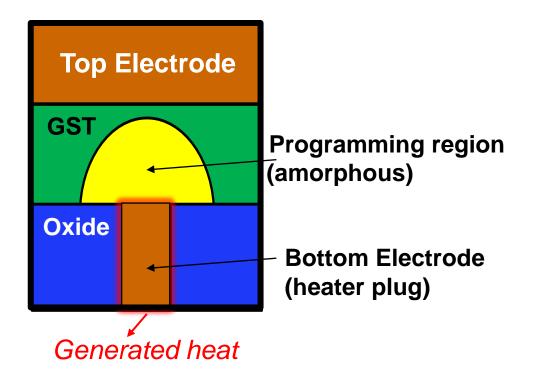

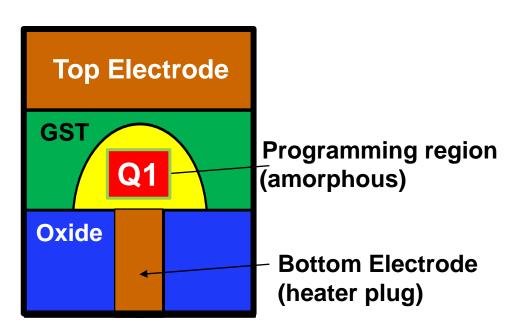

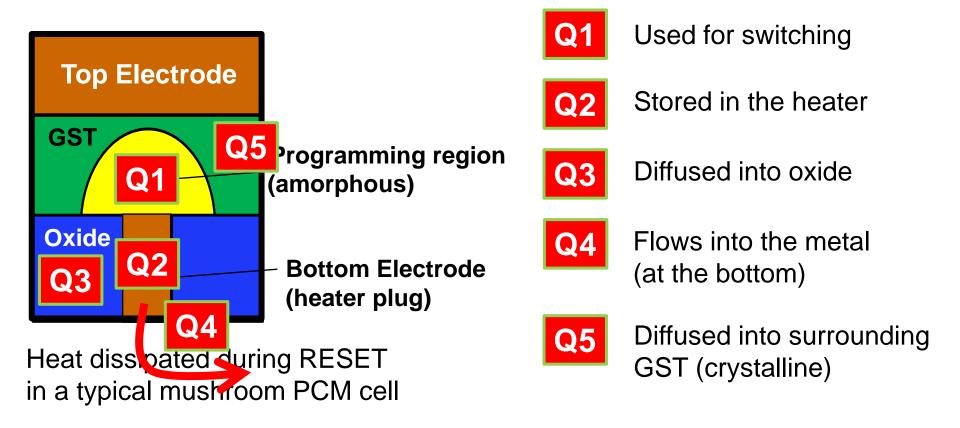

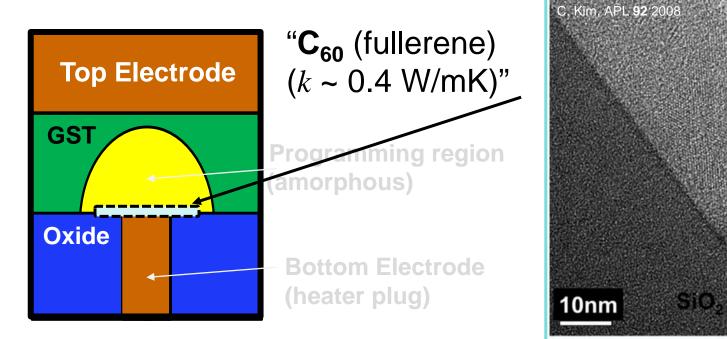

Remembering that PCM operation is based on "Joule Heating,"

Heat dissipated during RESET in a typical mushroom PCM cell

Used for switching

5

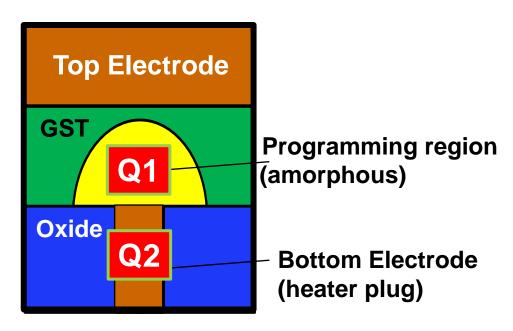

Remembering that PCM operation is based on "Joule Heating,"

Heat dissipated during RESET in a typical mushroom PCM cell

Used for switching

Stored in the heater

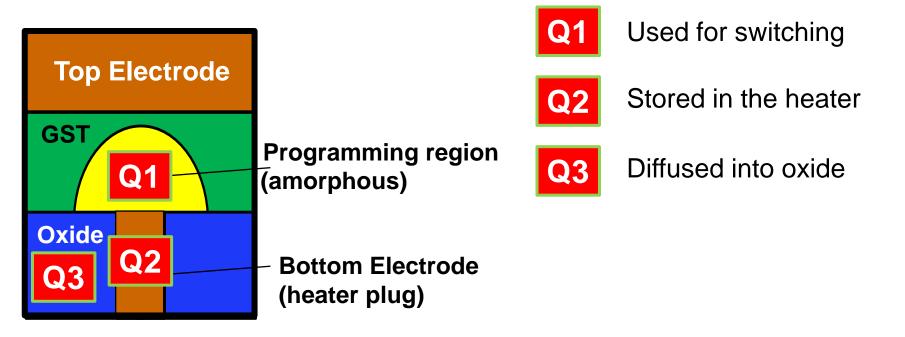

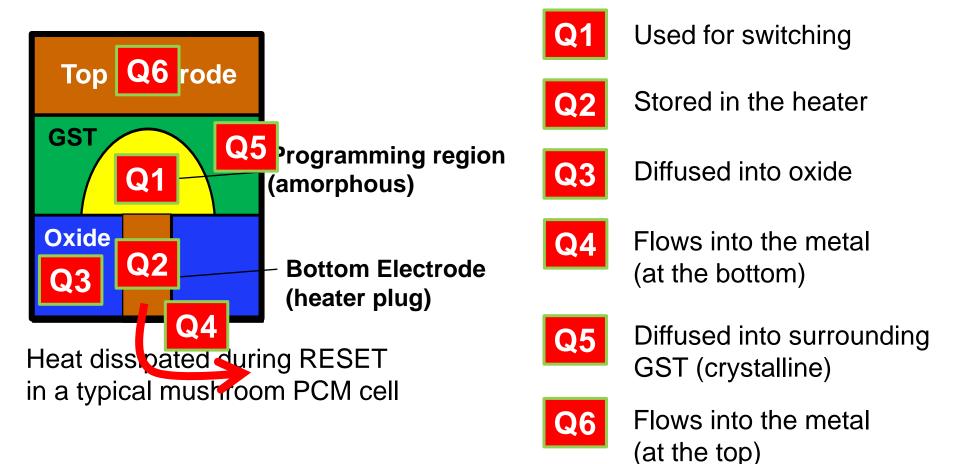

Remembering that PCM operation is based on "Joule Heating,"

Heat dissipated during RESET in a typical mushroom PCM cell

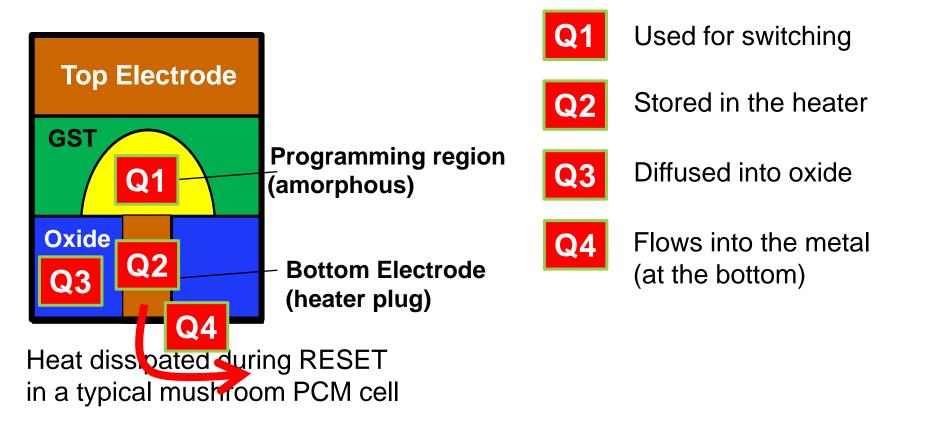

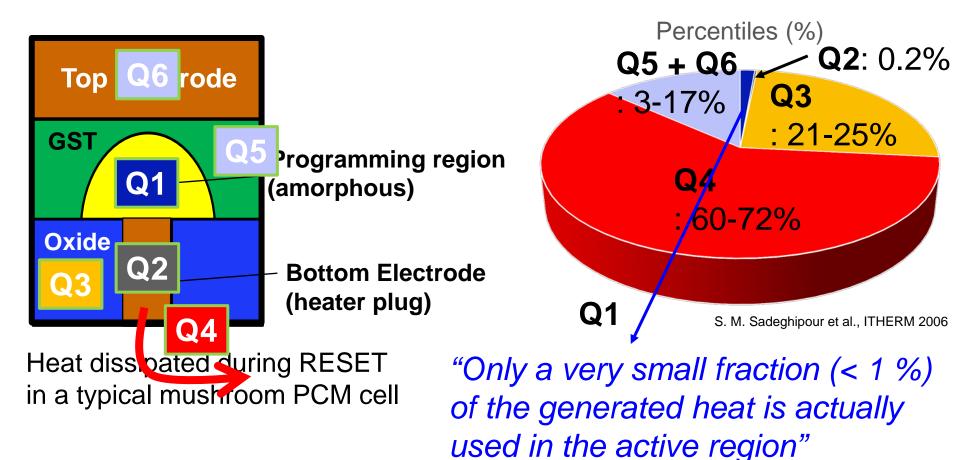

Remembering that PCM operation is based on "Joule Heating,"

Heat dissipated during RESET in a typical mushroom PCM cell "Only a very small fraction" (< 19, 2008) of the generated heat is actually used in the active region"

Ge\_Sb\_Te

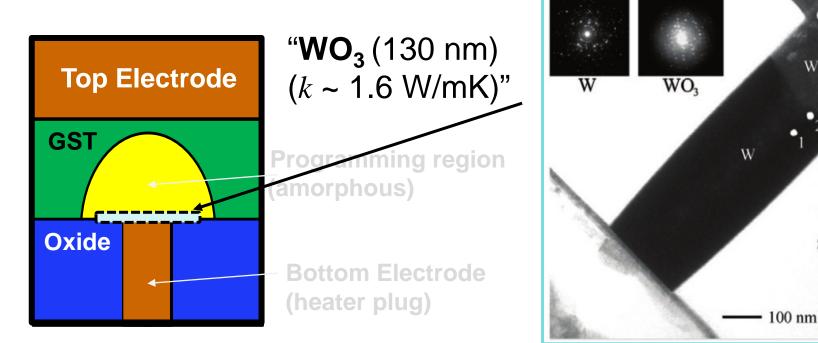

130 nm

WO<sub>3</sub>

SiO,

Remembering that PCM operation is based on "Joule Heating,"

Heat dissipated during RESET in a typical mushroom PCM cell "Only a very small fraction (< 1 %) of the generated heat is actually used in the active region"

23

Coating

## "How about graphene?"

#### The Janus faces of graphene

"In-plane"

See references [1] Pop et al. MRS Bull. 2012 [2] Guzman et al. ITherm. 2014 [3] Koh et al. Nano Lett. 2010 [4] Mak et al. APL 2010

#### "Out-of-plane"

SLG <sup>‡ 3 Å</sup> <sup>(</sup> "thermally equivalent" GST <sup>‡ 200 Å</sup>

Ahn et al. Nano Letters 2015

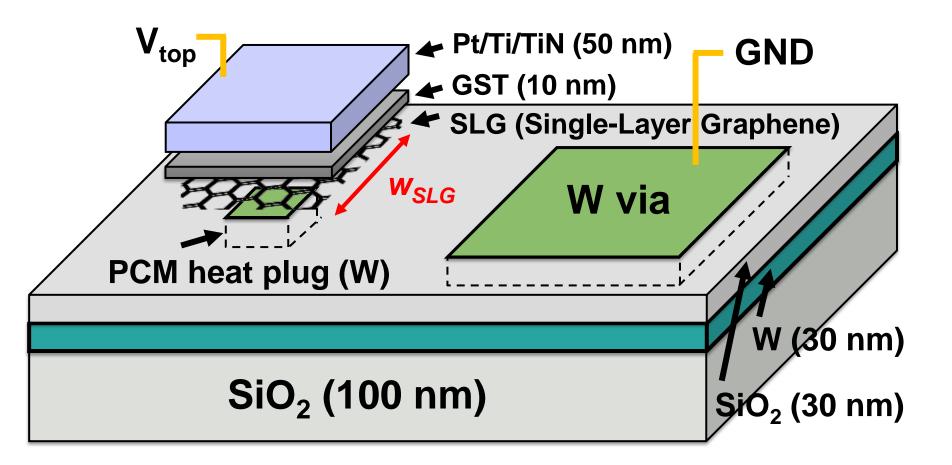

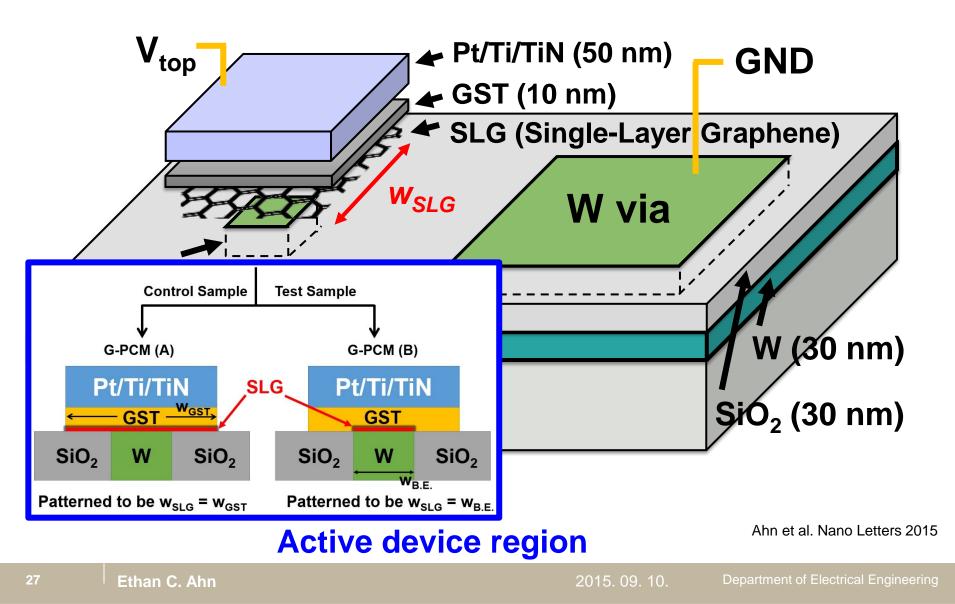

#### <u>G-PCM</u>: **Device structure**

Ahn et al. Nano Letters 2015

#### <u>G-PCM</u>: **Device structure**

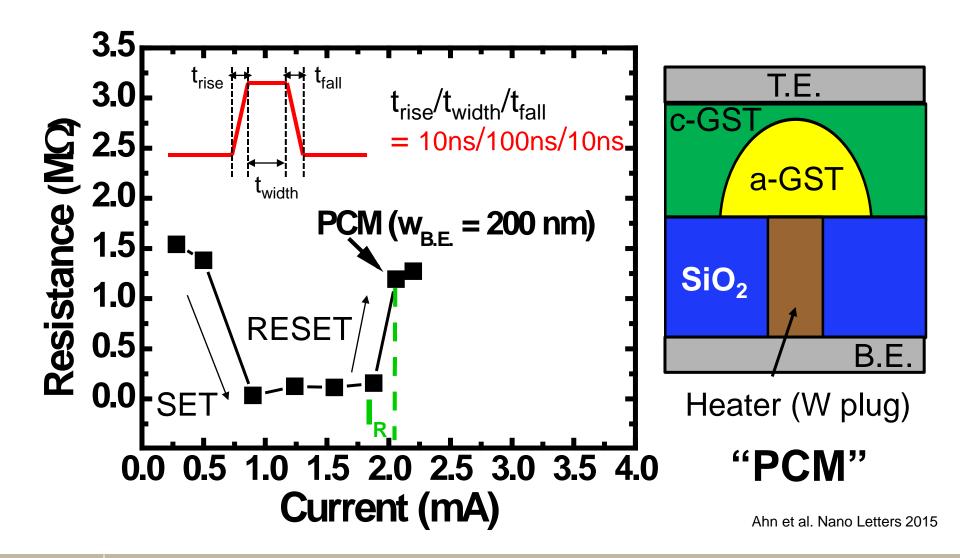

## <u>G-PCM</u>: I<sub>RESET</sub> of traditional PCM

Stanford University

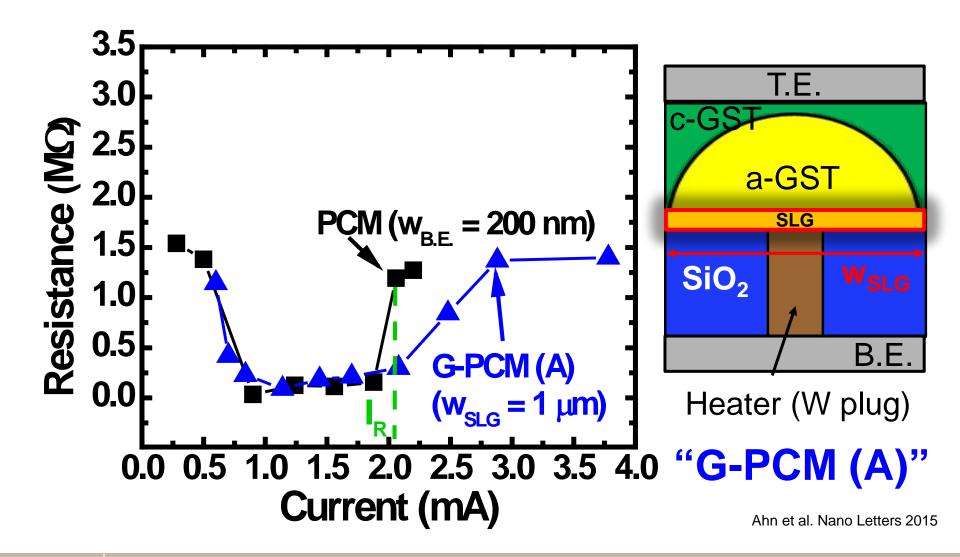

#### <u>G-PCM</u>: I<sub>RESET</sub> of GPCM (A) – Control sample

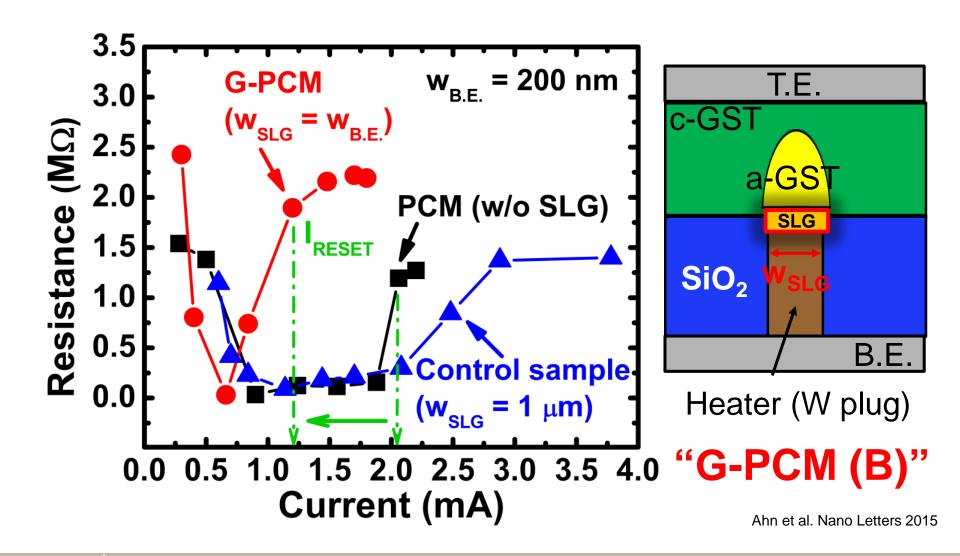

## <u>G-PCM</u>: I<sub>RESET</sub> of GPCM (B) – Optimal design

Stanford University

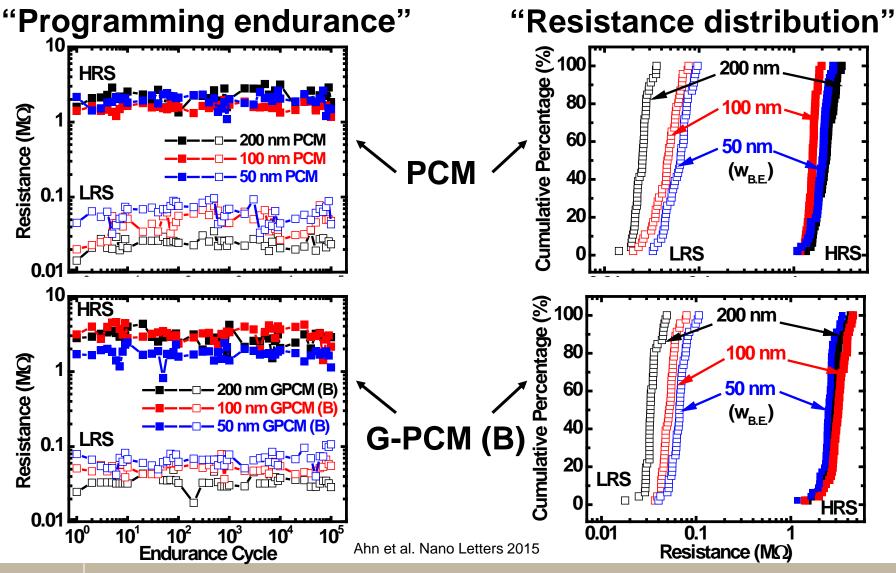

#### <u>G-PCM</u>: Verifying endurance is of great importance

2015.09.10.

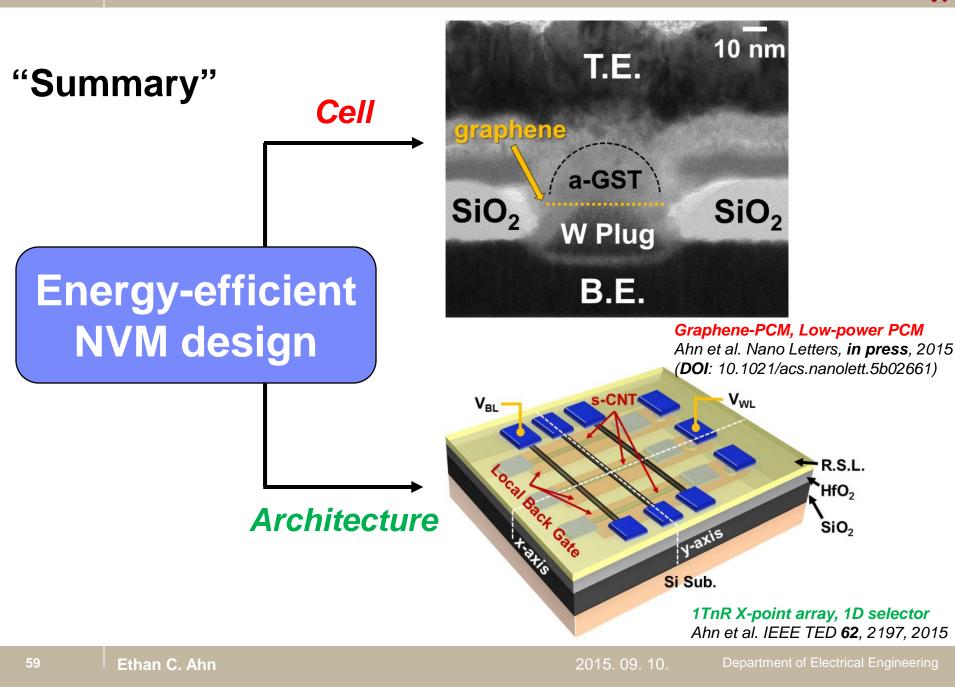

# 1. Energy-efficient <u>Cell</u> design

# 2. Energy-efficient Architecture design

July 2015

July 2015

s

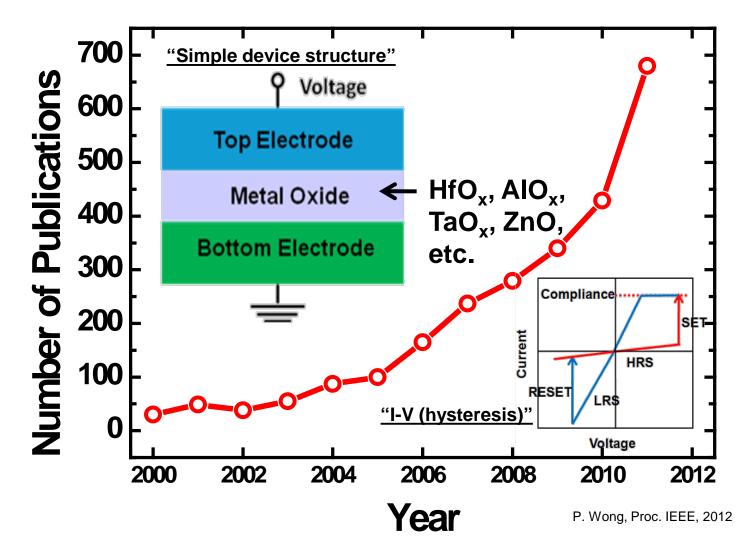

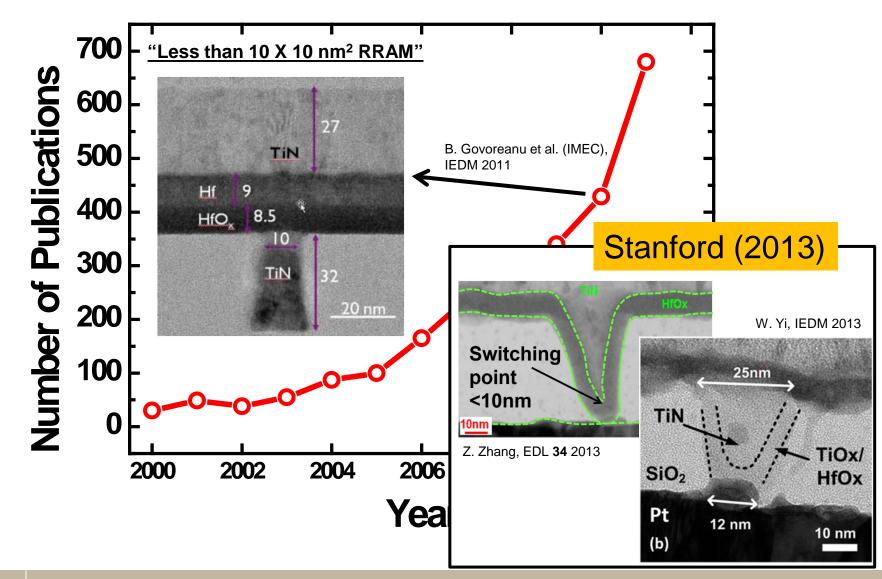

#### <u>RRAM</u>: **Emerging candidate** for sub-10 nm NVM

5

#### RRAM: Emerging candidate for sub-10 nm NVM

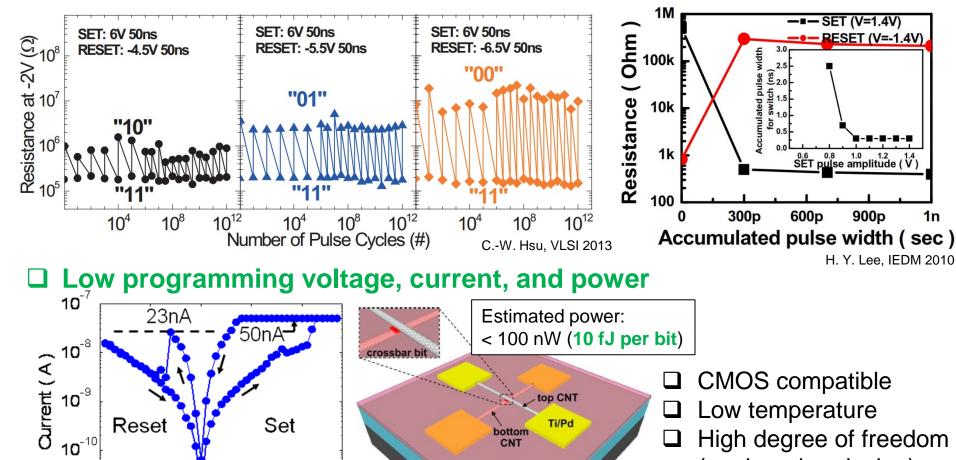

# RRAM: Key attributes (electrical performance)

#### □ High endurance (> 10<sup>12</sup> cycles) with MLC

AIO<sub>x</sub> SiO<sub>2</sub>

Si

(engineering design)

High speed (< 1 ns)

2015.09.10.

C.-L. Tsai, ACS Nano 7, 2013

10<sup>-11[</sup>-2

-1

Ethan C. Ahn

0

1

2

Voltage (V) W. Kim, VLSI 2011

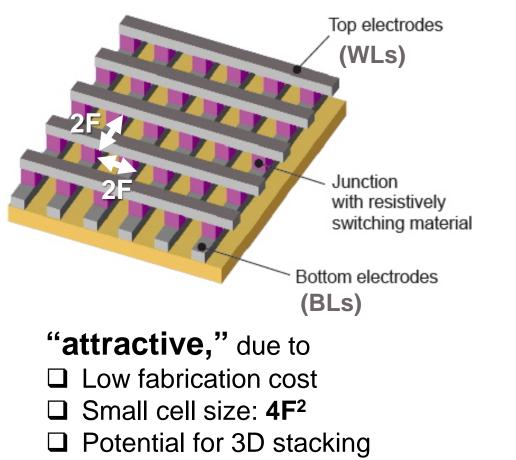

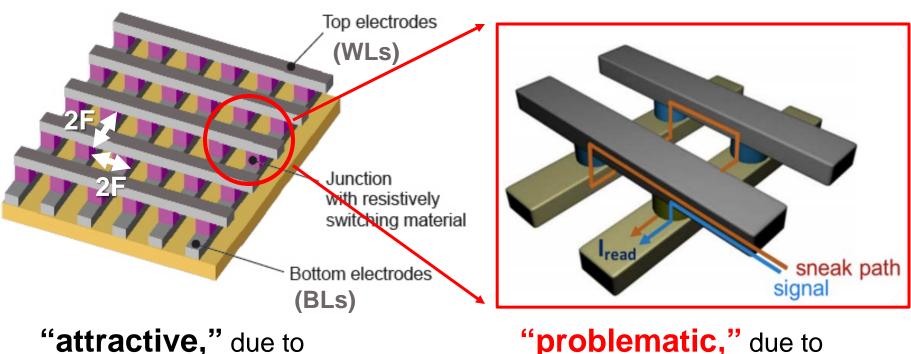

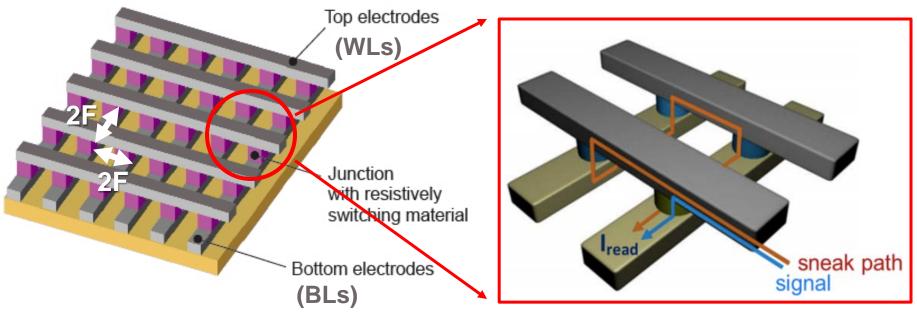

#### RRAM array: Cross-point structure

$(4F^2/N, N = number of layers)$

#### RRAM array: Cross-point structure

- Low fabrication cost

- □ Small cell size: 4F<sup>2</sup>

- Potential for 3D stacking  $(4F^2/N, N = number of layers)$

# "problematic," due to

#### Sneak path problem

- Increased power consumption

- Reduced write/read margin (limiting maximum allowable array size)

#### "attractive," due to

- Low fabrication cost

- □ Small cell size: 4F<sup>2</sup>

- Potential for 3D stacking  $(4F^2/N, N = number of layers)$

#### "problematic," due to

#### We need "Selection Device" to cut-off sneak leakage current

(limiting maximum allowable array size)

### "What selector will be the best choice for you?"

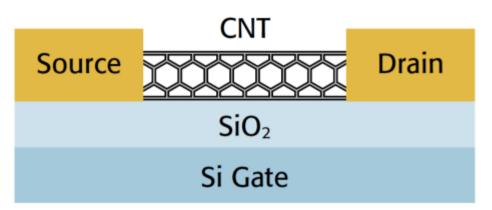

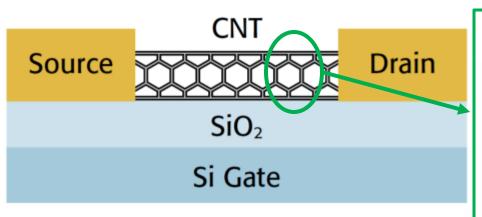

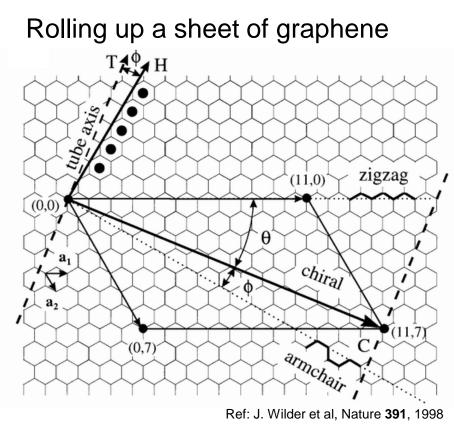

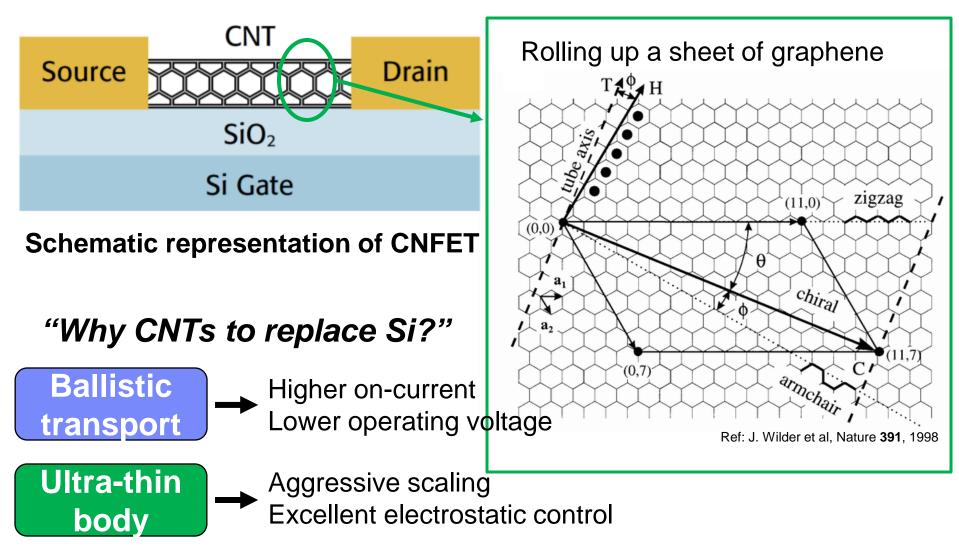

### Carbon nanotube field-effect transistors (CNFETs)

#### Schematic representation of CNFET

### Carbon nanotube field-effect transistors (CNFETs)

#### Schematic representation of CNFET

### Carbon nanotube field-effect transistors (CNFETs)

44

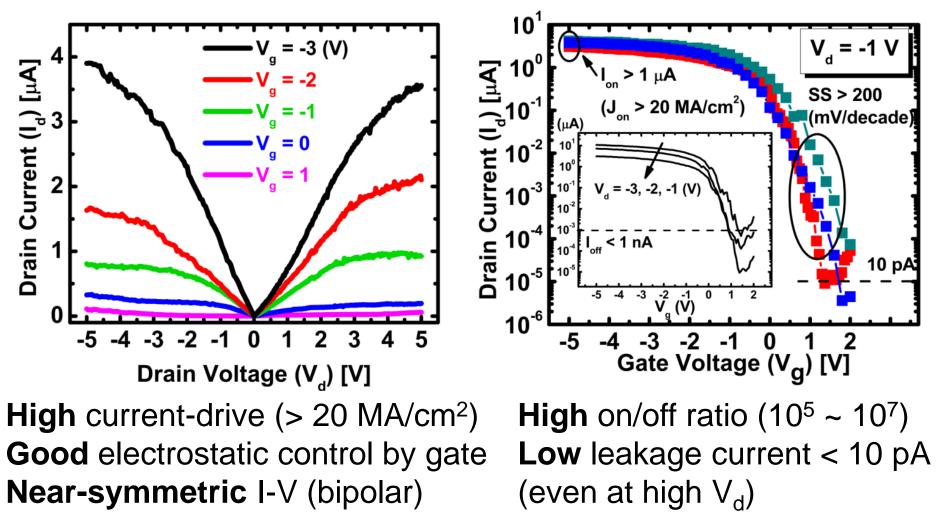

# **<u>CNFET</u>: Ideal selection device for memory array**

## □ High forward-current (I<sub>on</sub>) densities (J<sub>on</sub>)

to program aggressively scaled memory device  $J_{on} > 10 \text{ MA/cm}^2$

# □ High On/off ratio (I<sub>on</sub>/I<sub>off</sub>)

to have high selectivity of memory bits  $I_{on}/I_{off} > 10^{6}$

#### Low off-current (I<sub>off</sub>)

to accommodate un- and half-selected cells

$I_{off} < 10 \text{ pA}$

#### Low processing temperature (T)

to allow 3D stacking T < 300 °C

#### □ Bipolar operation

to allow for best-of-breed RRAM Symmetric I-V at both polarities

# + "small device area"

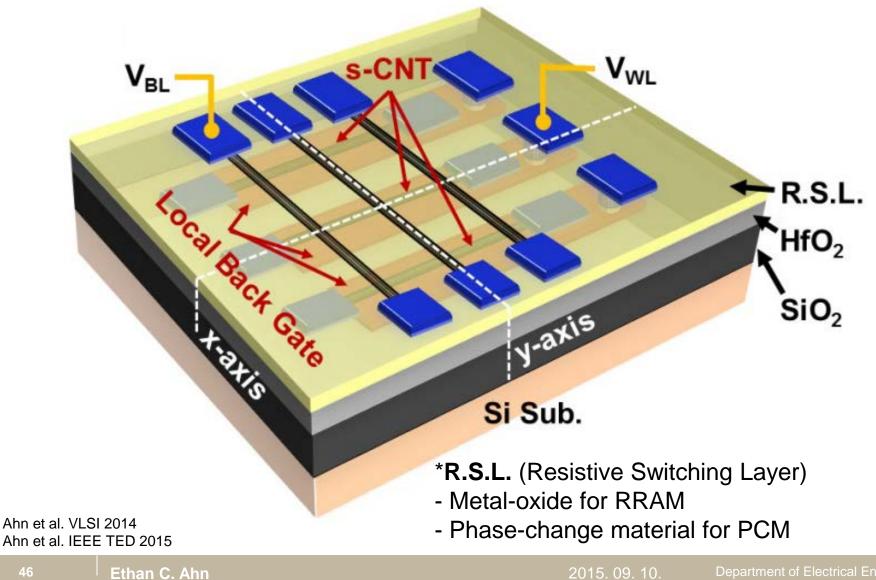

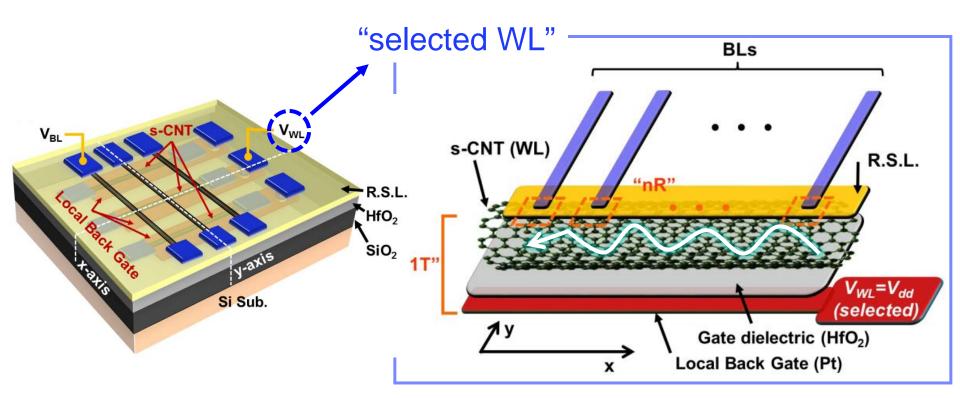

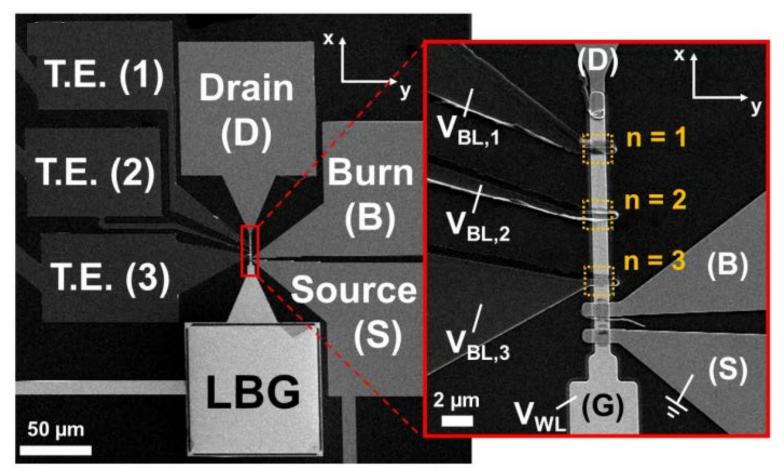

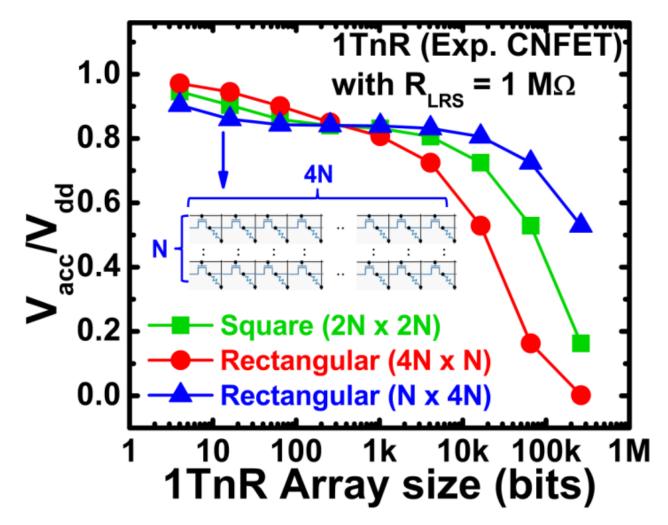

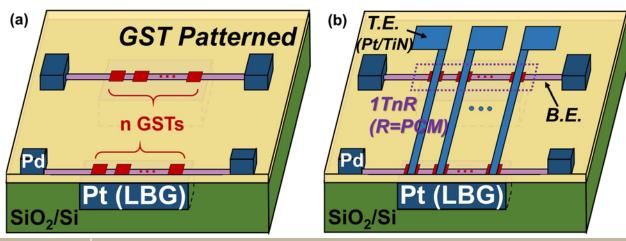

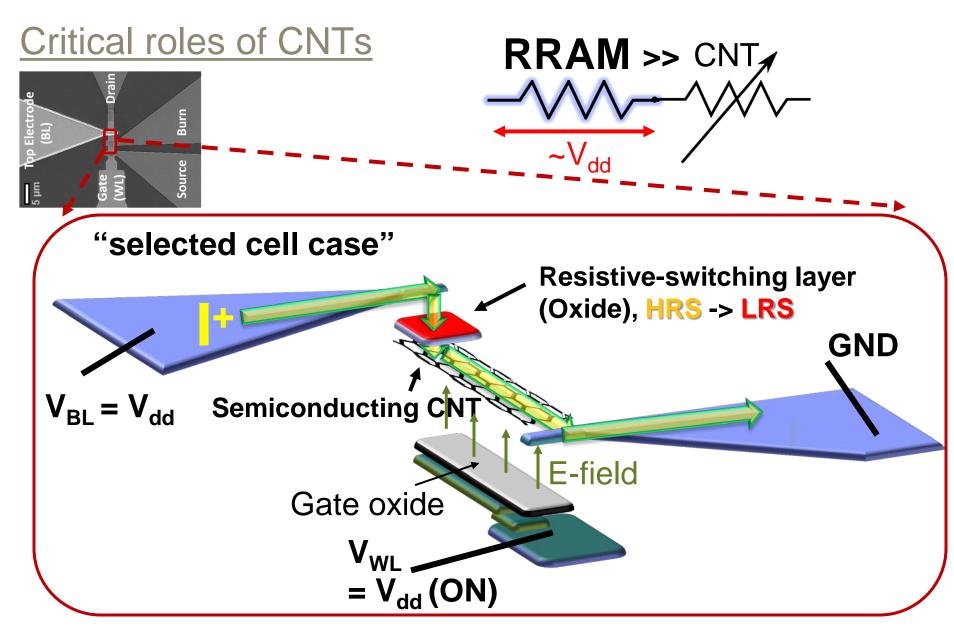

### **<u>1TnR array</u>: Based on CNFET selection device**

2015.09.10.

#### 1TnR array: Reduced sneak leakage

#### "Sneak leakage is much reduced from 2D to 1D," as it is confined within the 1D CNT channel

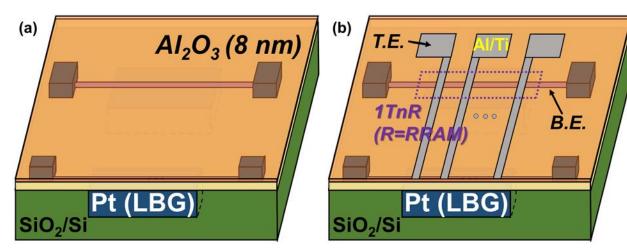

# <u>1TnR:</u> (1) Requires NO additional contacts/wiring

#### "CNFET selector is tightly integrated, with CNT as B.E."

### 1TnR: (2) Rectangular array preferred

### Electrical results: IVs of fabricated CNFETs

### Integration: CNFET + Memory = 1TnR

#### "Integrating with Al<sub>2</sub>O<sub>3</sub>-based RRAM"

#### "Integrating with PCM (GST)"

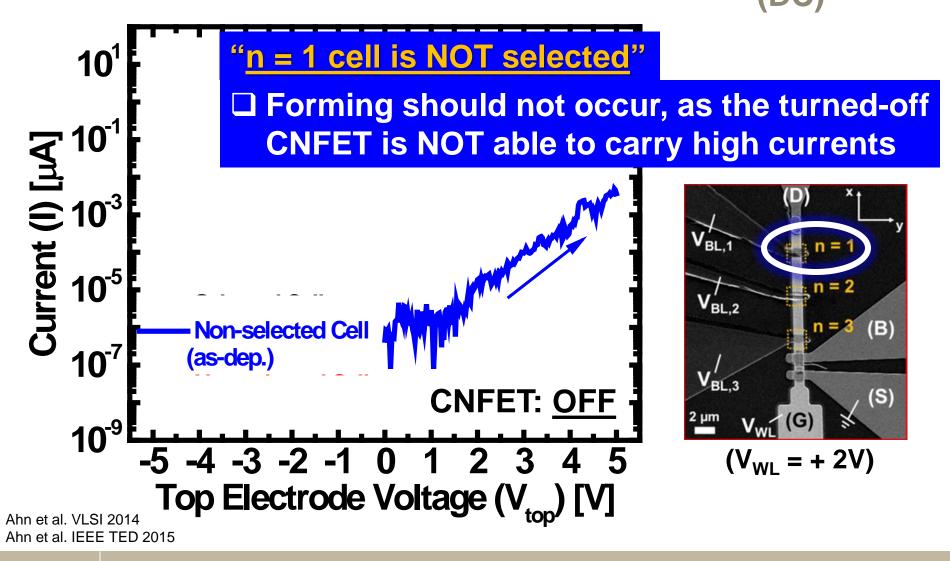

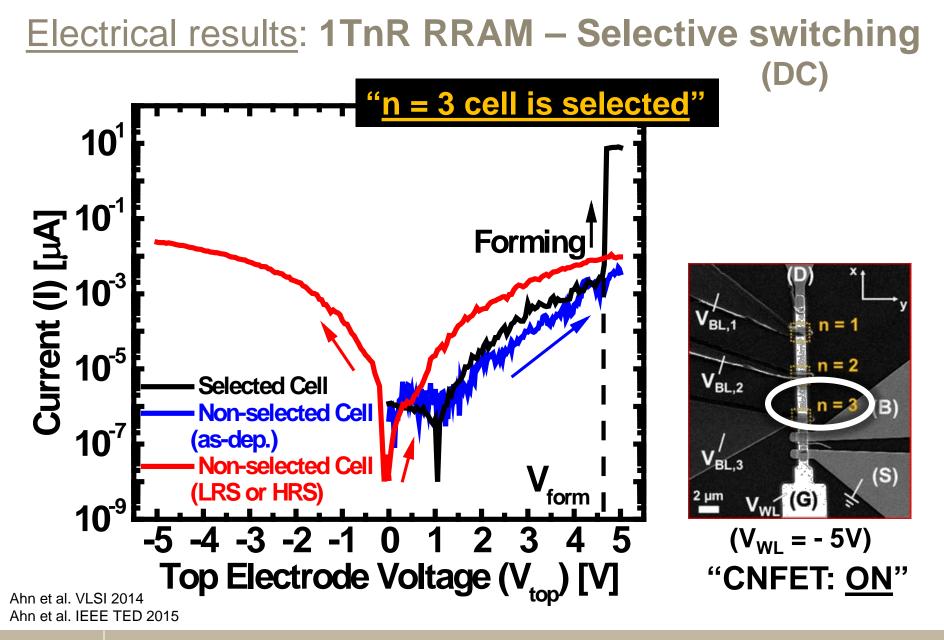

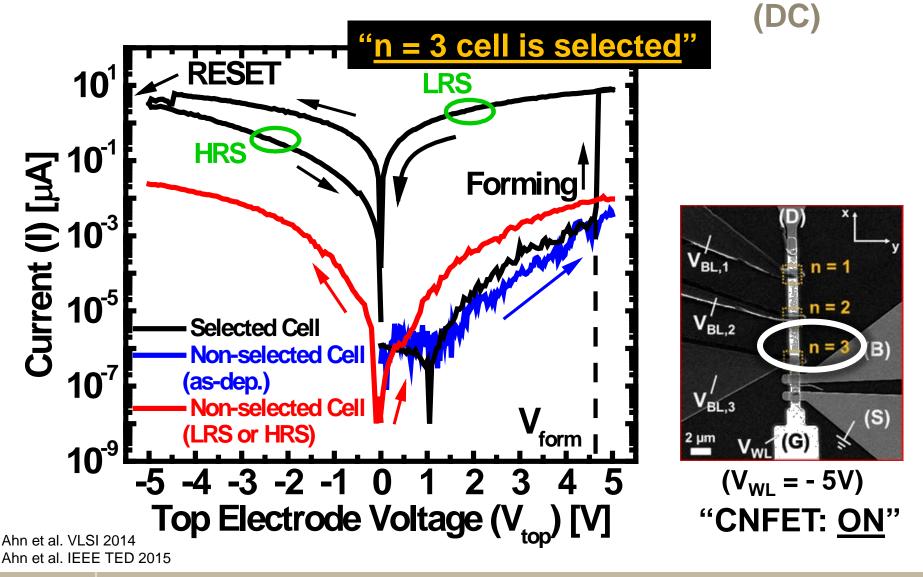

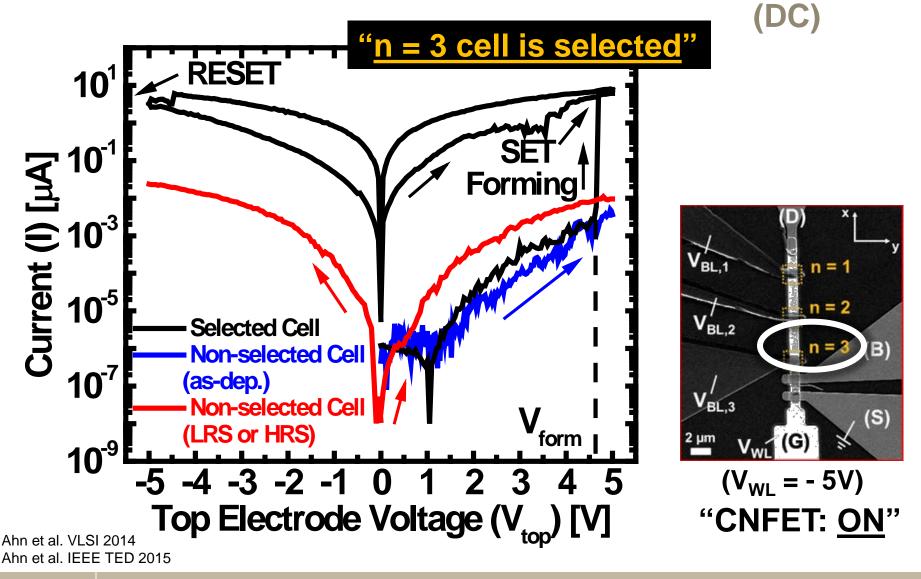

#### Electrical results: 1TnR RRAM – Selective switching (DC)

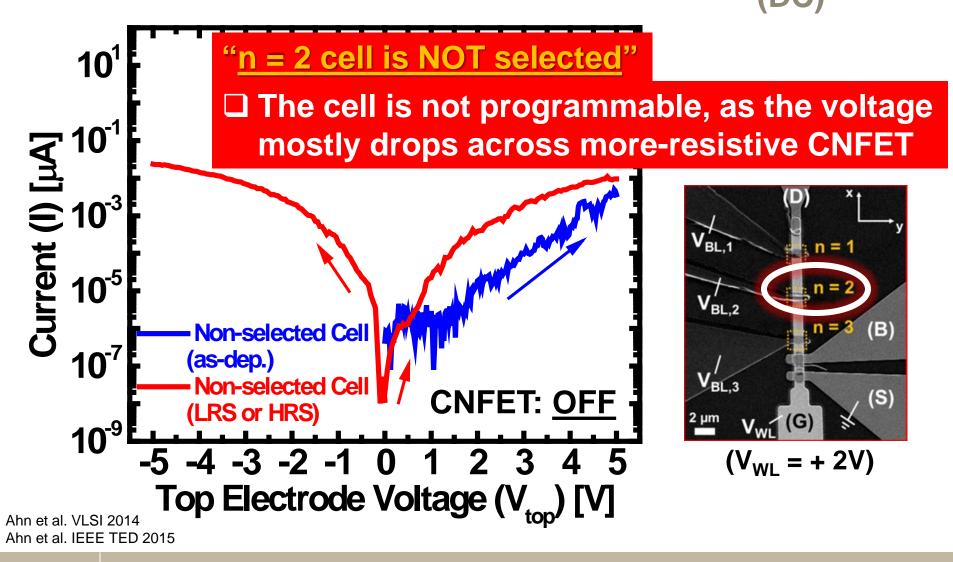

# Electrical results: 1TnR RRAM – Selective switching

# Electrical results: 1TnR RRAM – Selective switching

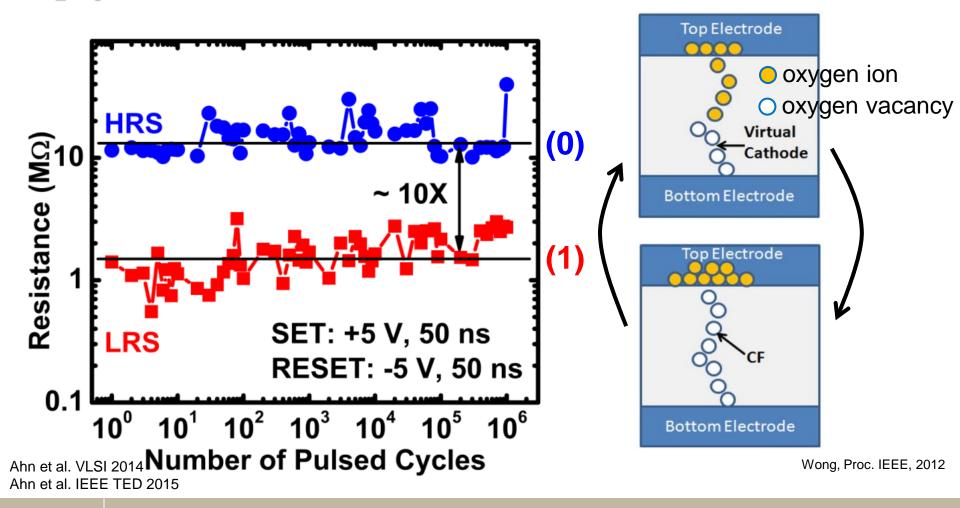

### Electrical results: 1TnR RRAM – Pulsed endurance

$Al_2O_3$  RRAM  $\rightarrow$  Low programming power  $\rightarrow$  Size of CF: small

#### "Take home"

High-density (low-cost) RRAM storage? Ultra-low power microchip?

Graphene/CNT interconnects?

Google smart contact lens