# A DISRUPTOR TO THE SEMICONDUCTOR INDUSTRY

# **THE MONOLITHIC 3D-IC**

# Agenda:

- The Semiconductor future is exciting

- But we are reaching an inflection point

- Monolithic 3D IC the emerging path for the next generation technology driver

- The challenge and solution for the fabrication of monolithic 3D IC

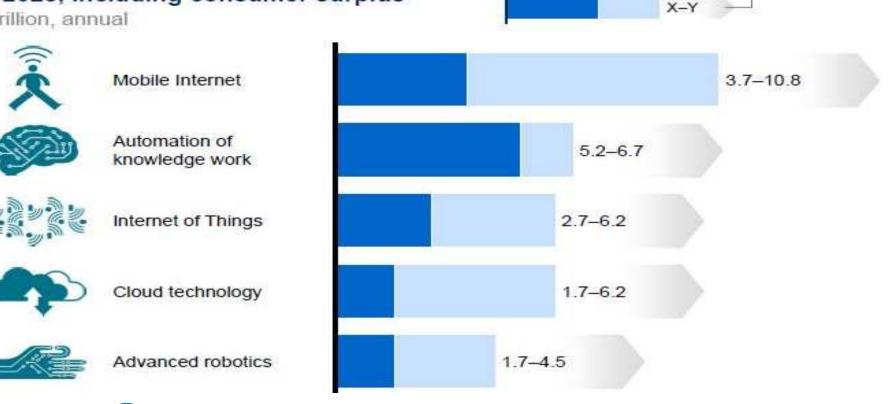

# \$15-34 trillion, annual =>~\$5T Semi /year

Range of sized potential

High

economic impacts

Low

Impact from other

(not sized)

potential applications

#### Exhibit E3

Estimated potential economic impact of technologies from sized applications in 2025, including consumer surplus

\$ trillion, annual

Source: McKinsey Global Institute Analysis 2013

# Cisco sees \$19 Trillion opportunity in IoT

"CES LIVE: Cisco's Chambers Says Internet of Everything, \$19 Trillion Opportunity, Is Next Big Thing" 1/7/14 <ttp://www.forbes.com/sites/connieguglielmo/2014/01/07/ces-live-cisco-ceo-chambers-to-deliver-keynote/>

\$19 trillion: that's the opportunity he says for the Internet of Everything in the private and public sector combined. Breakout is \$14.4 trillion in private sector and \$4.6 trillion in public sector of new revenue generation or new savings. That's a conservative number he says for public sector."This will be bigger than anything done in high tech in a decade."

"As many as 50 billion devices will be connected to the Internet by 2020, creating a \$14.4 trillion business opportunity" said Rob Lloyd, president of sales and development at Cisco, <<u>http://www.eetimes.com/electronics-news/4409928/Cisco-sees--14-trillion-opportunity-in-Internet-of-Things</u>>

# Semiconductor Industry is Facing an Inflection Point

**Dimensional Scaling has reached Diminishing Returns**

### The Current 2D-IC is Facing Escalating Challenges - I

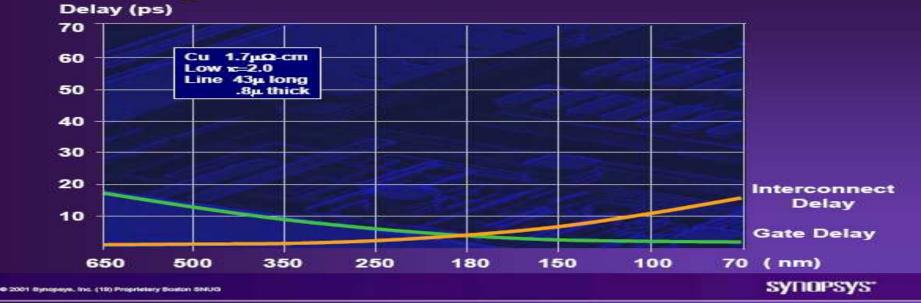

### On-chip interconnect is

- Dominating device power consumption

- Dominating device performance

- Penalizing device size and cost

#### Interconnect Delay Creates the Timing Closure Problem

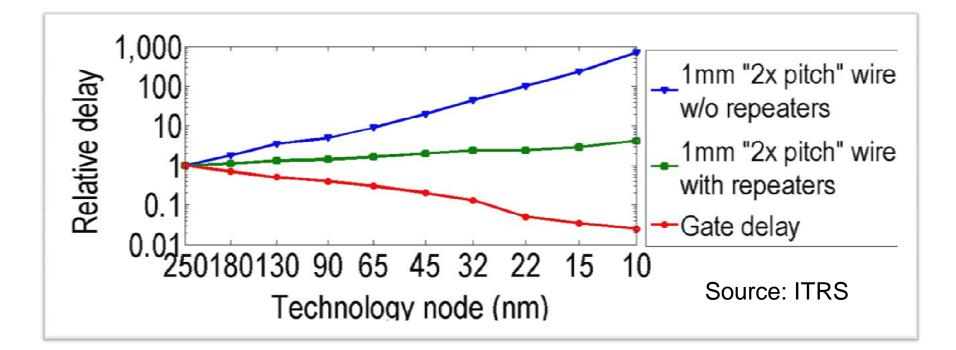

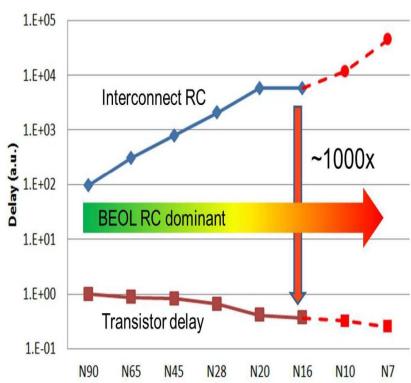

# Interconnect Delay A Big Issue with Scaling

- > Transistors improve with scaling, interconnects do not

- Even with repeaters, 1mm wire delay ~50x gate delay at 22nm node

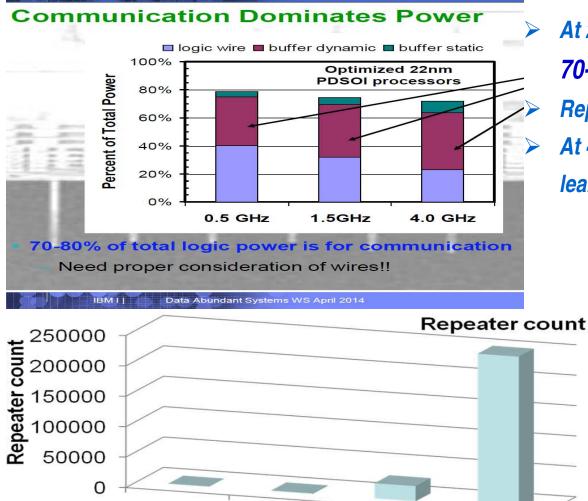

### Connectivity Consumes 70-80% of Total Power @ 22nm Repeaters Consume Exponentially More Power and Area

90nm

65nm

45nm

130nm

IBM Research

At 22nm, on-chip connectivity consumes 70-80% of total power Repeater count increases exponentially At 45nm, repeaters are > 50% of total leakage

> Source: IBM POWER processors R. Puri, et al., SRC Interconnect Forum, 2006

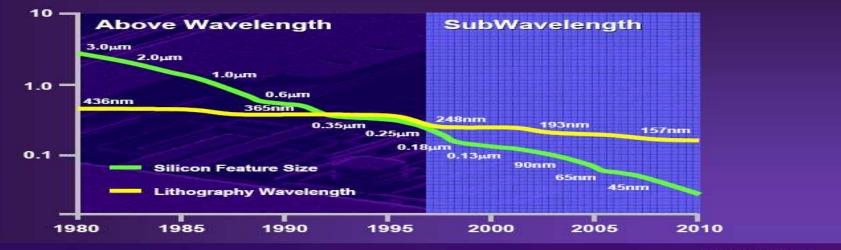

### The Current 2D-IC is Facing Escalating Challenges - II

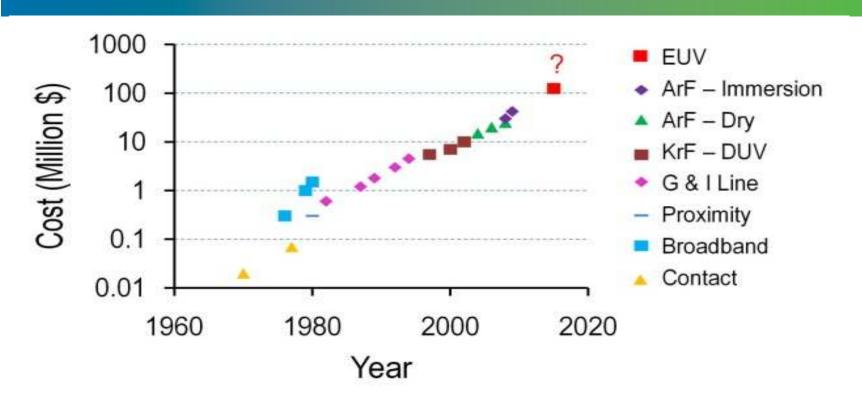

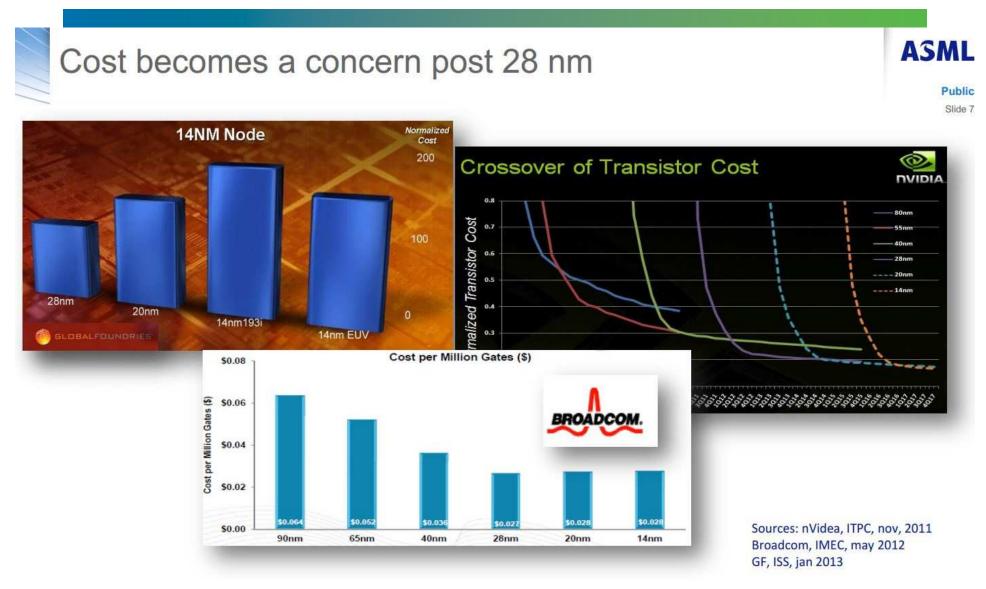

### Lithography is

- Dominating Fab cost

- Dominating device cost and diminishing scaling's benefits

- Dominating device yield

- Dominating IC development costs

#### Subwavelength Lithography Challenge

© 2001 Synapsys, Inc. (1) CONFIDENTIAL

# A Challenge: Lithography

- Quad-patterning next year  $\rightarrow$  costly. EUV delayed, costly.

- Can we get benefits of scaling <u>without relying on lithography</u>?

### Martin van den Brink - EVP & CTO, ASML ISSCC 2013 & SemiconWest 2013

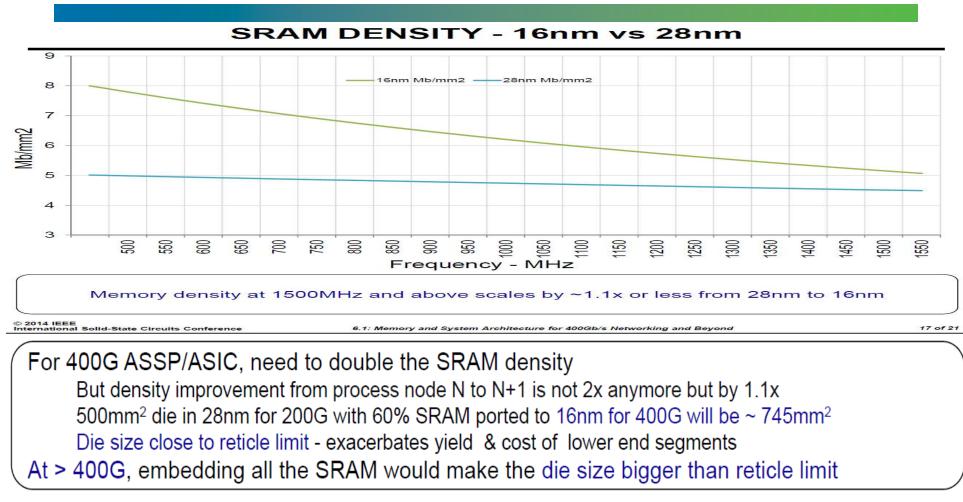

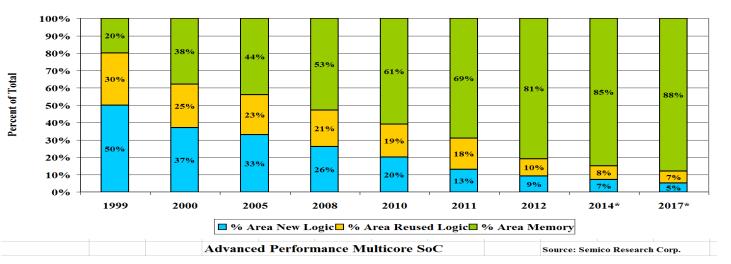

### Embedded SRAM isn't Scaling Beyond 28nm (1.1x instead off 4x) eSRAM > 60% of Die Area => End of Dimension Scaling !

© 2014 IEEE International Solid-State Circuits Conference

6.1: Memory and System Architecture for 400Gb/s Networking and Beyond

18 of 21

Dinesh Maheshwari, CTO, Memory Products Division at Cypress Semiconductors, ISSCC2014

### Embedded SRAM isn't Scaling Beyond 28nm eSRAM > 60% of Die Area => End of Dimensional Scaling !

| * | Early production          | 2011 - 2012<br>22 - 20nm | 2013 - 2014<br>16 -14nm | 2015 - 2016<br>10nm | 2017 - 2018<br>7nm     | 2019<br>5nm             |

|---|---------------------------|--------------------------|-------------------------|---------------------|------------------------|-------------------------|

|   |                           |                          |                         |                     |                        |                         |

| N | Memory (um <sup>2</sup> ) | SRAM 0.09-0.08           | SRAM 0.08-0.07          | SRAM 0.06-0.05      | SRAM < 0.05;           | SRAM < 0.05; (STT-MRAM) |

| C | Device                    | Planar, FinFET           | FinFET, FDSOI           | FINFET              | FinFET; (LOCSOI, GAA)  | GAA FINFET; (NW)        |

| C | Gate EOT (nm)             | HKMG 0.9                 | HKMG 0.8                | HKMG 0.7            | HKMG 0.7               | HKMG 0.7                |

|   | Channel n/p               | Si                       | Si / SiGe               | Si / (SiGe)         | Si / SiGe; (IIIV / Ge) | Si / SiGe; (IIIV / Ge)  |

| s | i/D Strain                | yes                      | yes                     | yes                 | yes                    | yes                     |

|   | /dd (V)                   | 0.8                      | 0.8                     | 0.8-0.7             | 0.7-0.5                | 0.7-0.5                 |

\*<u>imec's 2013</u> International Technology Forum,

# Moore's Law Dead by 2022\* Bob Colwell, Director MTO, DARPA

My model: During and After Moore's Law

- 1. COTS is both problem & opportunity for DoD for next 10 years.

- 2. Then COTS stalls out. (But DoD doesn't have to!)

| 1968 | 2012                     | 2020 |                                                 | 2030                                 |

|------|--------------------------|------|-------------------------------------------------|--------------------------------------|

|      | Moore's Law<br>in effect | 1    | Post-Moore's Law<br>specialization &<br>cleanup | New switch?<br>Back to the<br>races! |

|      | Better, cheaper, faster  |      | aster bigger hotter<br>nd more expensive        |                                      |

|      | COTS is King             |      | COTS stalled                                    |                                      |

DARPA

\*http://www.eetimes.com/document.asp?doc\_id=1319330 \*CRA/CCC & ACM SIGDA, Pittsburgh, March 2013

# **Conclusions:**

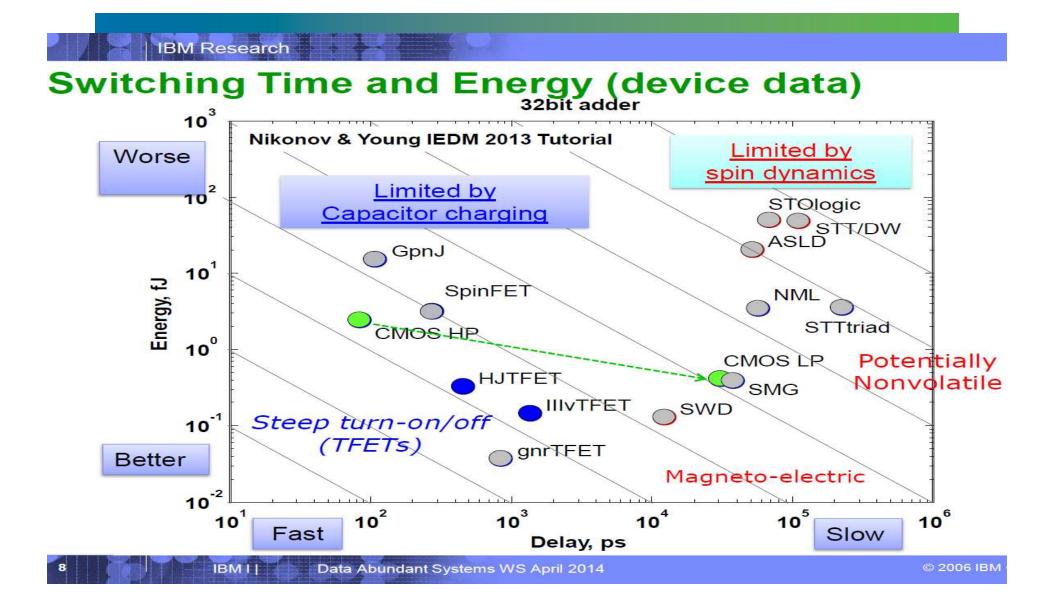

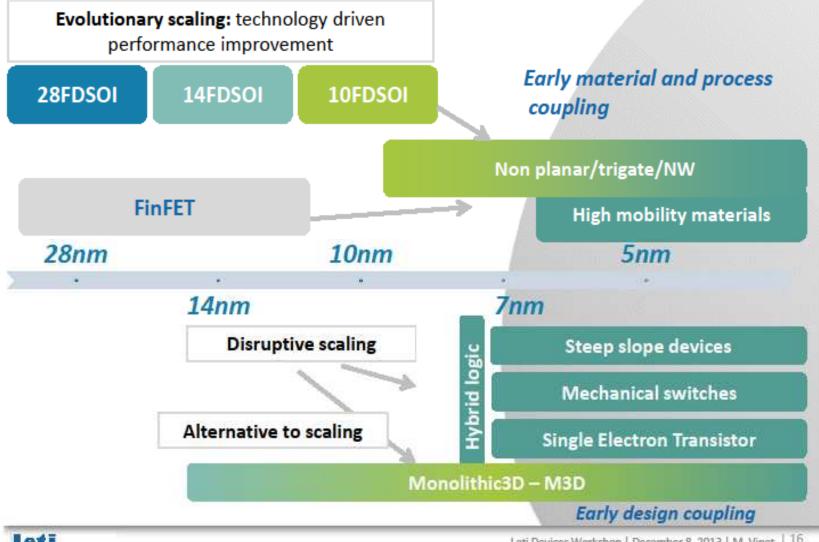

- Dimensional Scaling ("Moore's Law") is already exhibiting diminishing returns

- The road map beyond 2017 (7nm) is unclear

- > While the research community is working on many interesting new technologies (see below), none of them seem mature enough to replace silicon for 2019

- Carbon nanotube Indium gallium arsenide

- -'2D' devices: MoS2, etc

- Graphene

- Spintronics

- Nanowire

- Photonics

- Molecular computing

- Quantum computing

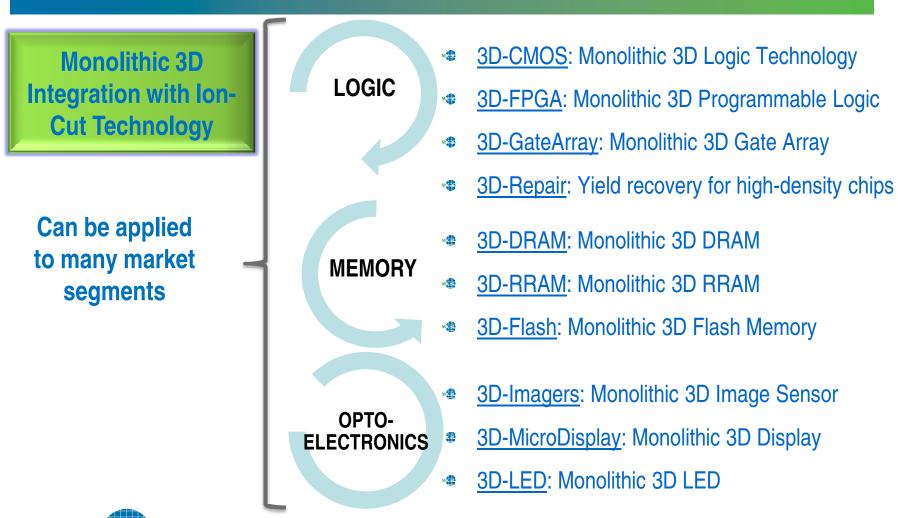

- 3D IC is considered, by all, as the near term solution, and Monolithic 3D **IC** is well positioned to be so, as it uses the existing infrastructure

- > It is safe to state that Monolithic 3D is the only alternative that could be ready for high volume in 2019

# **CMOS** is the Best Device Option

# 3D and EDA need to make up for Moore's Law, says Qualcomm\*

- "Qualcomm is looking to monolithic 3D and smart circuit architectures to make up for the loss of traditional 2D process scaling as wafer costs for advanced nodes continue to increase. .. Now, although we are still scaling down it's not cost-economic anymore"

- Interconnect RC is inching up as we go to deeper technology. That is a major problem because designs are becoming interconnect-dominated. Something has to be done about interconnect. What needs to be done is monolithic three-dimensional ICs."

- "TSV...are not really solving the interconnect issue I'm talking about.

So we are looking at true monolithic 3D. You have normal vias between different stacks."

\* Karim Arabi Qualcomm VP of engineering Key Note DAC 2014 <http://www.techdesignforums.com/blog/2014/06/05/karim-arabi-monolithic-3dic-dac-2014/>

### "CEA-Leti Signs Agreement with Qualcomm to Assess Sequential (monolithic)3D Technology"

Business Wire December 08, 2013

Fig. 17: BEOL performance/area/cost scaling is the foremost issue for 10nm/7nm nodes.

"Monolithic 3D (M3D) is an emerging integration technology poised to reduce the gap significantly between transistors and interconnect delays to extend the semiconductor roadmap way beyond the 2D scaling trajectory predicted by Moore's Law."

Geoffrey Yeap, VP of Technology at Qualcomm, Invited paper, IEDM 2013

### **Device technology roadmap**

Leti Devices Workshop | December 8, 2013 | M. Vinet | 16

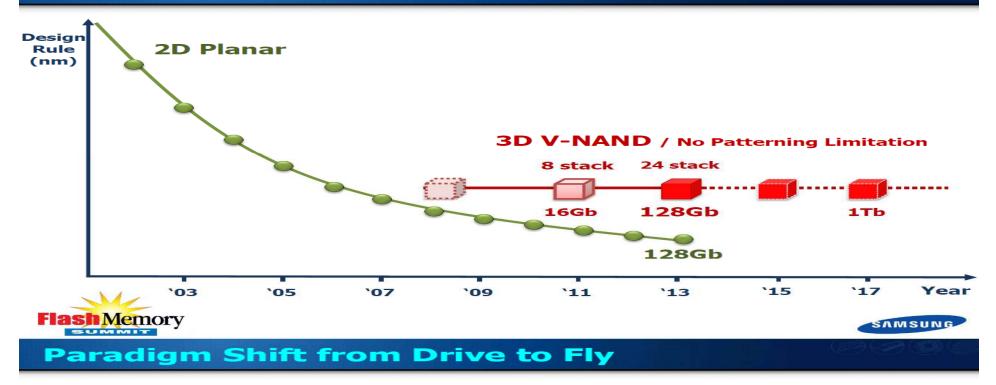

#### **V-NAND Era for the Future**

Innovative Technology

- Material

- Structure

- Integration

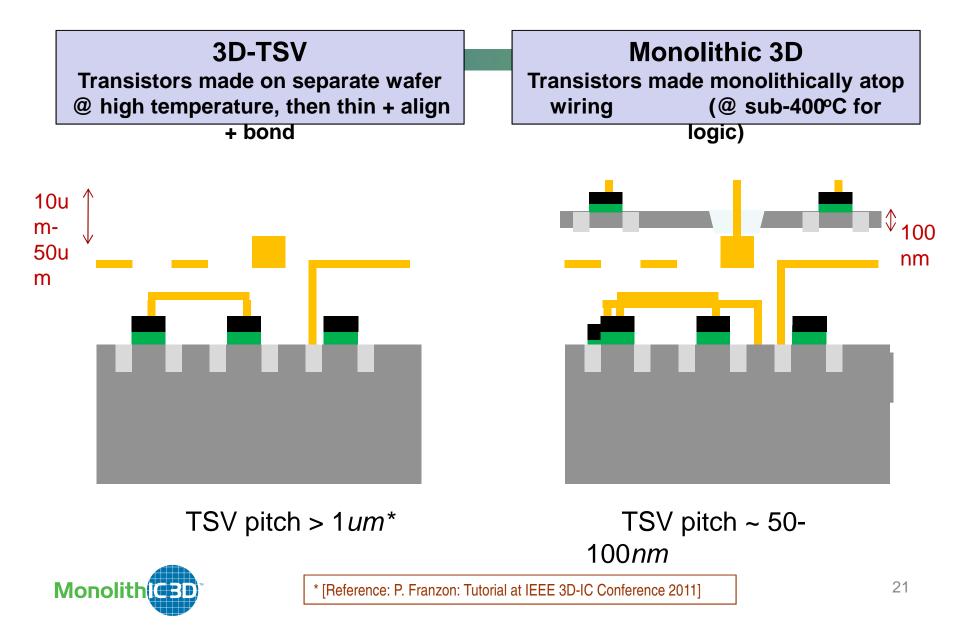

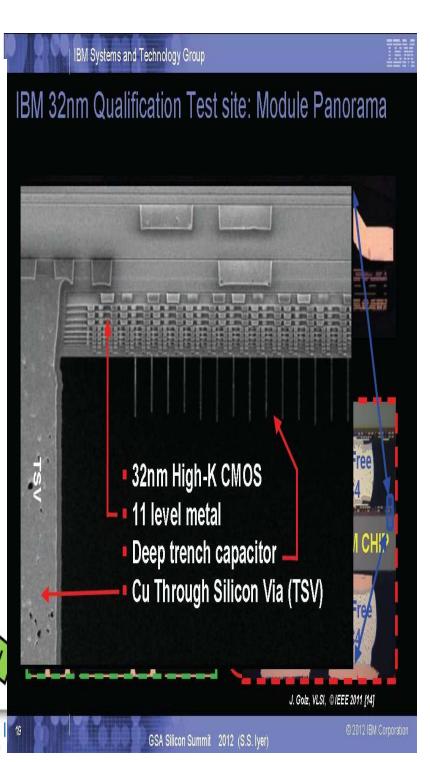

# Two Types of 3D Technology

# **MONOLITHIC**

# 10,000x the Vertical Connectivity of TSV

| Enables:                             | TSV     | Monolithic  |

|--------------------------------------|---------|-------------|

| Layer<br>Thickness                   | ~50µ    | ~50nm       |

| Via Diameter                         | ~5µ     | ~50nm       |

| Via Pitch                            | ~10µ    | ~100nm      |

| Wafer (Die) to<br>Wafer<br>Alignment | ~1µ     | ~1nm        |

| Overall<br>Scale                     | microns | nano-meters |

# Monolithic/ Sequential 3D

• Wafers Processed separately

Stacking and Contacting

1 TSV/ Block of 10,000 FETs

TSV

TSV

Parallel

Bottom transistor processing

Top FET processing

- Contacting

- 1 vertical contact/ FET

Advances, Challenges and Opportunities in 3D CMOS Sequential Integration. P. Batude et al, IEDM 2011

> High density 3D integration solutions at the wafer scale. Scannell, CEA-Leti July 10<sup>th</sup>, 2012.

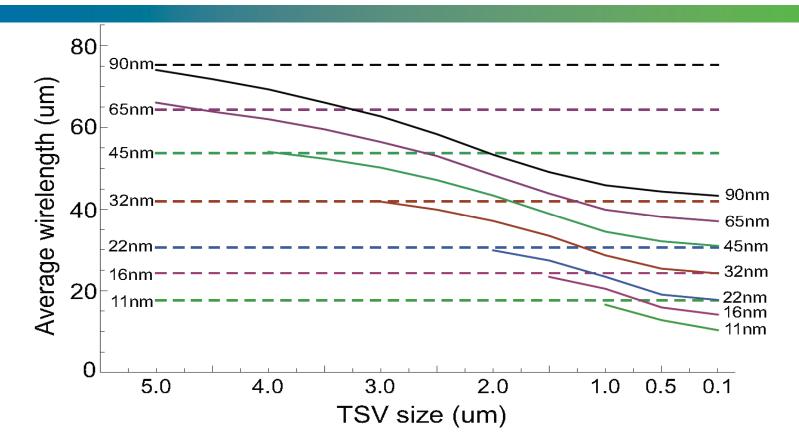

# 3D ICs in older process (65*nm*) is better than 2D ICs built with a newer process (32*nm*)

Fig. 6. Cross comparison among various 2D and 3D technologies. Dashed lines are wirelengths of 2D ICs. # dies: 4.

\*IEEE IITC11 Kim

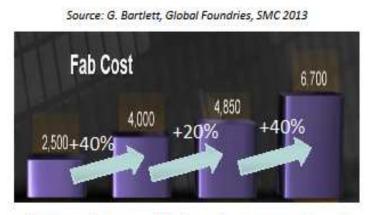

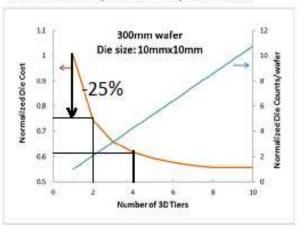

# **Interest for M3D**

Without scaling avoid fab and process costs increase

Source: R. Gilmore, Qualcomm VP, ESSIRC 2012

#### Stack 2 layers: 25% die cost reduction

Top metal Average gain layers 1 node gain benchmark for 6 Interlevel via CMOS without circuits/planar Interlevel scaling metal layers CMOS 3 metal levels

Leti Devices Workshop | December 8, 2013 | M. Vinet | 18

**The Monolithic 3D Challenge** Why is it not already in wide use?

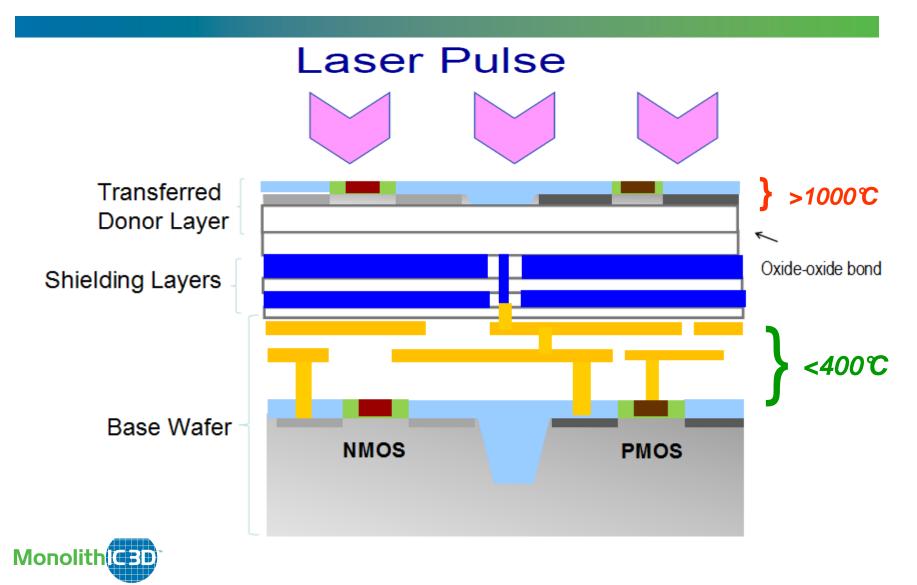

Processing on top of copper interconnects should not make the copper interconnect exceed 400°C

➢ How to bring mono-crystallized silicon on top at less than 400°C

How to fabricate state-of-the-art transistors on top of copper interconnect and keep the interconnect below at less than 400°C

Misalignment of pre-processed wafer to wafer bonding step is ~1um

➢ How to achieve 100nm or better connection pitch

➢ How to fabricate thin enough layer for inter-layer vias of ~50nm

# MonolithIC 3D – Breakthrough

### **3 Classes of Solutions (3 Generations of Innovation)**

- RCAT (2009) Process the high temperature on generic structures prior to 'smart-cut', and finish with cold processes – Etch & Depositions

- Gate Replacement (2010) (=Gate Last, HKMG) Process the high temperature on repeating structures prior to 'smartcut', and finish with 'gate replacement', cold processes – Etch & Depositions

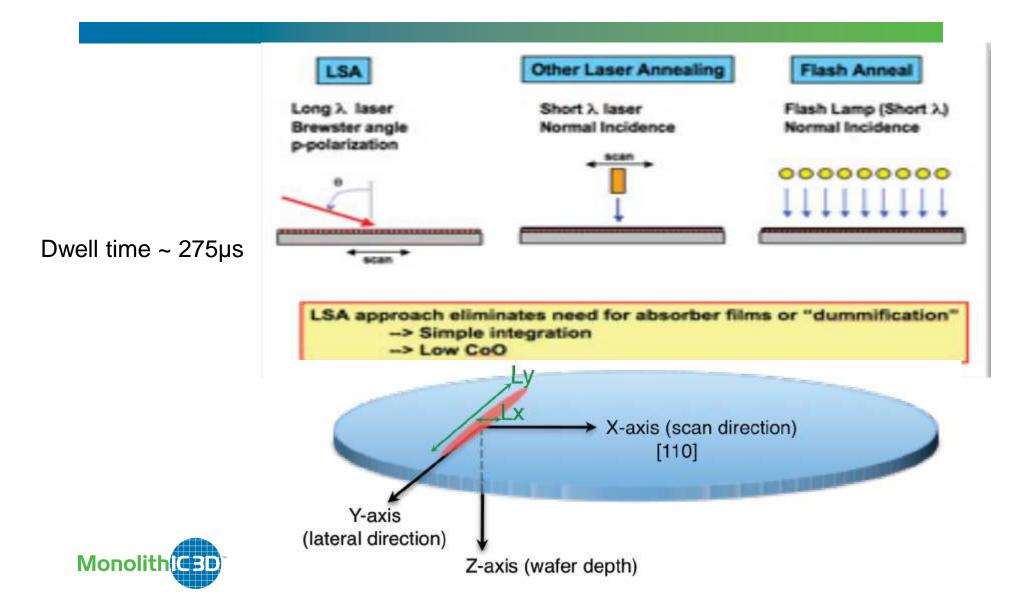

- Laser Annealing (2012) Use short laser pulse to locally heat and anneal the top layer while protecting the interconnection layers below from the top heat

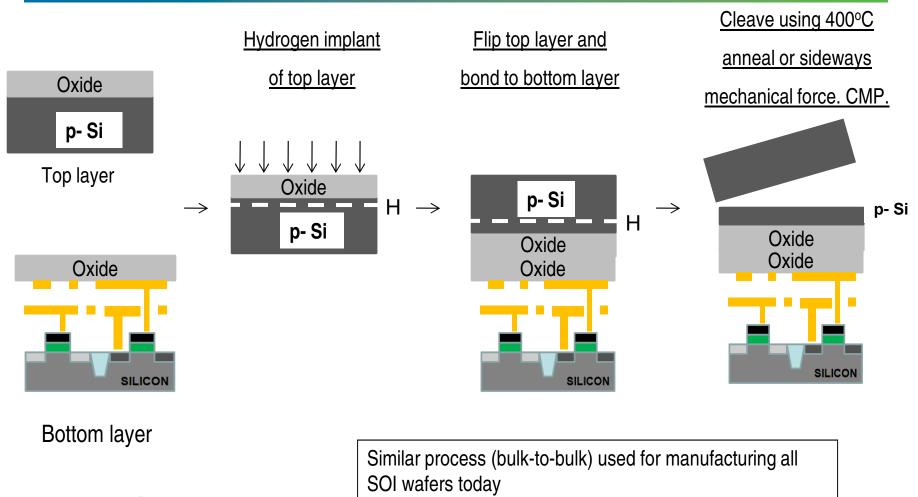

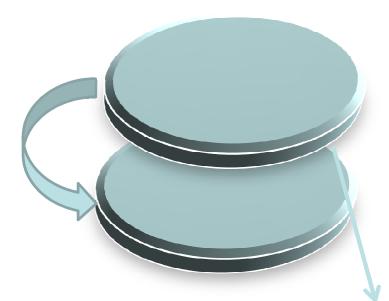

# Layer Transfer ("Ion-Cut"/"Smart-Cut") → The Technology Behind SOI

# MonolithIC 3D - 3 Classes of Solutions

- RCAT Process the high temperature on generic structure prior to 'smart-cut', and finish with cold processes – Etch & Depositions

- Gate Replacement (=Gate Last, HKMG) Process the high temperature on repeating structure prior to 'smart-cut', and finish with 'gate replacement', cold processes – Etch & Depositions

- Laser Annealing Use short laser pulse to locally heat and anneal the top layer while protecting the interconnection layers below from the top heat

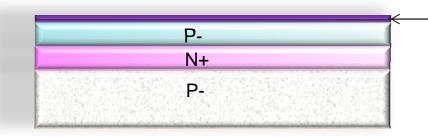

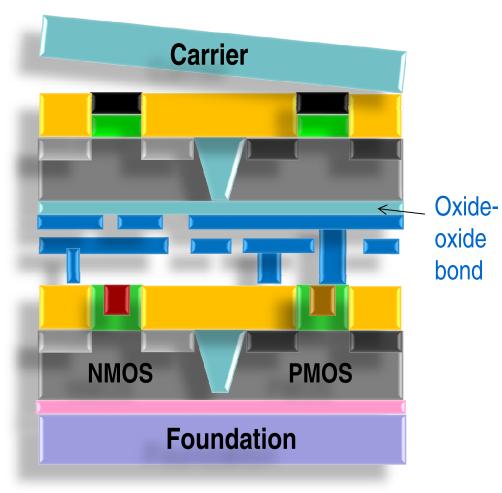

### **Step 1. Donor Layer Processing**

<u>Step 1</u> - Implant and activate unpatterned N+ and P- layer regions in standard donor wafer at high temp. (~900°C) before layer transfer. Oxidize (or CVD oxide) top surface.

SiO<sub>2</sub> Oxide layer (~100nm) for oxide -to-oxide bonding with device wafer.

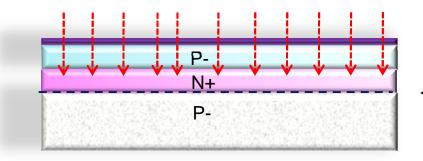

Step 2 - Implant H+ to form cleave plane for the ion cut

H+ Implant Cleave Line in N+ or below

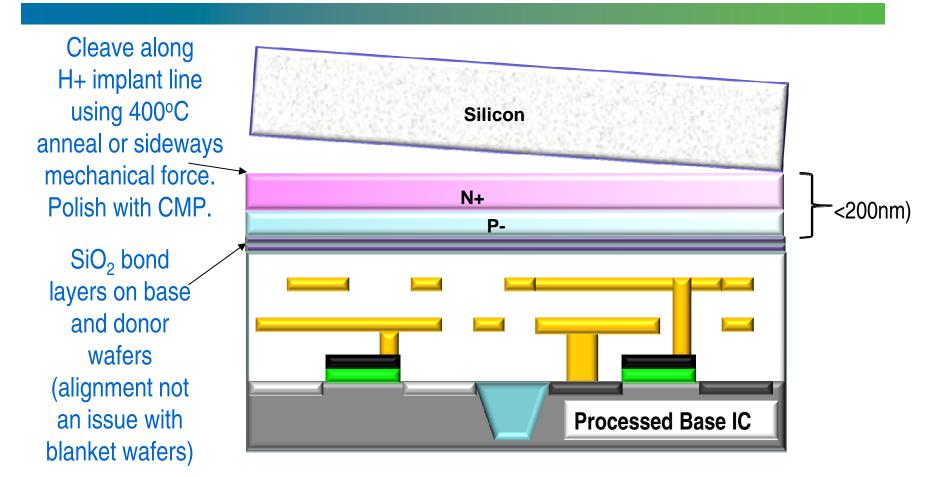

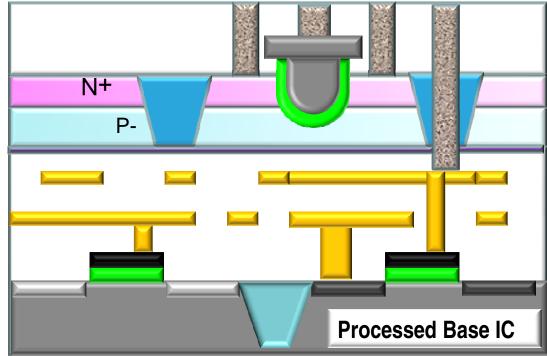

# Step 3 - Bond and Cleave: Flip Donor Wafer and Bond to Processed Device Wafer

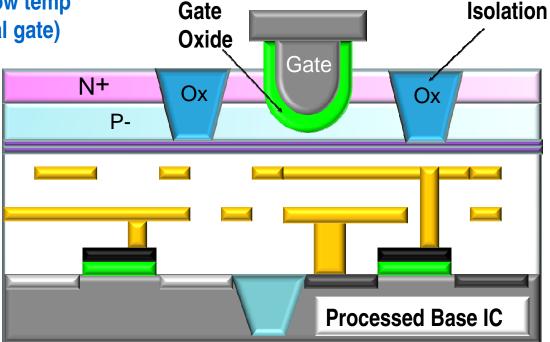

### **Step 4 - Etch and Form Isolation and RCAT Gate**

Litho patterning with features aligned to bottom layer

Etch shallow trench isolation (STI) and gate structures

Deposit SiO<sub>2</sub> in STI

Grow gate with ALD, etc. at low temp (<350° C oxide or high-K metal gate)</li>

<u>Advantage:</u> Thinned donor wafer is transparent to litho, enabling direct alignment to device wafer alignment marks: no indirect alignment. (common for TSV 3DIC)

# **Step 5 – Etch Contacts/Vias to Contact the RCAT**

- > Complete transistors, interconnect wires on 'donor' wafer layers

- Etch and fill connecting contacts and vias from top layer aligned to bottom layer

# MonolithIC 3D - 3 Classes of Solutions

- RCAT Process the high temperature on generic structure prior to 'smart-cut', and finish with cold processes – Etch & Depositions

- Gate Replacement (=Gate Last, HKMG) Process the high temperature on repeating structure prior to 'smart-cut', and finish with 'gate replacement', cold processes – Etch & Depositions

- Laser Annealing Use short laser pulse to locally heat and anneal the top layer while protecting the interconnection layers below from the top heat

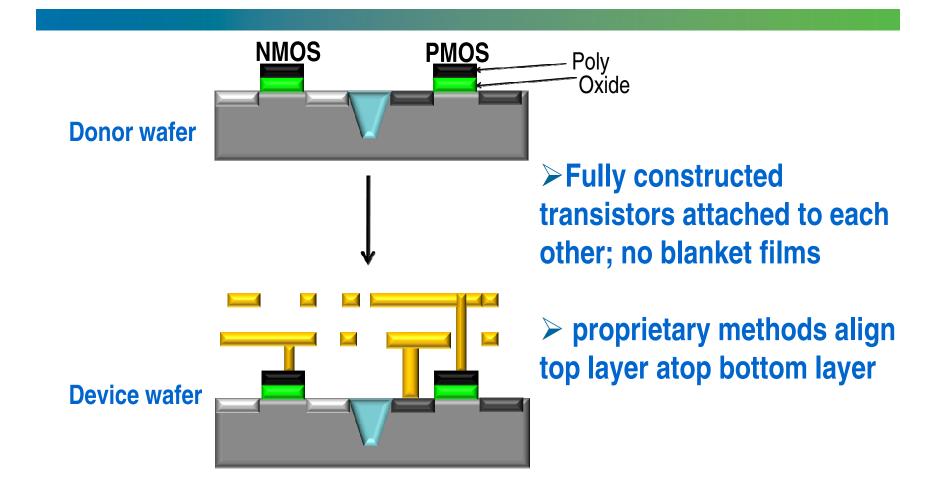

### **A Gate-Last Process for Cleave and Layer Transfer**

### **A Gate-Last Process for Cleave and Layer Transfer**

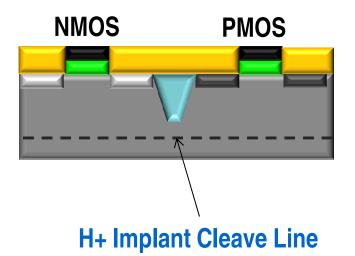

### Step 3. Implant H for cleaving

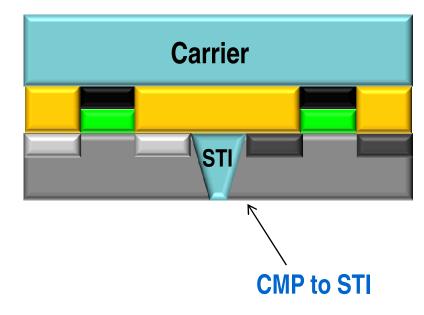

### Step 4.

- Bond to temporary carrier wafer (adhesive or oxide-to-oxide)

- > Cleave along cut line

- > CMP to STI

### **A Gate-Last Process for Cleave and Layer Transfer**

<u>Step 5.</u>

Low-temp oxide

### deposition

Bond to bottom layer

Remove carrier

### A Gate-Last Process for Cleave and Layer Transfer

#### Remove (etch) dummy gates, replace with HKMG

### **Step 6.** On transferred layer:

- Etch dummy gates

- Deposit gate dielectric and electrode

- > CMP

- Etch tier-to-tier vias thru STI

- Fabricate BEOL interconnect

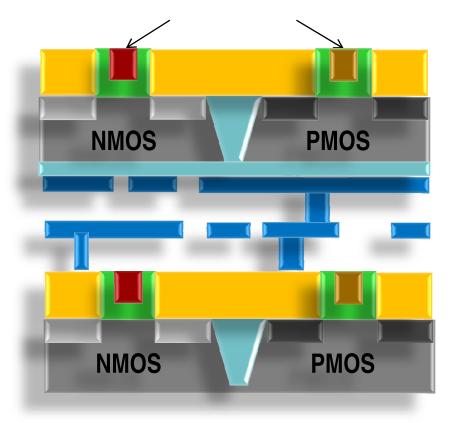

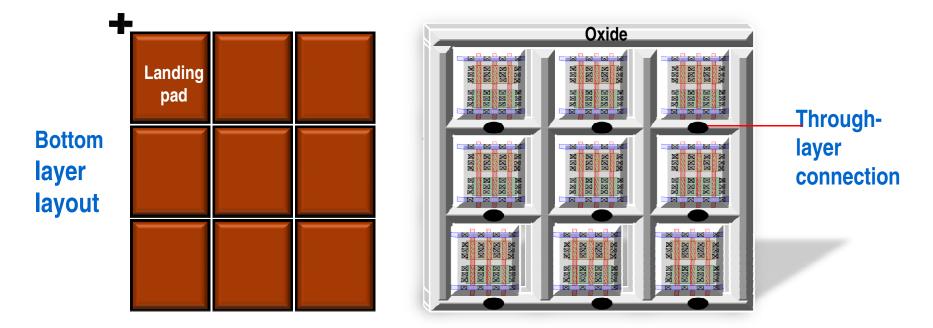

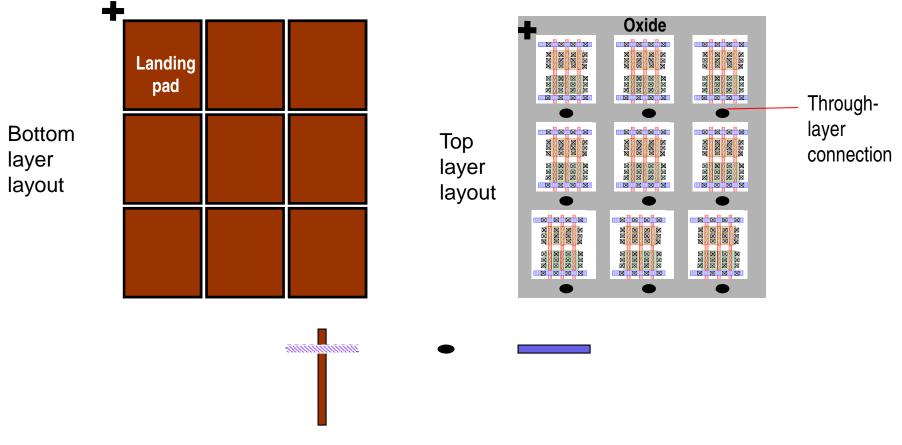

### Path 2 – Leveraging Gate Last + Innovative Alignment

Misalignment of pre-processed wafer to wafer bonding step is ~1um

How to achieve 100nm or better connection pitch

How to fabricate thin enough layer for inter-layer vias of ~50nm

### 1µ Misalignment

### **Novel Alignment Scheme using Repeating Layouts**

$\succ$  Even if misalignment occurs during bonding  $\rightarrow$

repeating layouts allow correct connections

> Above representation simplistic (high area penalty)

## **A More Sophisticated Alignment Scheme**

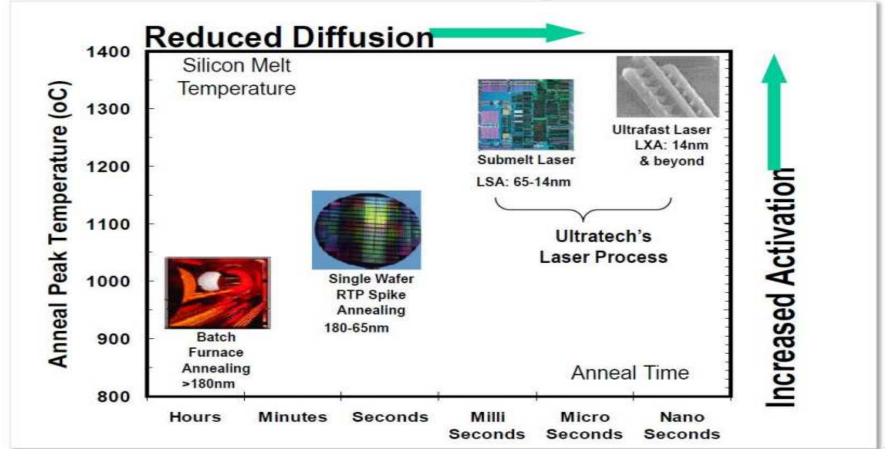

## **MonolithIC 3D - 3 Classes of Solutions**

- RCAT Process the high temperature on generic structures prior to 'smart-cut', and finish with cold processes – Etch & Depositions

- Gate Replacement (=Gate Last, HKMG) Process the high temperature on repeating structures prior to 'smart-cut', and finish with 'gate replacement', cold processes – Etch & Depositions

- Laser Annealing Use short laser pulse to locally heat and anneal the top layer while protecting the interconnection layers below from the top heat

## **Annealing Trend with Scaling**

Ultratech

### **Thermal Annealing Evolution**

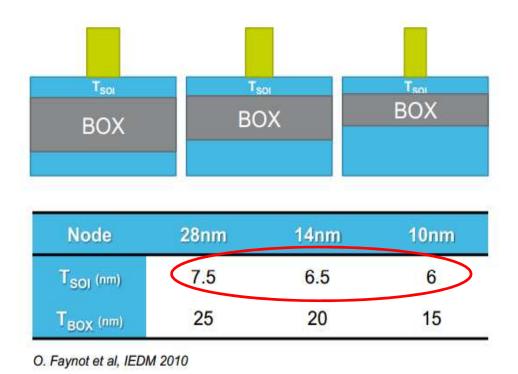

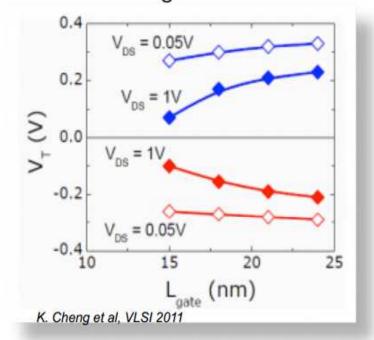

## Planar UTBB FD-SOI Scalability: T<sub>SOI</sub> & T<sub>BOX</sub> 32

Si data for L<sub>G</sub>=15nm:

- Electrostatic control improved by Thinning T<sub>BOX</sub>

- Scalability down to 10nm node

- Devices already processed with 3.5nm SOI film!

## LSA 100A – Short Pulse, Small Spot

Two Major Semiconductor Trends help make Monolithic 3D Practical NOW

> As we have pushed dimensional scaling:

- The volume of the transistor has scaled

- Bulk <u>um</u>-sized transistors —> FDSOI & FinFet <u>nm</u> transistors

- Processing times have trended lower

- > Shallower & sharper junctions, tighter pitches, etc.

=> Much less to heat and for much shorter time

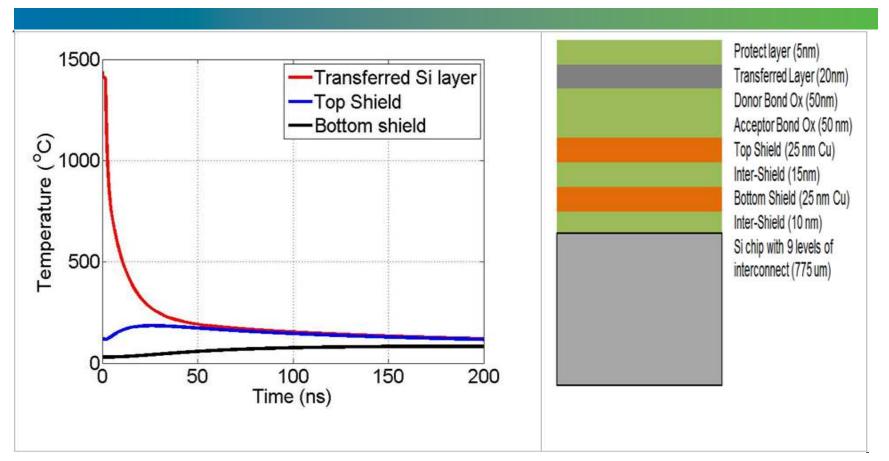

# The Top Layer has a High Temperature >1000°C) without Heating the Bottom Layers (<400℃) !!!

## **Process Window Set to Avoid Damage**

Temperature variation at the 20 nm thick Si source/drain region in the upper active layer during laser annealing. Note that the shield layers are very effective in preventing any large thermal excursions in the lower layers

# The Monolithic 3D Advantage

- II. Reduction die size and power doubling transistor count

- Extending Moore's law

### Monolithic 3D is far more than just an alternative to 0.7x scaling !!!

- III. Significant advantages from using the same fab, design tools

- IV. Heterogeneous Integration

- V. Multiple layers Processed Simultaneously Huge cost reduction (Nx)

- VI. Logic redundancy => 100x integration made possible

- VII. Enables Modular Design

- VIII. Naturally upper layers are SOI

- IX. Local Interconnect above and below transistor layer

- X. Re-Buffering global interconnect by upper strata

- XI. Others

- A. Image sensor with pixel electronics

- B. Micro-display

## Monolithic 3D Provides an Attractive Path to...

## Summary

- Monolithic 3D is now practical and well positioned to keep Moore's Law alive for many years

- Multiple paths to process mono-crystal transistors over copper interconnect

- Monolithic 3D IC provides many opportunities for existing products and for new products & architectures

# **Back Ups**

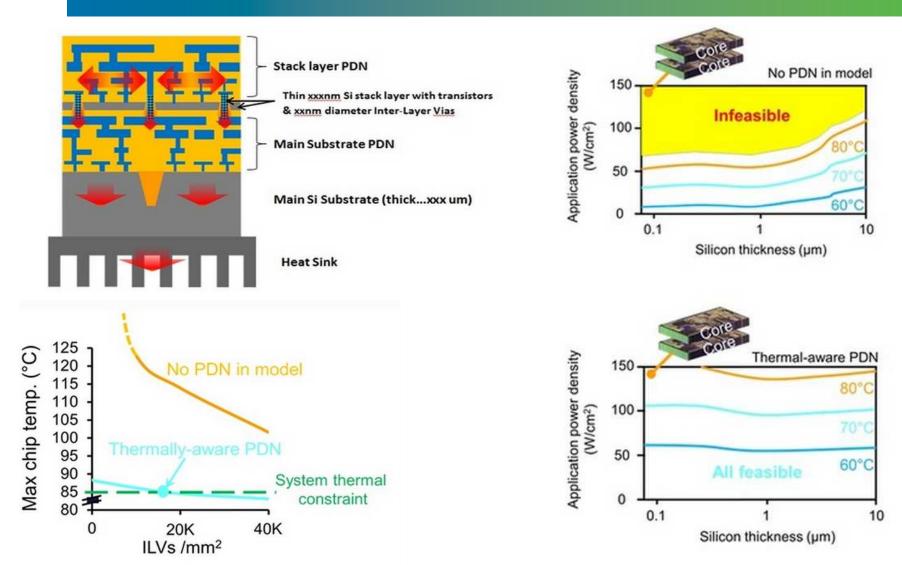

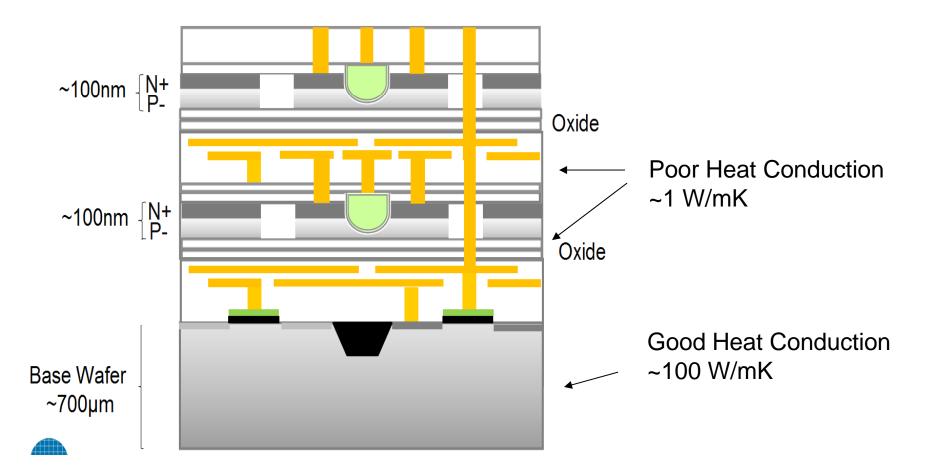

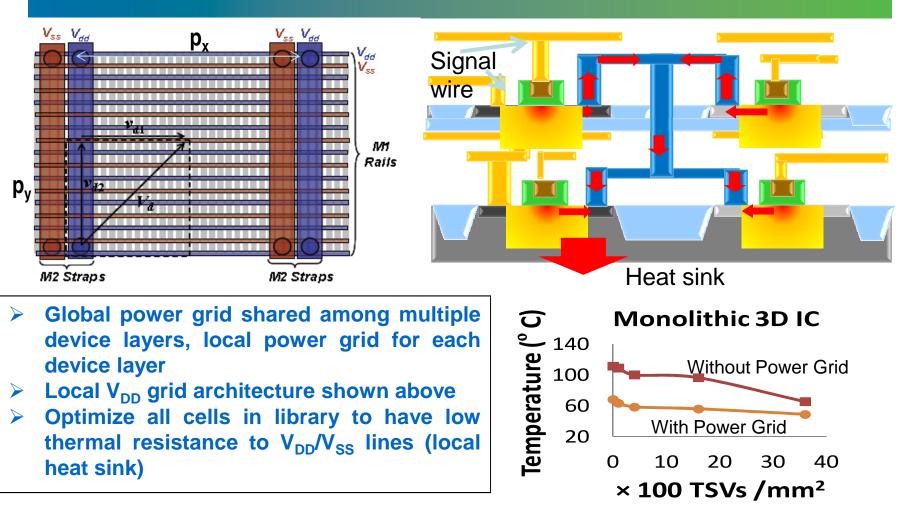

## The Operational Thermal Challenge

Upper tier transistors are fully surrounded by oxide and have no thermal path to remove operational heat away

## The Solution

- Use Power Delivery (Vdd, Vss) Network ("PDN") also for heat removal

- Add heat spreader to smooth out hot spots

- Add thermally conducting yet electrically nonconducting contacts to problem areas such as transmission gates

# IEDM 2012 Paper

### Cooling Three-Dimensional Integrated Circuits using Power Delivery Networks (PDNs)

Hai Wei, Tony Wu, Deepak Sekar<sup>+</sup>, Brian Cronquist<sup>\*</sup>, Roger Fabian Pease, Subhasish Mitra

Stanford University, Rambus+, Monolithic 3D Inc.\*

### **Monolithic 3D Heat Removal Architecture**

(Achievable with Monolithic 3D vertical interconnect density)

# Power Delivery (Vdd, Vss) Network Provide effective Heat Removal Path