## **3D Packaging for Memory Application**

(NCCAVS Joint User Group Meeting)

## Outline

- Motivations for 3D Packaging Technology Adoption in Memory Space

- Memory Cost Scaling Challenge

- Power Efficiency Requirement

- Memory Sub-system Performance Demand

- Traditional 3D Packaging Technologies for Memory Application

- System-in-Package (SiP)

- Package-on-Package (PoP)

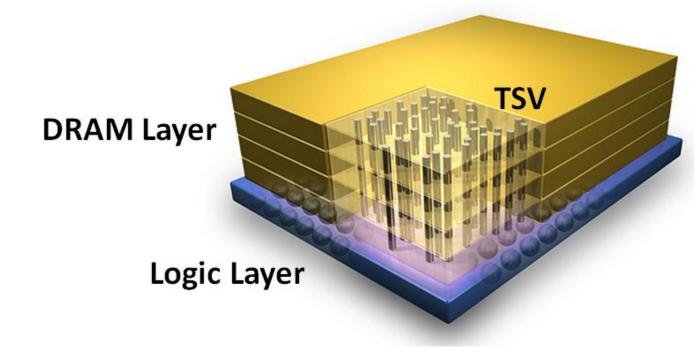

- Emerging TSV Based 3D Packaging Technologies for Memory Application

- Mobile Wide IO DRAM

- Hybrid Memory Cube (HMC)

- High Bandwidth Memory (HBM)

- Rambus 3D Package for Logic/Memory Application

- Summary

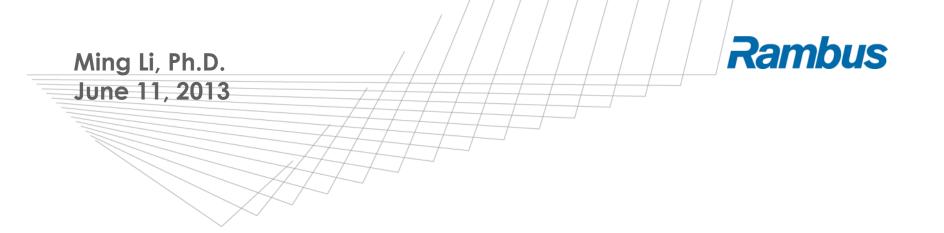

### Memory Cost Scaling Challenge

### Memory Cost Scaling Over Time

3 ©2013 Rambus Inc. (Source: Mike Black, Micron, EDPS 2013)

R

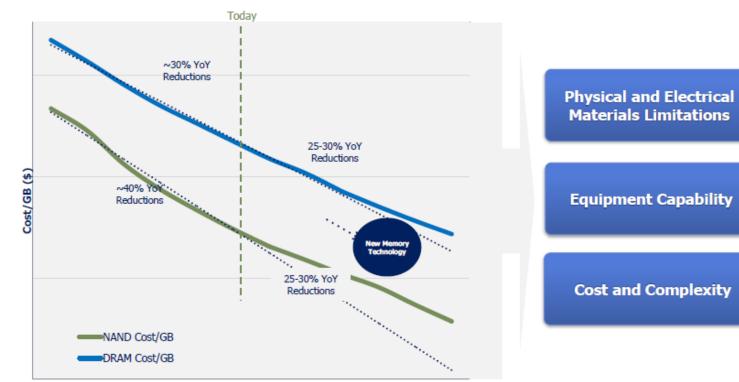

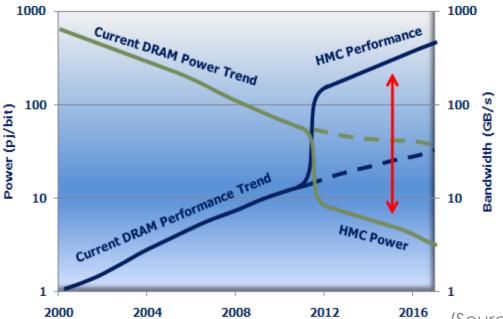

### Power Efficiency Requirement

Scaling of I/O date rate with constant I/O power dissipation

Even more challenging for computing memory subsystem memory bandwidth (BW) scaling

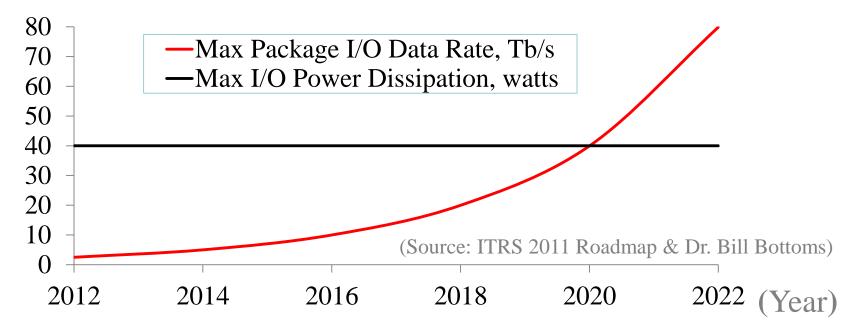

### **Memory BW Demand**

- Packaging and interconnect technology vital in defining memory sub-system performance

- Traditional off-package interconnection between CPU and memory chip not going to scale, trends: on-package interconnection and 2.5D/3D interconnection

R

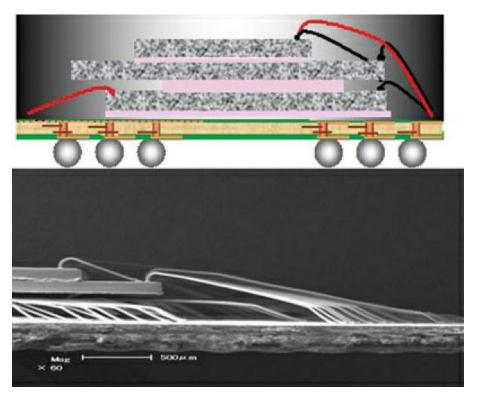

## Traditional 3D Packaging for Memory Application - SiP

(Source: Internet)

- System-in-Package (SiP)

- Die stacking using wire bond (WB) interconnects

- Same memory die stacking for memory capacity (NAND or DRAM)

- Logic/memory die stacking for memory bandwidth (BW)

- Low cost solution

- Limited BW scalability due to limited WB interconnect density

- Know-Good-Die (KGD) concern

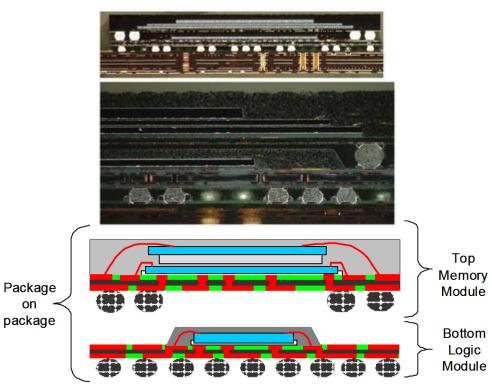

### Traditional 3D Packaging for Memory Application - PoP

(Source: Internet)

- Package-on-Package (PoP)

- Top memory package

- Bottom logic package

- Logic and memory packages separated for logistic control and KGD

- Standard memory interface between top and bottom

- Limited BW scalability due to limited interface memory bus width

- Mainly for mobile application

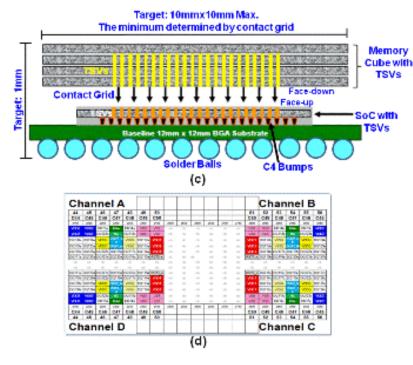

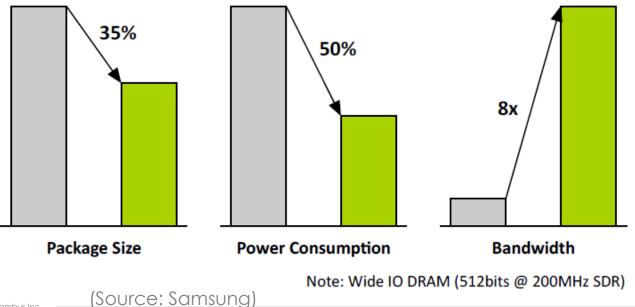

### TSV Based 3D Packaging Technology for Memory Application – Wide IO DRAM

|                           | WideIO    | LPDDR3               |  |

|---------------------------|-----------|----------------------|--|

| Power                     | 1.2 volts | 1.2 volts            |  |

| Speed                     | 200 Mbps  | 1600 Mbps            |  |

| Data width                | 512 bits  | 32 or 64 bits        |  |

| Data rate                 | single    | double               |  |

| Maximum channel bandwidth | 12.8 Gbps | @32 bits 6.4<br>Gbps |  |

- Low power for mobile application

- Small formfactor

- Thin profile

- High cost

- Complicate business model

- Yield loss

- Scrap management

### Wide IO DRAM Stacking vs. PoP

Conventional PoP Solution (package-on-package) Direct Chip Connection using TSV (TSV-micro bump joint)

### TSV Based 3D Packaging Technology for Memory Application – Hybrid Memory Cube (HMC)

R

### Hybrid Memory Cube (HMC)

Fast process logic and advanced DRAM design in one optimized package

- Power Efficient

- Smaller Footprint

- Increased Bandwidth

- Reduced Latency

(Source: MemCon Memory Conference 2012)

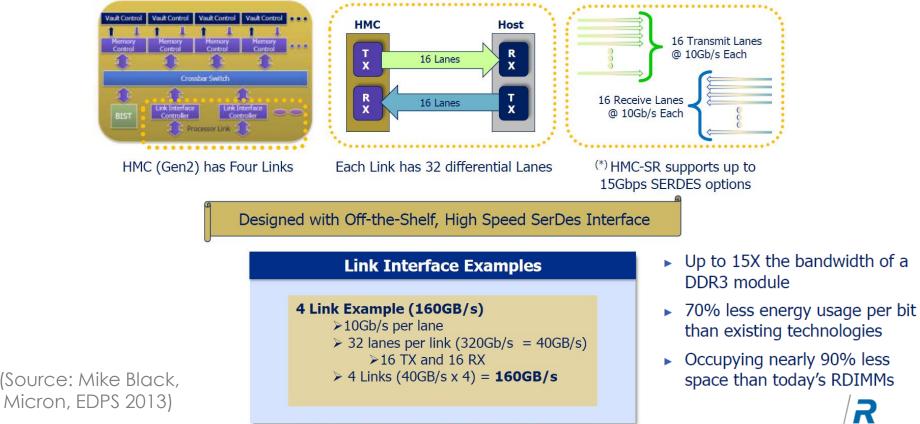

## **HMC Link Controller Interface**

(\*) Aggregate DRAM peak bandwidth remains 160GB/s

### **HMC Application**

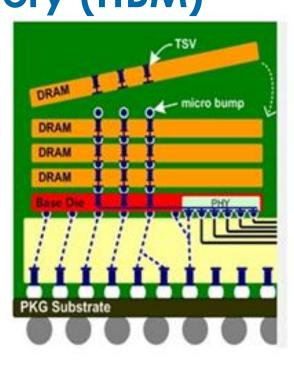

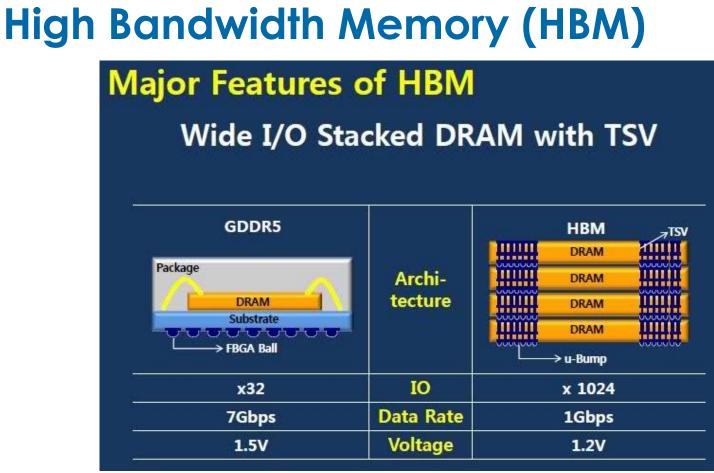

# TSV Based 3D Packaging Technology forMemory Application - High BandwidthMemory (HBM)TTEMTARGET

| ITEM                    | TARGET                                |  |

|-------------------------|---------------------------------------|--|

| Burst Length            | 2, 4                                  |  |

| Stack Density           | 1GByte per stack<br>(2Gbit per slice) |  |

| Channel / Slice         | 2                                     |  |

| Banks / Channel         | 8                                     |  |

| IO / Channel            | 128                                   |  |

| Prefetch / Channel      | 32B (128x2bit)                        |  |

| Channels / Stack        | 8                                     |  |

| Total TSV Data IO Width | 1024                                  |  |

| Clock Speed             | 500MHz                                |  |

| Peak Read BW / Stack    | 128 GB/s                              |  |

| Page Size               | 2KB                                   |  |

| Data Parity             | 1 bit / 32 bit                        |  |

| DRAM Core Voltage       | 1.2V                                  |  |

| Logic Buffer IO Voltage | 1.2V                                  |  |

R

15 ©2013 Rambus Inc.

(Source: SK/Hynix, Jan 2013)

### Markets for TSV Based 3D Packaging Technologies

| Market            | SmartPhone             | Tablet                                                   | Networking                                             | Graphics                         |

|-------------------|------------------------|----------------------------------------------------------|--------------------------------------------------------|----------------------------------|

| Processor         | Apps Processor         | Apps Processor                                           | Networking Proc                                        | Graphic Proc                     |

| Power             | 1-2W                   | 1-5W                                                     | 20W +                                                  | 20W +                            |

| Memory<br>Type    | Wide I/Ox              | Wide I/Ox or<br>LPDDRx                                   | HMC / HBM                                              | НВМ                              |

| Memory Size       | $2 \to 4 \; \text{GB}$ | $4 \to 8 \to 16 \text{ GB}$                              | $4 \rightarrow 8 \rightarrow 16 \text{ GB}$            | $4 \rightarrow 16 \text{ GB}$    |

| Interface         | Wide I/O2              | Wide I/O or DDR                                          | SerDes / Parallel                                      | Parallel                         |

| I/O               | 1000                   | 1000 or 500                                              | <500/>1000                                             | 1600 +                           |

| Min Bump<br>Pitch | 40x40µm rows           | 40x50µm rows or<br>80µm rows                             | 1mm / 96x55µm<br>array                                 | 96x55µm array,<br>staggered rows |

| Packaging         | 3D                     | 2.5D medium L/S<br>density or 3D with<br>heat management | Off chip memory or<br>2.5D high density<br>interposers | 2.5D high density interposers    |

|                   |                        |                                                          | 🧇 🗐                                                    |                                  |

(Source: Internet)

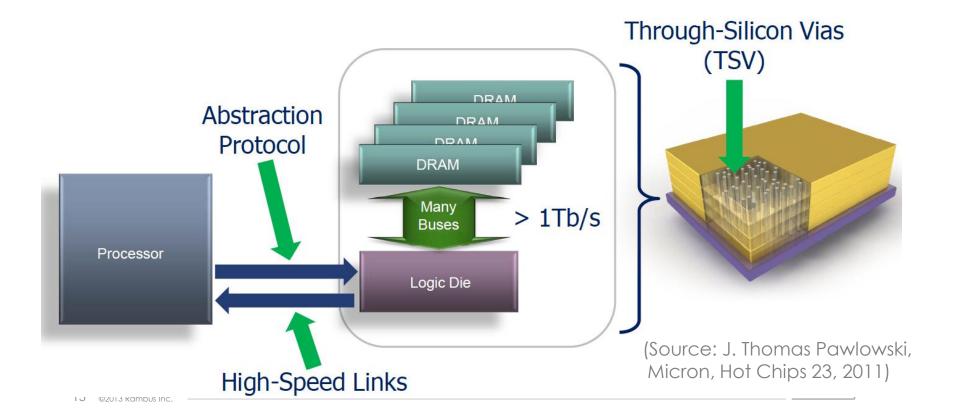

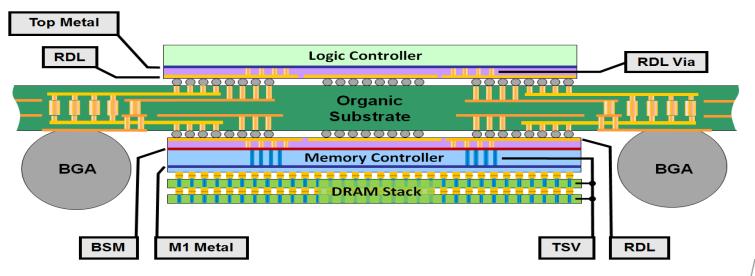

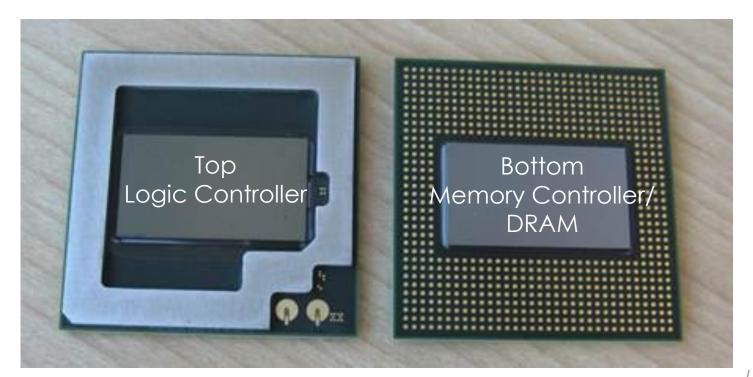

### Rambus 3D Package for Logic/Memory - Introduction

- CPU/GPU performance often constrained by both insufficient memory bandwidth and excessive memory power

- Stacked CPU/GPU and DRAM (using TSV) poses significant challenges to thermal management and power delivery

- One solution is double-sided flip-chip package with a processor on top and stacked DRAMs on bottom

- Middle-ground approach between traditional package-to-package, on-PCB solutions and pure-3D integration

- Processor interfaces with memory directly through package

- Very high IO density and low-loss interconnect paths

- $\cdot$  Thermally decoupled processor and memory devices

(Package co-design & optimization: Secker D.; et al., ECTC 2012)

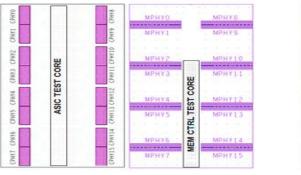

### **3D Package Physical Architecture**

- Organic Substrate and Assortment of BEOL Technologies

- Controller and DRAM stack share a 5-2-5 organic substrate

- RDL on Controller and DRAM

- Disaggregated DRAM with fine-pitch TSV's

- 256 GB/s peak DQ bandwidth across 800 diff. pairs (4 Gb/s per pair)

R

18 @2013 Rambus Inc. (Package co-design & optimization: Secker D.; et al., ECTC 2012)

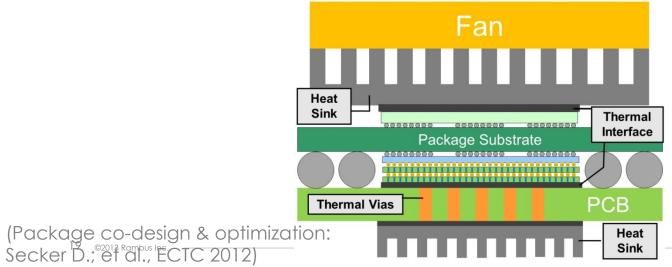

## **Thermal Design**

- High power of stacked memory with high-performance processor creates thermal management issue in 3D IC

- Thermal isolation achieved mounting components on opposite sides of package substrate

- Memory stack cooled using combination of thermal interface material, PCB thermal vias and back-side heat sink

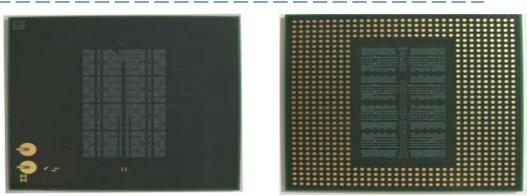

## **3D Package Implementation**

**Controller and DRAM Floorplans**

### **Controller Die**

- 12.3 x 21.6mm ٠

- 200um C4 pitch

**Bottom View**

### **Organic Package** Substrate

- 35x35mm outline ٠

- Thin-core 5-2-5 buildup

- 718 BGA (1mm pitch) ٠

- ~ 8800 C4 (total) .

### **Top View**

(A 256GB/s Memory Subsystem Built Using a Double-Sided IC Package with a /20 <sup>©2013 Rambus I</sup>Memory Controller and 3D-Stacked DRAM: Best S.; et al., DesignCon 2013)

### Rambus 3D Package for Logic/Memory

### Summary

- Cost scaling, power efficiency and bandwidth are three main factors that drive the adoption 3D packaging technology for memory application.

- Traditional 3D packaging technologies like SiP and PoP have reached the scaling limit for performance and power efficiency.

- Emerging TSV based 3D packaging technology shows great potential for scaling but many issues have to be resolved before it could be a mature technology.

- Rambus 3D packaging technology for logic/memory application bridges both mature technologies and advanced 3D IC technology and shows great potential for immediate implementation.

## Thank you

### rambus.com