## **Process Development for Advanced Generation Crystalline Silicon Solar Cells**

James Gee

Applied Materials, Santa Clara, CA

Northern California Chapter of the American Vacuum Society Joint User Group Topical Conference February 21, 2011

## Outline

- Roadmaps

- Industry

- Trends in High Efficiency

- Applied Materials

- Process Development Examples:

- Ion Implantation

- Heterojunction

- Screen Printing

- Passivation

- Personal Observations

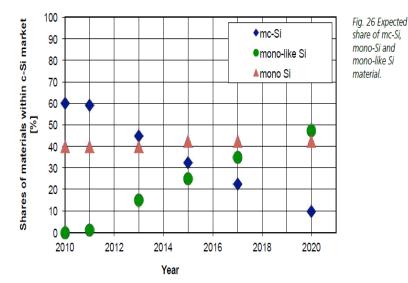

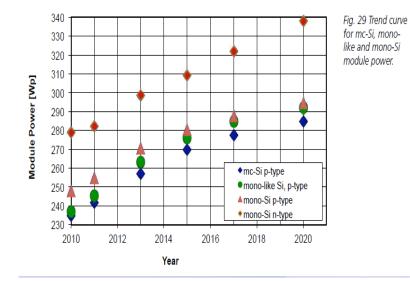

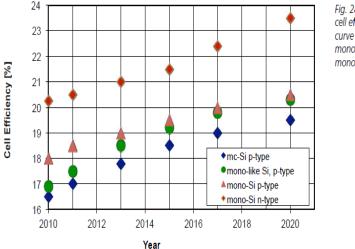

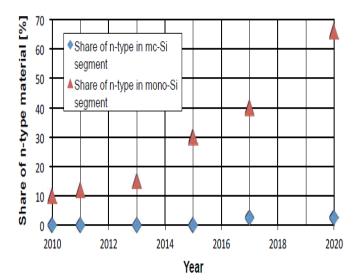

## ITRPV March 2012 (2011 Roadmap)

Fig. 28 Stabilized cell efficiency trend curve for mc-Si, mono-like and mono-Si.

Fig. 27 Expected share of n-type material on world production of c-Si solar cells.

## **Industry Roadmap**

- Industry Roadmap:

- ITRPV provides a useful illustration of future trends

- Does not have strong influence on individual company decisions

- Each company has their own roadmap

- Reasons:

- Past: Companies largely competed during rapid expansion of PV solar market by scale, value-chain cost optimization, and process optimization with largely similar process and products.

- Semi industry serves a range of end markets, so cooperation for improvement of base technology does not impact individual company competitive positions. Products in end solar market is largely interchangeable, so strong tendency towards commoditization.

- Applied Roadmap

- Based on analysis of emerging technology trends

- Performance/cost analysis attempts to fully value efficiency, energy yield, etc. in end system

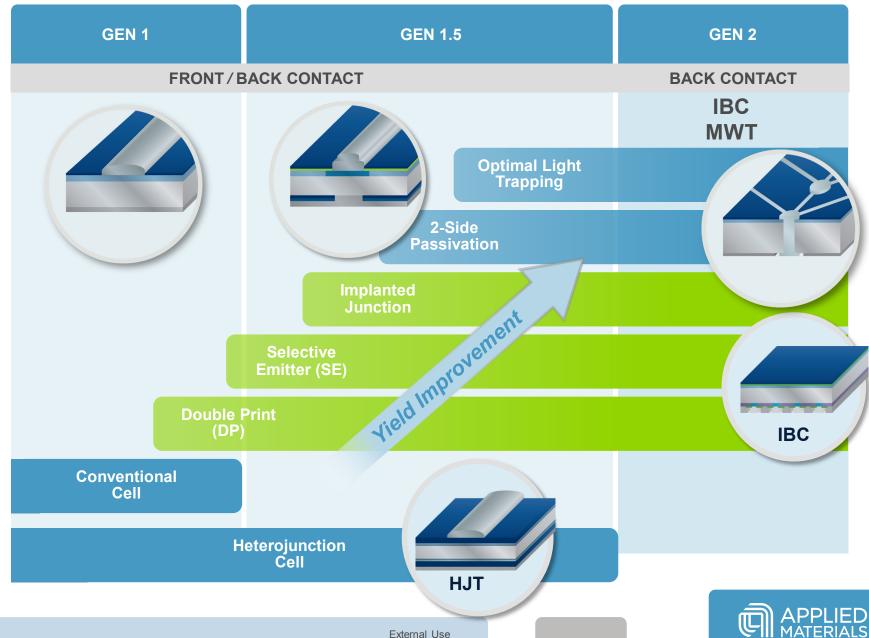

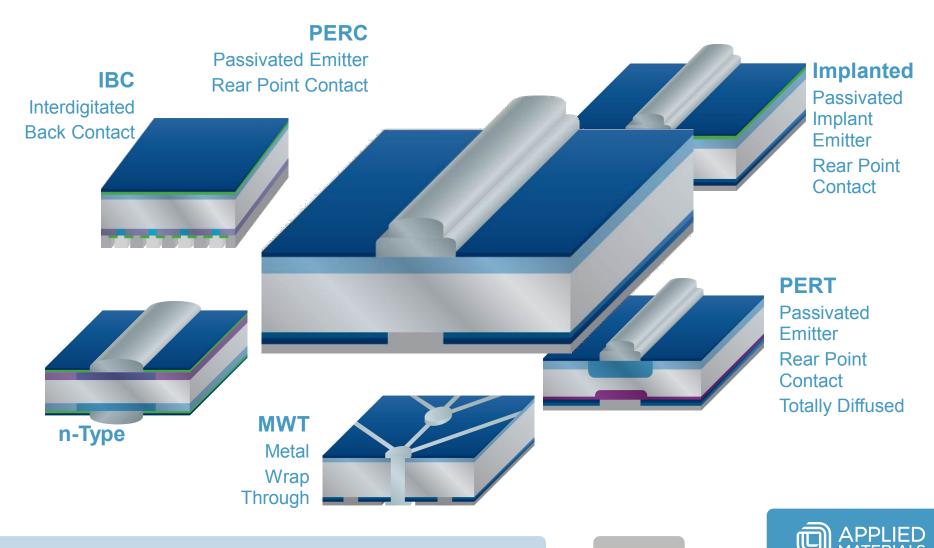

## **High Efficiency Structures in the News**

## **Applied Materials Powering the c-Si PV Roadmap**

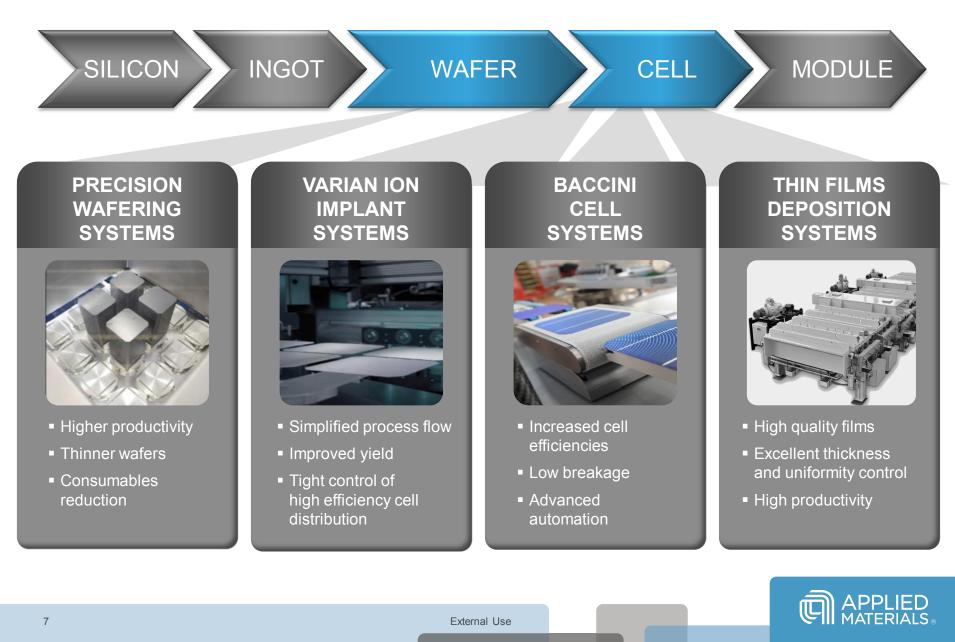

# **PV Manufacturing Solutions Leadership**

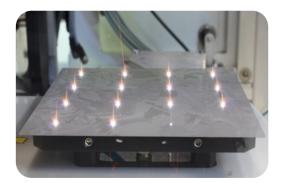

## **Solion<sup>™</sup>: Exceptional Process Control**

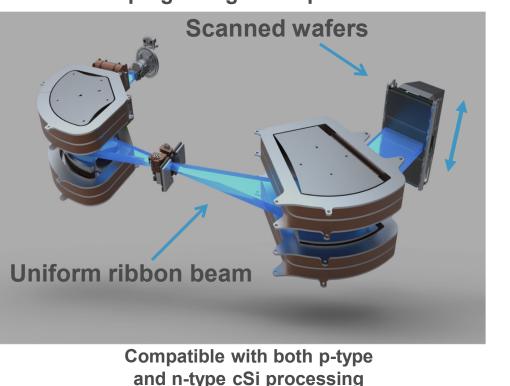

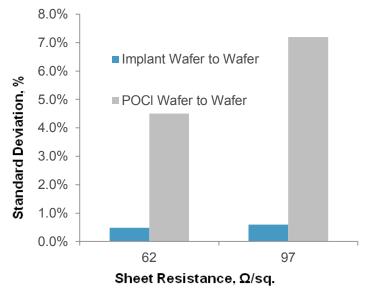

#### **Doping Using Ion Implantation**

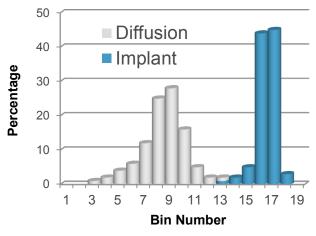

Excellent wafer uniformity – for high Rs emitters yields improved binning

### Ribbon beam improves uniformity and binning performance

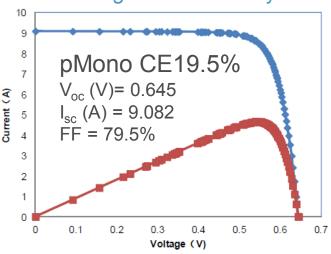

## High Quality Emitter = High Efficiency Solion Device Performance and Yield

#### **High Cell Efficiency**

#### **Device Performance**

- Superior Emitter Junction Quality No dead layer - Better blue response

- Precise Uniform Doping- FF, J<sub>sc</sub>

- No cost thermal oxide Improved passivation- V<sub>oc</sub>

#### Yield

#### **Process Simplification**

- Eliminate PSG Clean

- Single sided doping no edge isolation

- In situ patterning SE

#### **Precise Uniformity and Repeatability**

Enables 2-3x fewer bins

#### **Superior Binning**

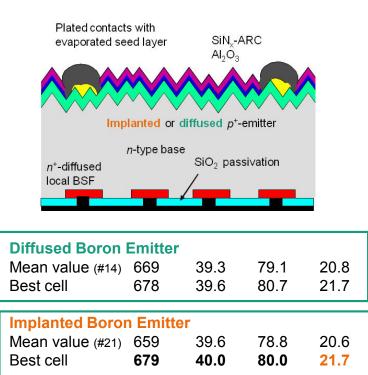

# Why n-type Cells?

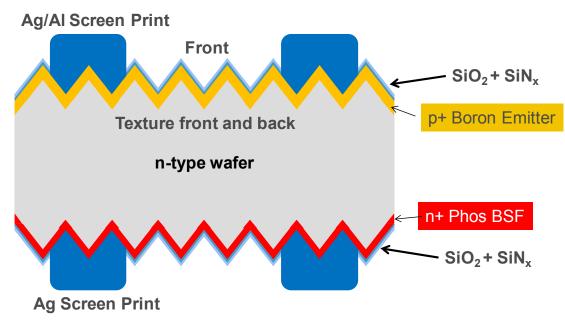

#### **Boron Front Emitter**

- Efficiency entitlement exceeding 21% due to high bulk lifetime

- No Light Induced Degradation (LID)

- Passivation Options: SiO<sub>2</sub> / SiN<sub>x</sub> or Al<sub>2</sub>O<sub>3</sub> / SiN<sub>x</sub>

- Metallization: Screen printed Grid, front and back

- Texturing: Single or Double side textured possible

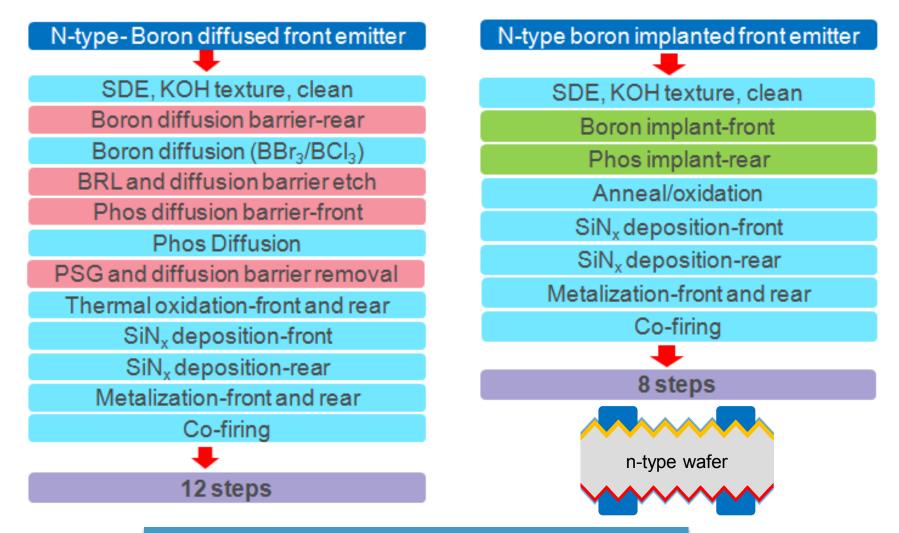

# Why Implant for n-type Cells?

N-type cell process with implant significantly reduces process steps and complexity

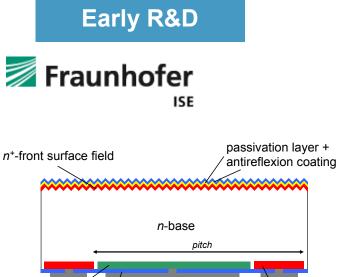

# $\textbf{n-type} \ \textbf{R\&D} \rightarrow \textbf{Customer}$

#### Early R&D

Cell area 2x2 cm² on 1  $\Omega cm$  FZ Silicon

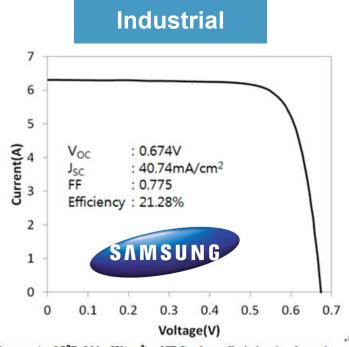

#### Industrial

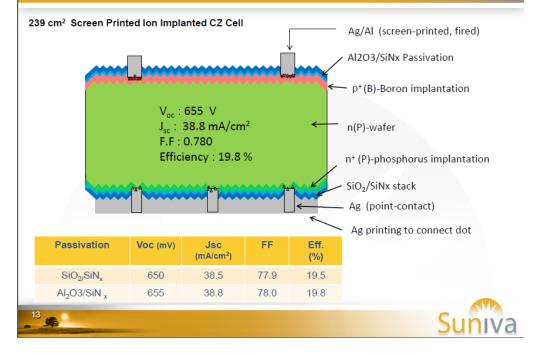

## 19.8% implanted B front junction cell with PBSF and local back contacts

- 19.8% CE with p+/n+ ion implantation

- Path to >21% CE

Rohatgi, nPV Workshop 2012

Hermle et al., 26th EUPVSC, p. 875, 2011

## IBC R&D → Customer

$p^{++}$ -emitter metallization  $n^{++}$ -back surface field Al<sub>2</sub>O<sub>3</sub>passivation layer

| Rear Side<br>Passivation       | $ ho \\ (\Omega cm)$ | V <sub>oc</sub><br>(mV) | J <sub>sc</sub><br>(mA/cm²) | FF<br>(%) | η<br>(%) |

|--------------------------------|----------------------|-------------------------|-----------------------------|-----------|----------|

| SiO <sub>2</sub>               | 1                    | 642.2                   | 37.8                        | 78.8      | 19.2     |

| Al <sub>2</sub> O <sub>3</sub> | 5                    | 650.1                   | 40.5                        | 75.8      | 20.0     |

>20% fully implanted POC

Bateman et al., 1st Silicon PV, p. 509, 2011

Fig. 3. I-V curve (at 25°C, 100mW/cm<sup>2</sup>) of IBC solar cell via ion implantation.

- 21.28% large-area IBC Solar Cell

- High J<sub>sc</sub> (~41 mA/cm<sup>2</sup>)

- All doping through ion implantation with shadow masks

Mo et al., 27th EUPVSEC 2012,

"High Efficiency Back Contact Solar Cell via Ion Implantation", 2CV.7.25

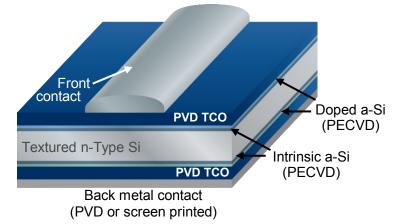

# Heterojunction

- Heterojunction cells offer high cell efficiency and low temperature process

- c-Si HJT cell performances

Panasonic HIT technology announcement: R&D: 24.7% Production: >20%

#### **Heterojunction Cell Structure**

- Superior temperature coefficient and absence of PID & LID

- PECVD a-Si films best-in-class uniformity and lifetime; high productivity platforms

- High productivity PVD platform for TCO

#### Heterojunction cell structures receiving greater interest

TCO: Transparent Conductive Oxide; PID: Potential induced degradation, LID: Light induced degradation

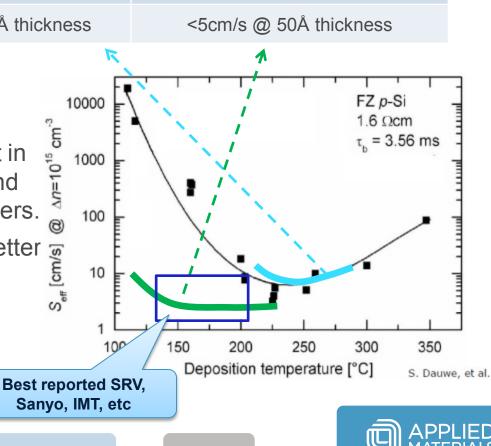

## **Improvement to Heterojunction Process**

|                          | Original RF Process      | New VHF Process             |

|--------------------------|--------------------------|-----------------------------|

| RF Frequency             | 13.56 MHz                | 40 MHz                      |

| Substrate<br>Temperature | 225-300°C                | 120-250°C                   |

| Deposition Rate          | >5Å/s for p, i, n layers | <2.5 Å/s for p, i, n layers |

| SRV                      | >10cm/s @ 50Å thickness  | <5cm/s @ 50Å thickness      |

|                          | R                        | 1                           |

- New VHF-PECVD hardware and process have enabled improvement in the a-Si passivation performance and the development of novel doped layers.

- Reduced deposition rate enabled better thickness control and process repeatability.

## **Applied Solutions for Heterojunction Cells**

#### Production Proven PECVD Options for R&D and HVM

Reliable and Proven Printing and Drying Solutions for Unique Heterojunction Requirements

#### High Throughput PVD System to Address Multiple Applications

#### **Baccini Metallization**

**Production Proven Solutions for Emerging Technologies**

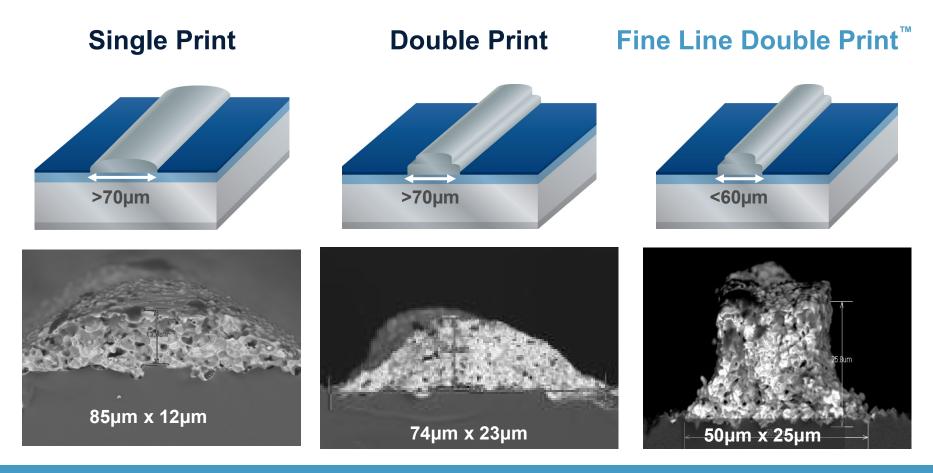

# Screen Printing Double Print MWT

## **Double Print Structures**

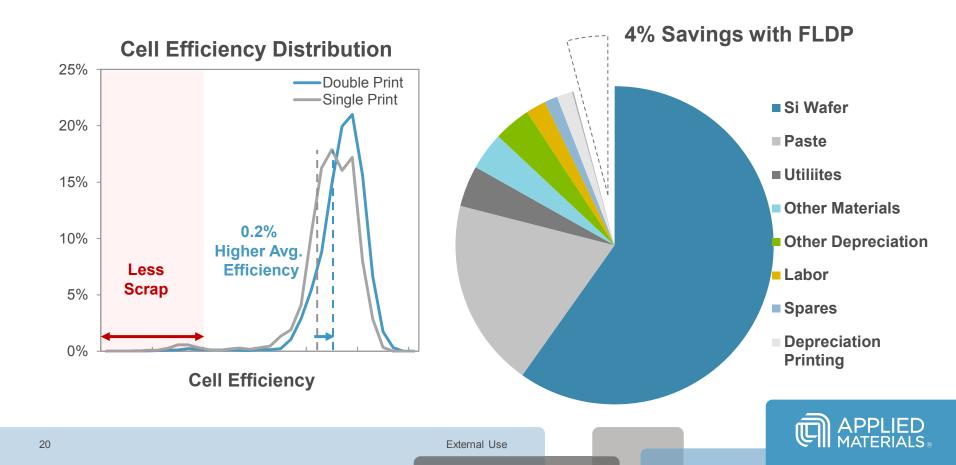

Fine Line Double Print enables 0.2% CE gain over single print and 20% Ag paste reduction

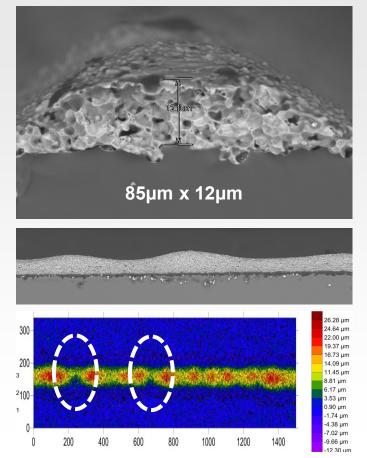

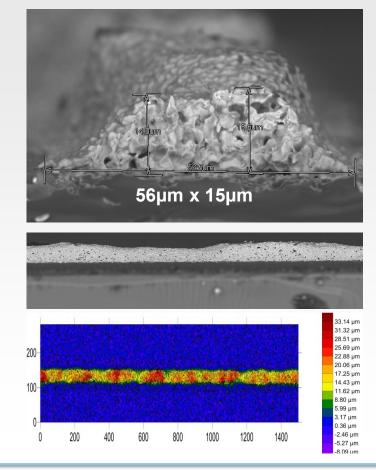

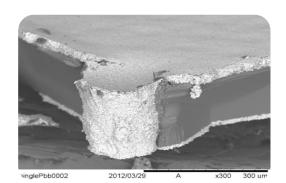

## **FLDP<sup>™</sup> Morphology Comparison**

#### **Single Print**

#### Fine Line Double Print<sup>™</sup>

#### Better morphology and fewer interrupts with Fine Line Double Print

# **Driving Force for FLDP**<sup>™</sup>

Increasing Revenues, Reducing Costs with Double Print

More Watts produced

- 0.2% absolute higher efficiency

- Scrap rate reduced

Reduced cell processing costs

- Reduce paste usage by 20%

- All costs reduced with higher efficiency

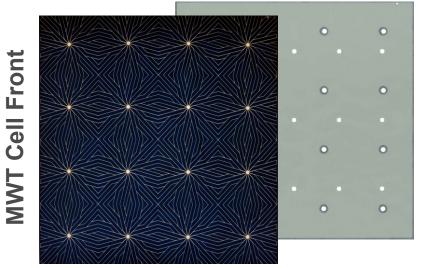

# Metal Wrap Through (MWT) Benefits

- No busbar on the front side

- Less paste deposit (up to 30% saving)

- Electrical contact only on the back side

- Higher short-circuit current density

- Higher V<sub>oc</sub> (recombination current is reduced by lower metallized area)

- Busbar shading 2%

- Finger shading 5%

# Efficiency gain of 0.3-0.5% absolute is observed ≥ 1% Efficiency gain at module level

Source: S.W. Glunz, Advances in OptoElectronics Volume 2007, Article ID 97370

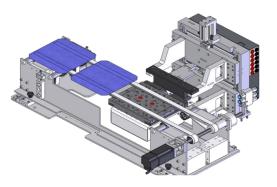

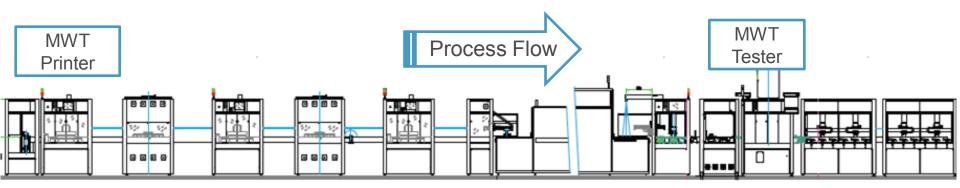

# **Applied Baccini MWT Distinctive Solutions**

#### **Laser Holes Drilling**

#### p and n-contacts Metallization

#### **I-V Testing**

Unique Galvo head plus Rotary table

Proprietary Closed Loop Control guarantees high accuracy and drift compensation

#### **Proven metallization**

- Full control of the vias filling

- Prevention of the cell contaminations

- No need for paper on nest

# Proven back contact probing

Best IV measurement repeatability

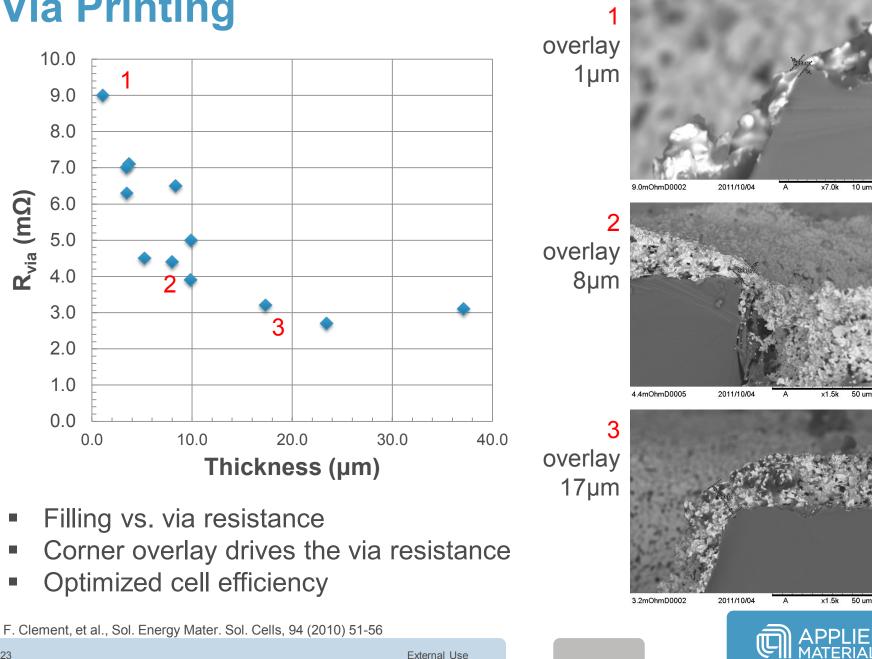

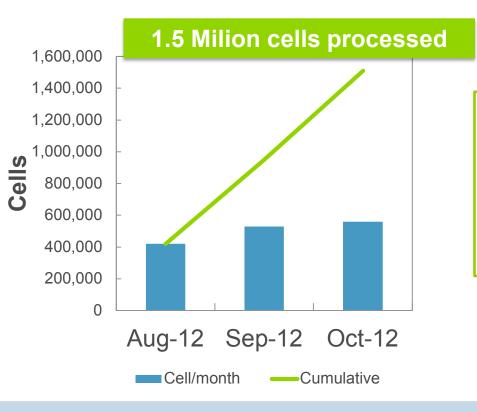

# Via Printing

## **Today: HVM**

- Same Breakage rate of standard cell

- Via Filling ratio > 98%

- Average Efficiency repeteability ± 0.05% absolute (dynamic mode)

# **Advanced Passivation**

## Advanced Cell Structures For High Efficiency Need 2-Side Passivation Solutions

## **Two-Side Passivation**

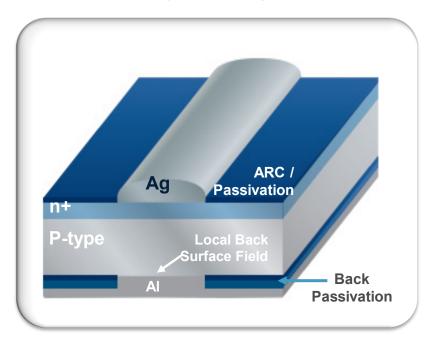

## **PERC Structure**

- Reduces backside recombination losses

- Contribute to ~ 45 % of efficiency gain

- Low surface recombination velocity

- Negative fixed charge Al<sub>2</sub>O<sub>3</sub> film repels electrons

- Improves backside reflection

- Contributes to ~ 55% of efficiency gain

- High back surface reflection of AIO/SiN (~90%) vs AI (65%)

### 2 Side Passivated Cell (PERC)

### Cell Efficiency Gains from Backside Passivation (Longer wavelength light capture)

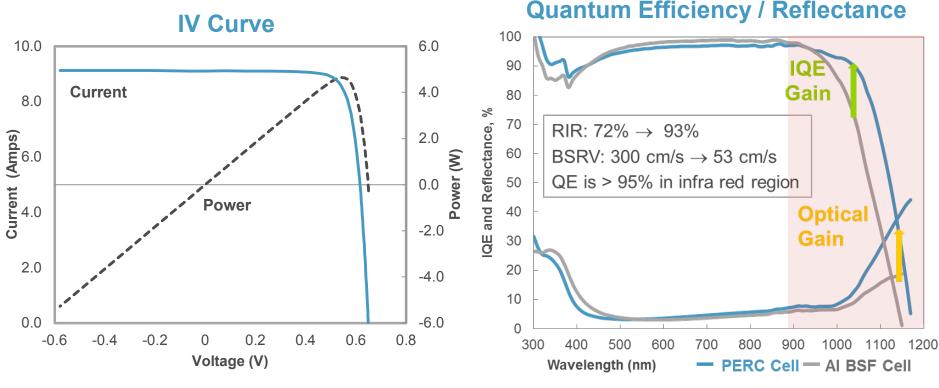

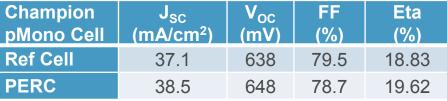

## P Type Mono-Si PERC Device Performance

- Red response benefit from lowered recombination and higher reflection

- Significant enhancements in IR response with backside passivation

- Long wavelength gains transfers to module

Demonstrates >0.6 efficiency gain with backside passivation on p-type mono cSi

Wijekoon et.al. 27th EU PVSEC (2012)

## **Concluding Personal Observations**

- End market continues to grow

- PV cell/module producers are becoming more sophisticated in valuing technology improvements

- A relentless drive to improve baseline technology (another 5W or go home!)

- Improved baseline technology and reduced costs raises the bar for disruptive technologies, but...

- Technology and brand differentiation will become larger component of many company business plans

- Cost structure of baseline technology will be migrated to the highefficiency potential of n-type material