## Mechanical Stresses and Reliability Study of Cu Through-Silicon Via (TSV) Samples Fabricated by SK Hynix vs. SEMATECH using Synchrotron X-Ray Microdiffraction for 3-D Integration and Reliability

A.S. Budiman<sup>1\*</sup>, H.-A. Shin<sup>2</sup>, B.-J. Kim<sup>2</sup>, S.-H. Hwang<sup>2</sup>, H.-Y. Son<sup>3</sup>, M.-S. Suh<sup>3</sup>, Q.-H. Chung<sup>3</sup>, K.-Y. Byun<sup>3</sup>, Y.-C. Joo<sup>2</sup>, R. Caramto<sup>4</sup>, L. Smith<sup>4</sup>, M. Kunz<sup>5</sup>, N. Tamura<sup>5</sup>

<sup>1</sup>Center for Integrated Nanotechnologies (CINT), Los Alamos National Laboratory (LANL), Los Alamos, NM 87545

<sup>2</sup>Dept. Of Materials Science & Engineering, Seoul National University (SNU), Republic of Korea

<sup>3</sup>PKG Development Group, R&D Division, SK Hynix Inc., Republic of Korea

<sup>4</sup>SEMATECH, Albany, NY

<sup>5</sup>Advanced Light Source (ALS), Lawrence Berkeley National Laboratory (LBNL), Berkeley, CA 94720

\*suriadi@alumni.stanford.edu

NCCAVS "3D Packaging", Tue, June 12<sup>nd</sup>, 2012

# Outline

- Background Mechanical Stresses and Reliability/Performance Implications in 3-D Cu TSV Integration Schemes

- The Technique Synchrotron X-Ray Submicron Diffraction (White and Monochromatic Beam)

- Experimental

- Mechanical Stresses in Cu TSV and Their Potential Impacts on 3-D Interconnect Reliability: SK Hynix vs. SEMATECH

- Mechanical Stresses in Silicon Surrounding TSV and Their Potential Impacts on 3-D Interconnect Performance as well as Reliability: SK Hynix vs. SEMATECH

- Conclusions & Future Work

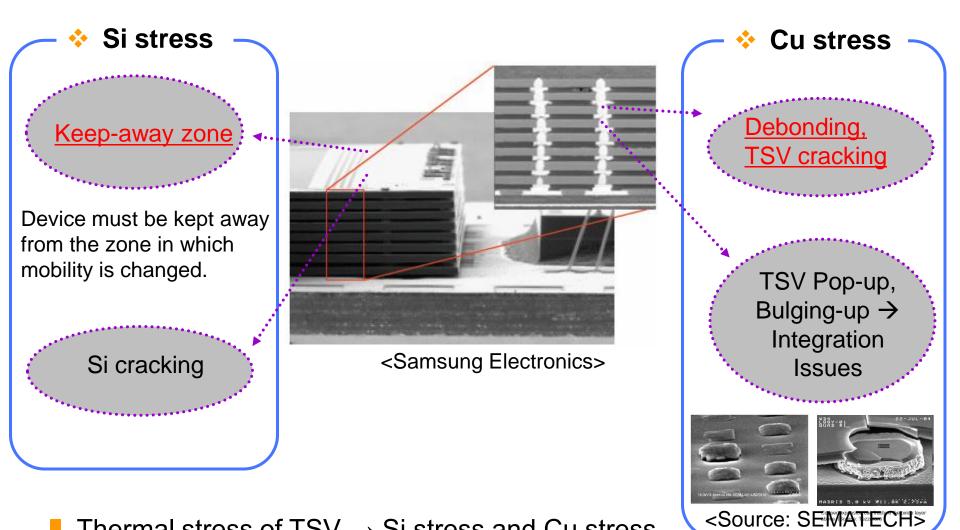

#### **Impact to Reliability and Performance of Device**

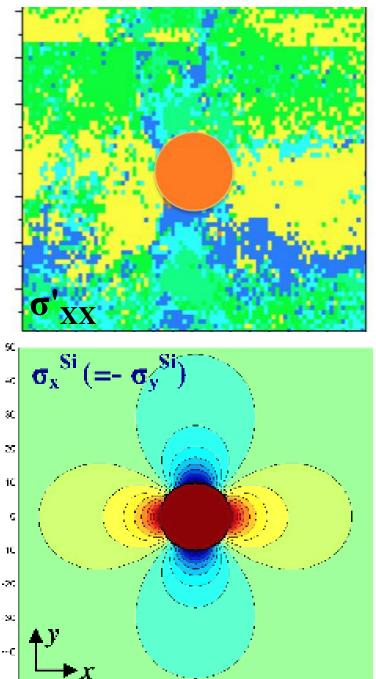

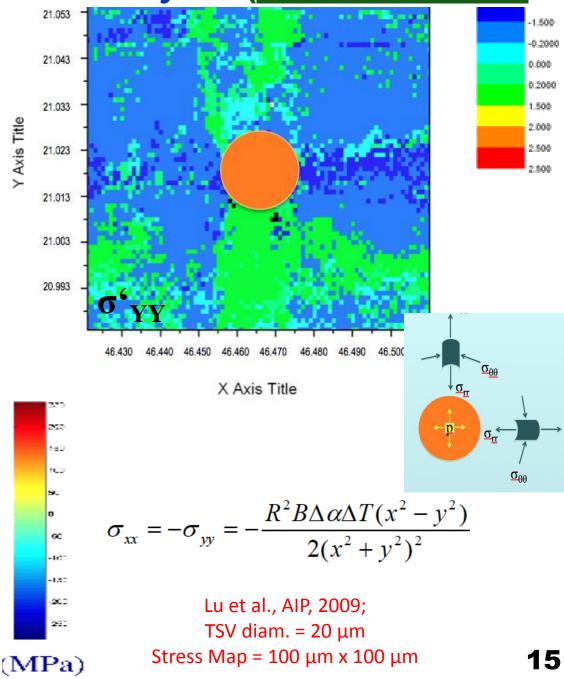

- Thermal stress of TSV  $\rightarrow$  Si stress and Cu stress.

- Si stress (residual stress)  $\rightarrow$  degradation of device performance.

- Cu stress (thermal stress)  $\rightarrow$  mechanical failure of Cu TSV.

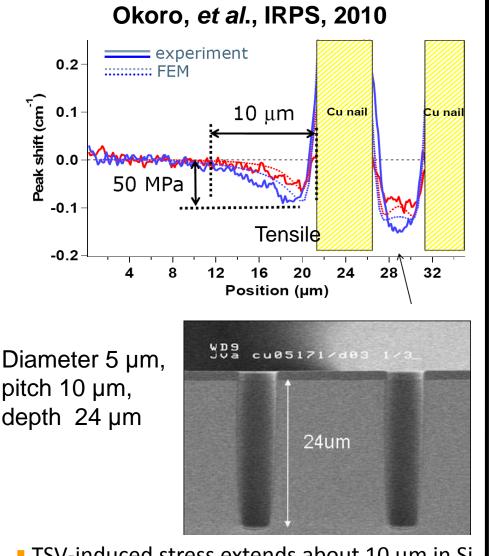

### Stress of Si : µ-Raman spectroscopy

TSV-induced stress extends about 10 μm in Si

50 MPa tensile stress in Si after cycling

Lee, *et al.*, TSV 3D Packaging Technology Workshop, 2010

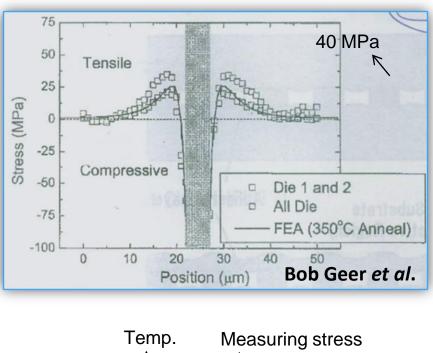

40 MPa tensile stress in Si was developed near Cu TSV after cycling.

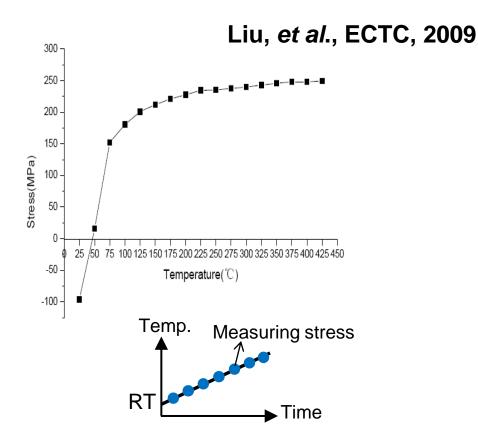

## Stress of Cu : Laboratory XRD Lack of micron resolution

Diameter 70  $\mu$ m , pitch 140  $\mu$ m, depth 460  $\mu$ m

+ 225 MPa at 200 °C.

- 100 MPa at 25 °C.

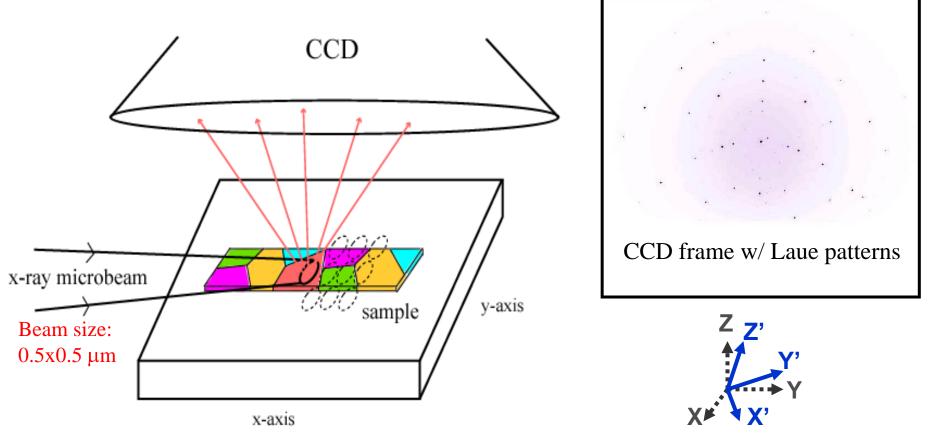

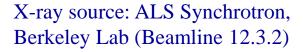

# Synchrotron X-Ray Sub-micron Diffraction

Deviatoric strain tensor: Small shifts in spot relative positions  $\rightarrow$  Crystal deformation at constant volume (~ 1 x10<sup>-4</sup> accuracy)

## Laue pattern and energy scanning analysis

# Experimental

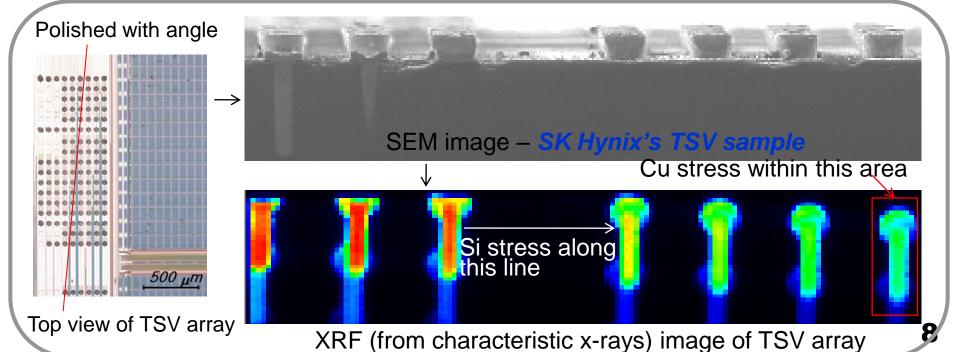

💠 Sample

Hynix: 20 µm TSV diameter, 90 µm pitch, 90 µm height

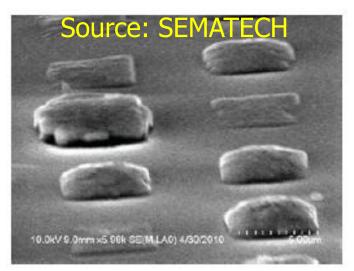

**SEMATECH**: 5.5 µm TSV diameter, 80 µm pitch, 50 µm height

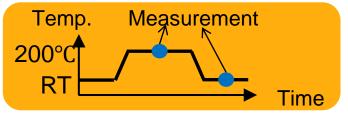

Condition of measurement

- Measurement of stress for : Si, Cu TSV

- Thermal treatment: in situ at 200 °C (SK Hynix)

ex situ post-annealed (200 °C for 1 hour) sample (SK Hynix)

ex situ post-annealed (350 °C for 30 mins) - SEMATECH

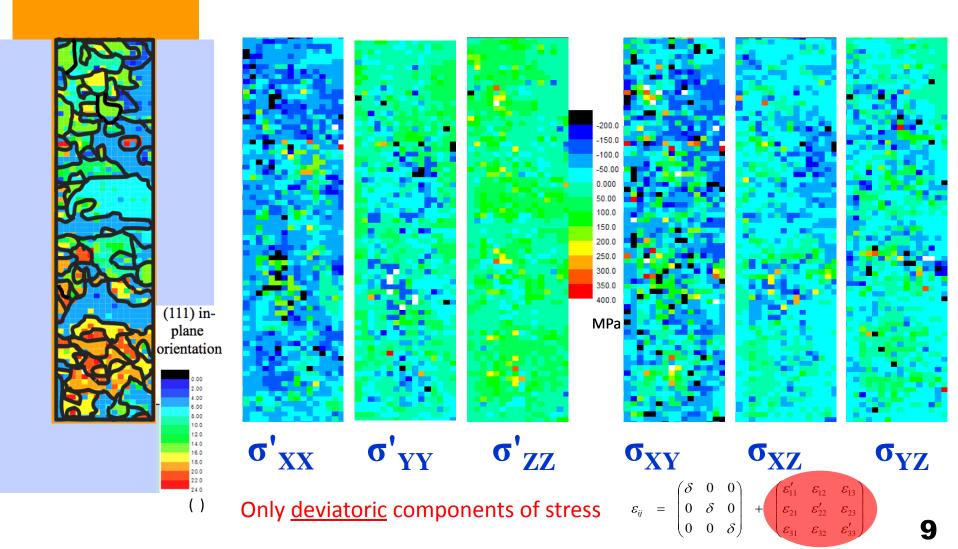

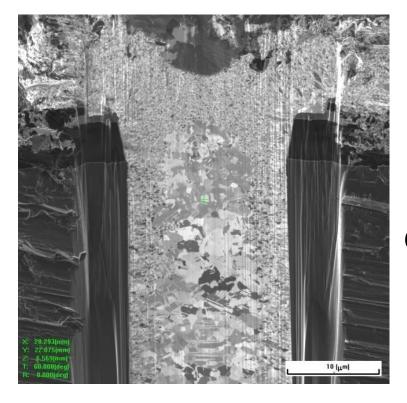

## Cu Stress State in TSV – SK Hynix - Post Annealed Sample (measure at RT)

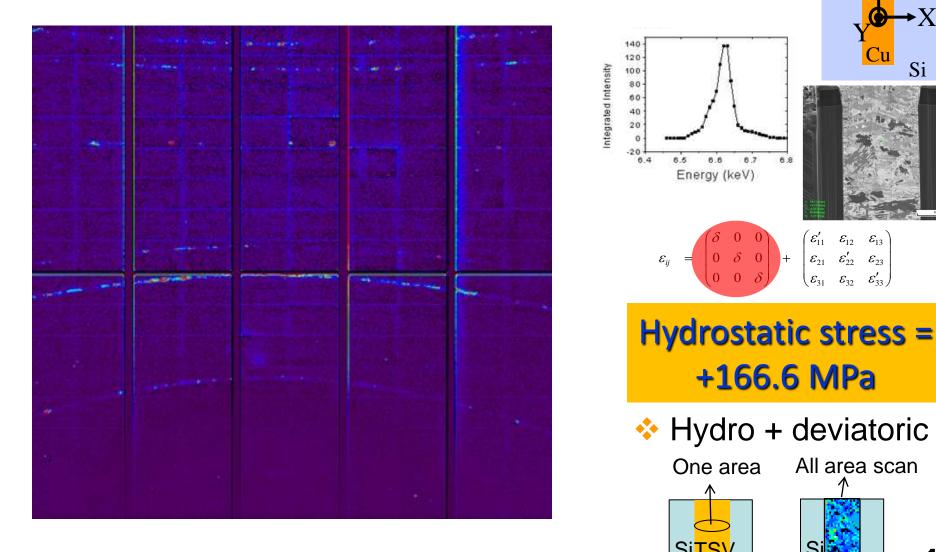

#### Cu Hydrostatic Stress State in TSV – SK Hynix - Post Annealed Sample (measure at RT)

10

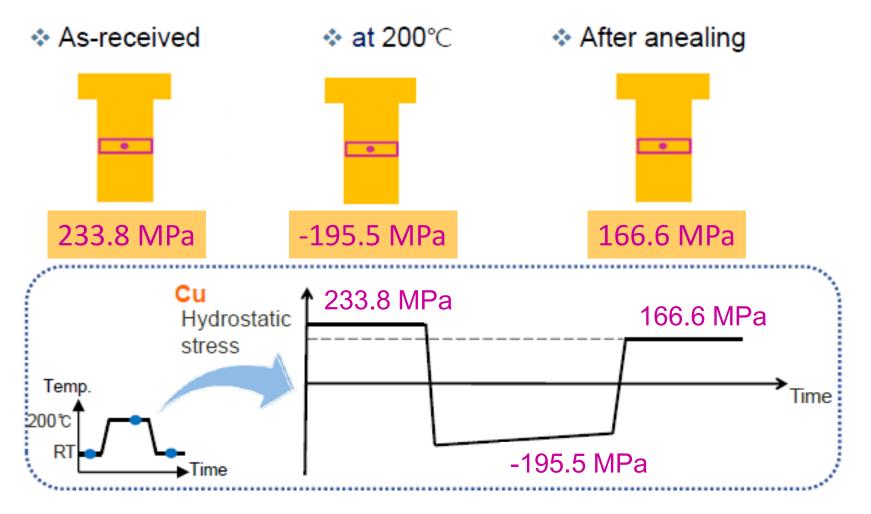

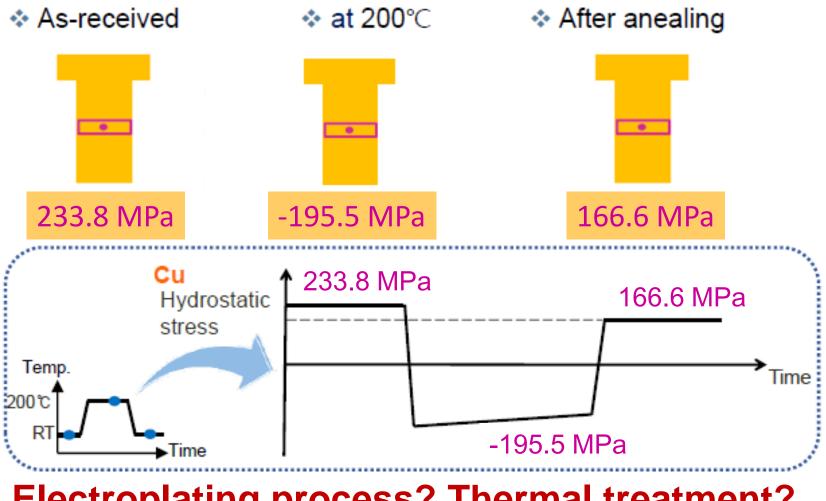

# **Stress Evolution in Cu TSV – SK Hynix**

#### Cu hydrostatic stress

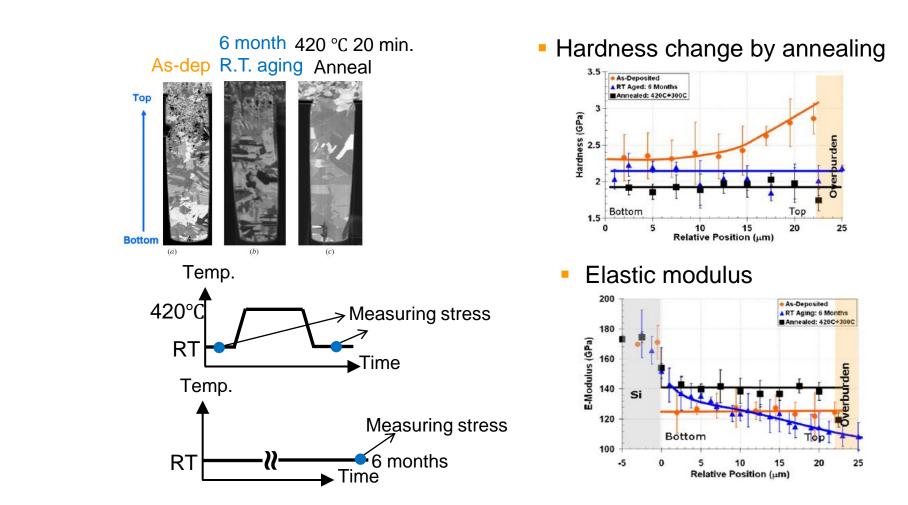

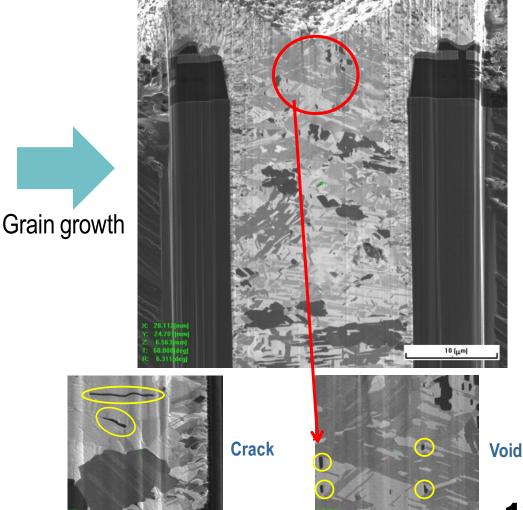

#### <u>High Tensile in As-Received</u> → Cu RT Grain Growth

Decreasing hardness  $\rightarrow$  Cu stress toward more tensile stress after annealing and R. T. aging.

• Okoro et. al., J. Micromech. Microeng. (2010)

#### Microstructure change of Cu during annealing leads to <u>tensile stress</u> – SK Hynix

#### As received

#### 200°C 1hr annealing

13

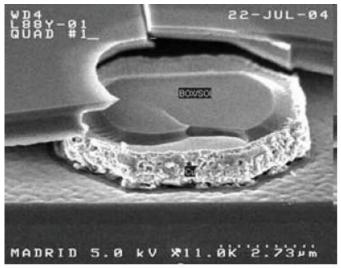

# <u>Compressive</u> Hydrostatic Stress in Cu TSV during Annealing

#### Cu TSV Protrusions:

- Popping out, bulging out during high-temp processing steps

- Cracking/flaking of dielectrics

over Cu TSV and open vias to

above metallization lines

→ Integration issues as well as serious reliability concerns!

Copper expansion can fracture the oxide layer above. (Source: Tezzaron)

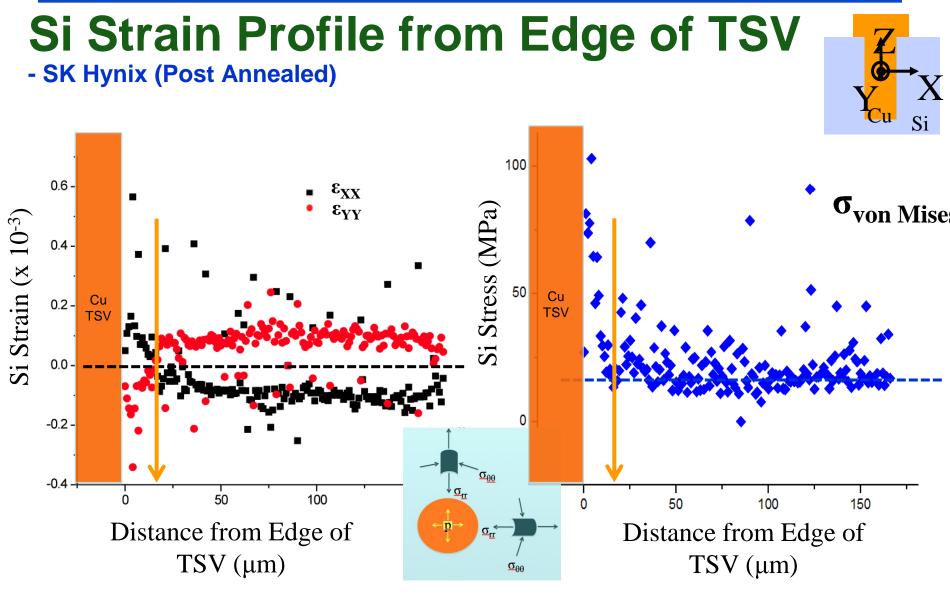

#### Si Stress State in TSV – SK Hynix (Post Annealed)

Y Axis Title

#### Si Keep-Away Zone:

<u>SK Hynix</u>: 17 μm

# → Reduce as-received Cu TSV high tensile stress!!

Electroplating process? Thermal treatment? Reduce Cu RT grain growth?

- Synchrotron X-ray submicron diffraction (white + monochromatic beam) has proven to be a powerful tool to measure stress states in TSV <u>in situ</u> and while the Cu via is still <u>buried under Silicon</u>

- <u>Cu stress state</u> is mostly in tensile and considerable shear stresses at the post-annealed state:

- Comparison SK Hynix vs. SEMATECH samples → RT grain growth leads to high tensile stress in the as-received state

- How to reduce stress-induced reliability/integration → reduce Cu hydro stress in the as-received state

- <u>Stress in Si surrounding Cu TSV</u> was found to follow Cu hydrostatic stress: higher Cu hydrostatic stress → higher Si stress → larger "keep-away zone"

- Si stress in array of TSV's  $\rightarrow$  important for design/layout

- Stress scanning from the top would be valuable → to optimize layout!

# Acknowledgements

#### Director, Los Alamos National Laboratory (LANL) Laboratory Director's Research Directions (LDRD) Fellowship: LDRD/X93V DOE, Office of Science, Office of Basic Energy Sciences

#### ADVANCED LIGHT SOURCE (ALS), ERNEST ORLANDO LAWRENCE BERKELEY NATIONAL LABORATORY U.S DOE, OFFICE OF BASIC ENERGY SCIENCES CONTRACT NO (DE-AC02-05CH11231)

# THANK YOU!