## **Monolithic 3D DRAM Technology**

Deepak C. Sekar, Brian Cronquist, Israel Beinglass, Paul Lim, Zvi Or-Bach

15<sup>th</sup> June 2011

## Outline

## Status of the DRAM industry today

## Monolithic 3D DRAM

## Implications and risks of the technology

## > Summary

## Outline

## Status of the DRAM industry today

## DRAM makers fall in the "endangered species" category

| 1996                                                                                                                          |                                                                                                                                          | 2010                                                                           |                                     |  |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------|--|

| 24 key DRAM players                                                                                                           |                                                                                                                                          | 9 key DRAM players                                                             |                                     |  |

| Samsung<br>Micron<br>NEC<br>Mitsubishi<br>Fujitsu<br>TI-Acer<br>Powerchip<br>Winbond<br>IBM<br>Motorola<br>Seiko Epson<br>UMC | Hyundai<br>Siemens<br>Hitachi<br>Toshiba<br>LG Semicon<br>Vanguard<br>ProMOS<br>Oki<br>TI<br>Matsushita<br>Nippon Steel<br>Mosel Vitelic | Samsu<br>Hynix<br>Micro<br>Elpid<br>Nany<br>Inoter<br>Powerc<br>ProMC<br>Winbo | x<br>n<br>a<br>a<br>ra<br>hip<br>OS |  |

#### Why? What are the challenges? We'll see in the next few slides

## **Reason 1: Profitability**

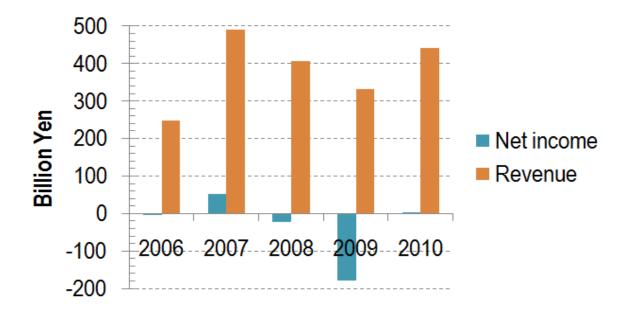

#### Financials of a top-tier DRAM vendor (Elpida) vs. fiscal year

DRAM has not been a profitable business in the near past

➢ Balance sheets of most companies' DRAM businesses similar to above ⊗

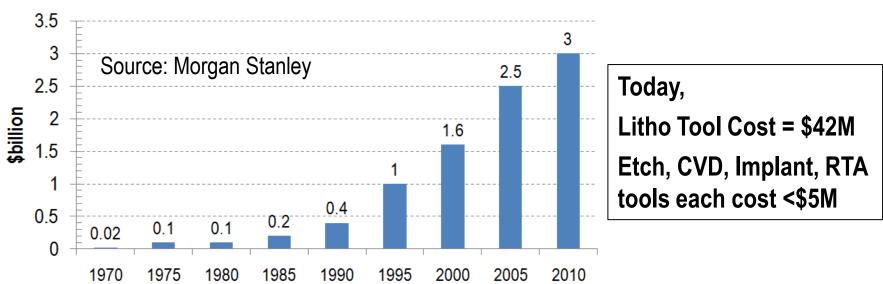

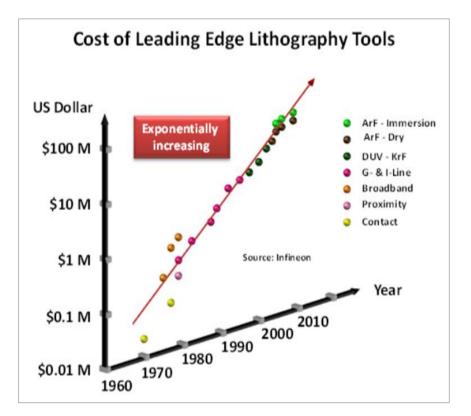

## **Reason 2: Large fab cost for scaling-down**

Cost of a DRAM Fab

- > Scaling-down  $\rightarrow$  lower cost per bit  $\rightarrow$  but huge litho and fab investment

- → Hard for unprofitable companies to fund scaled-down fabs. But if they don't fund new "scaled-down" fabs and others do → bad cost per bit → profitability even worse

Monolith( MonolithIC 3D Inc. Patents Pending

## Reason 3:

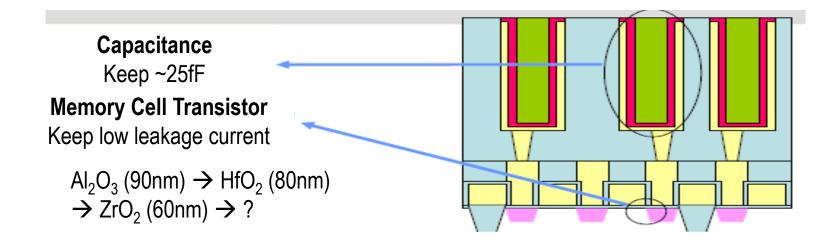

## Scaling-down the stacked capacitor challenging

| Source: ITRS 2010   | 45nm  | 32nm  | 22nm  | 15nm  | 10nm  |

|---------------------|-------|-------|-------|-------|-------|

| Dielectric constant | 40    | 50    | 60    | 65    | 70    |

| Aspect ratio        | 47:1  | 56:1  | 99:1  | 147:1 | 193:1 |

| EOT                 | 0.8nm | 0.6nm | 0.5nm | 0.3nm | 0.2nm |

#### **Requires >150:1 aspect ratios and exotic new high-k dielectrics!**

## Reason 4:

## The cell transistor needs major updates on scaling-down

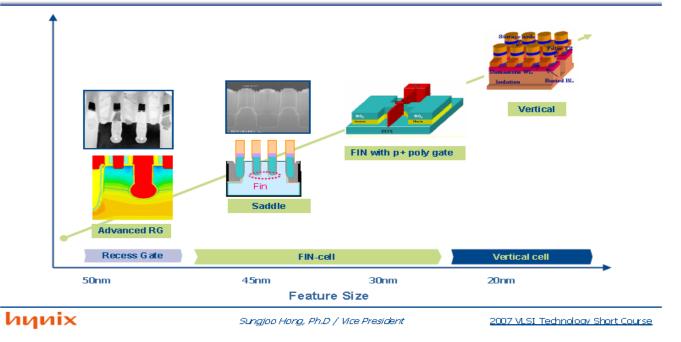

#### **Cell Transistor – Possible Scenario**

A major new transistor every generation or two!

100nm Planar  $\rightarrow$  80nm RCAT  $\rightarrow$  60nm S-RCAT  $\rightarrow$  35nm Finfet (?)  $\rightarrow$  20nm Vertical (?)

## To recap,

## Things don't look good for DRAM vendors because

(1) Low profitability

**Related**

- (2) Cost of scaled-down fabs

- (3) Scaling-down stacked capacitor

- (4) Cell transistor scaling-down

#### Common theme → Scaling-down

Is there an alternative way to reduce DRAM bit cost other than scaling-down?

Focus of this presentation

## Monolithic 3D DRAM

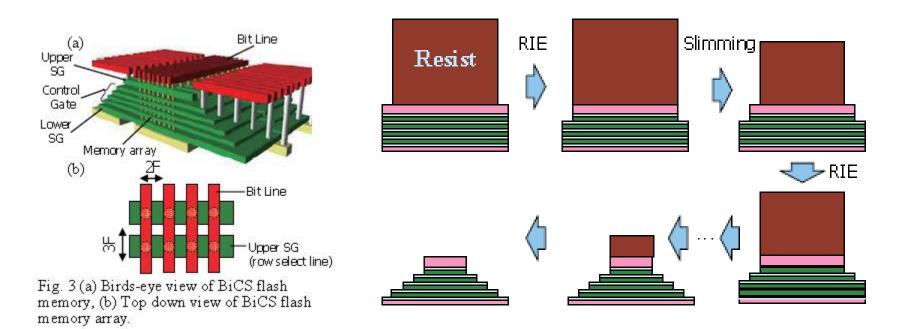

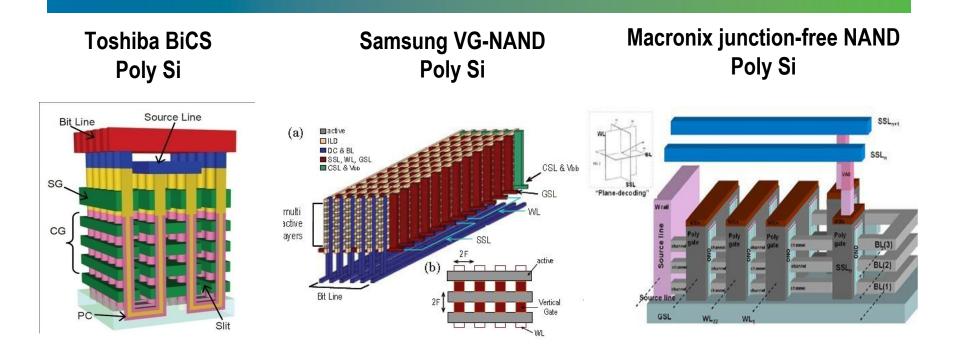

## Key technology direction for NAND flash: Monolithic 3D with shared litho steps for memory layers

#### To be viable for DRAM, we require

- $\succ$  Single-crystal silicon at low thermal budget  $\rightarrow$  Charge leakage low

- > Novel monolithic 3D DRAM architecture with shared litho steps

MonolithIC 3D Inc. Patents Pending

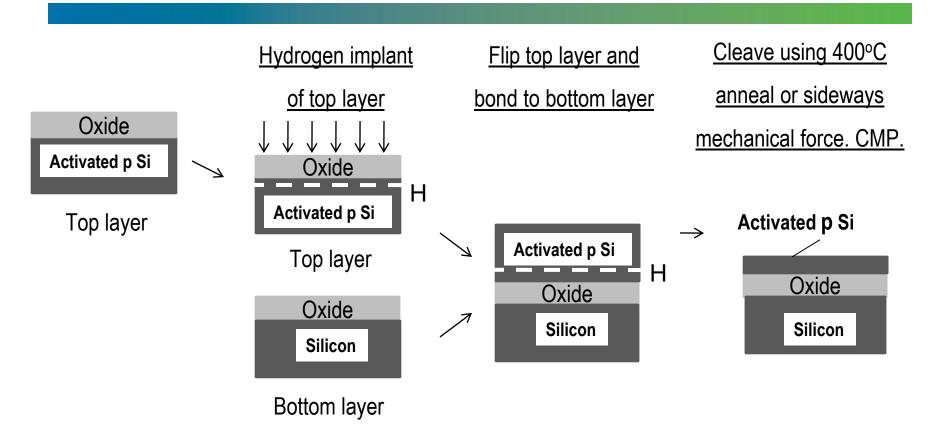

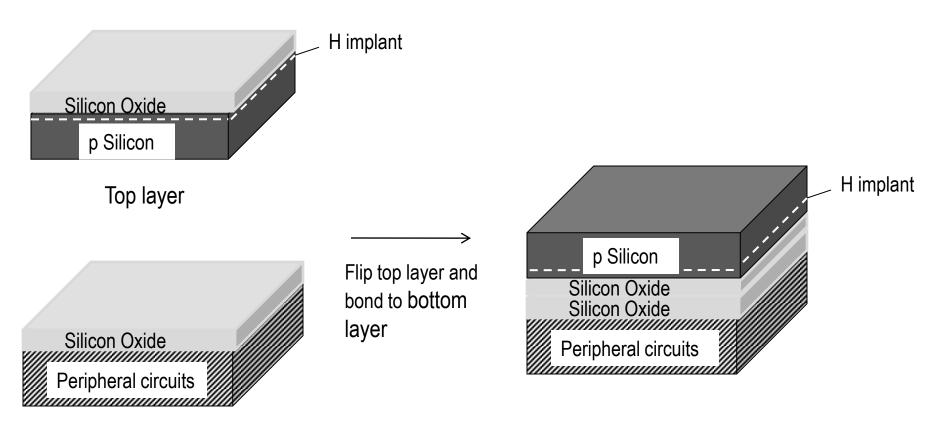

## Single crystal Si at low thermal budget

> Obtained using the ion-cut process. It's use for SOI shown above.

> Ion-cut used for high-volume manufacturing SOI wafers for 10+ years.

MonolithIC 3D Inc. Patents Pending

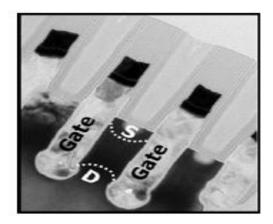

# Double-gated floating body memory cell well-studied in Silicon (for 2D-DRAM)

#### Hynix + Innovative Silicon VLSI 2010

- > 0.5V, 55nm channel length

- 900ms retention

- Bipolar mode

- > 2V, 85nm channel length

- > 10ms retention

- MOSFET mode

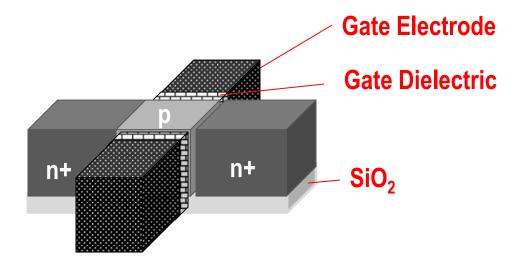

## **Our novel DRAM architecture**

Innovatively combines these well-studied technologies

- > Monolithic 3D with litho steps shared among multiple memory layers

- Stacked Single crystal Si with ion-cut

- > Double gate floating body RAM cell (below) with charge stored in body

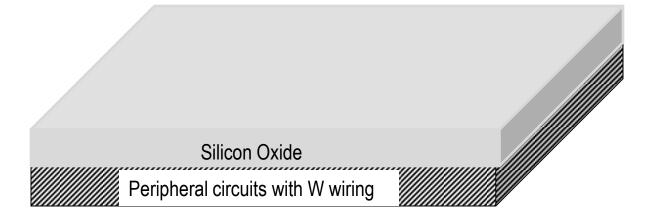

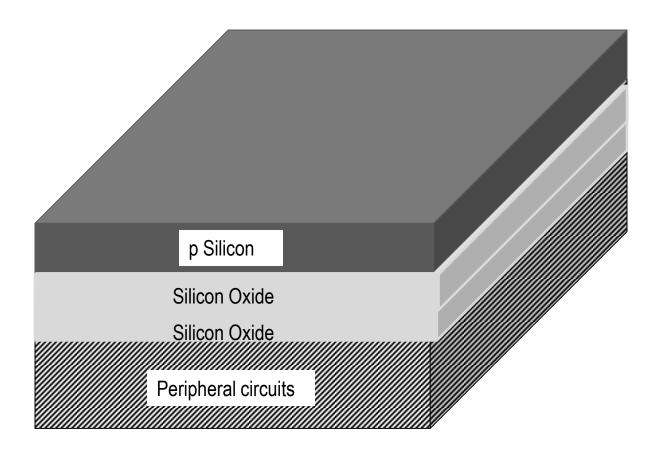

## Process Flow: Step 1 Fabricate peripheral circuits followed by silicon oxide layer

## Process Flow: Step 2 Transfer p Si layer atop peripheral circuit layer

Bottom layer

## Process Flow: Step 3 Cleave along H plane, then CMP

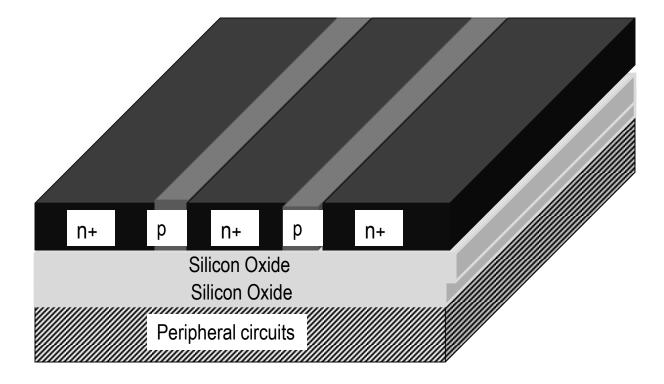

## Process Flow: Step 4 Using a litho step, form n+ regions using implant

## Process Flow: Step 5 Deposit oxide layer

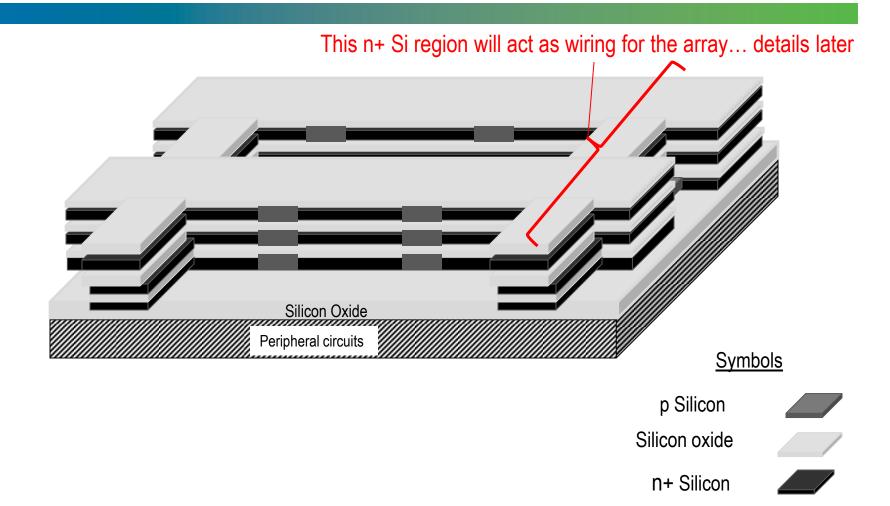

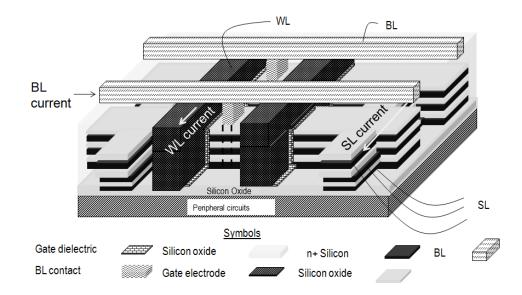

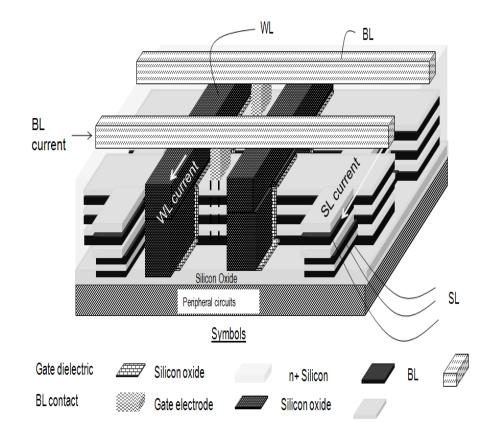

#### **Process Flow: Step 6**

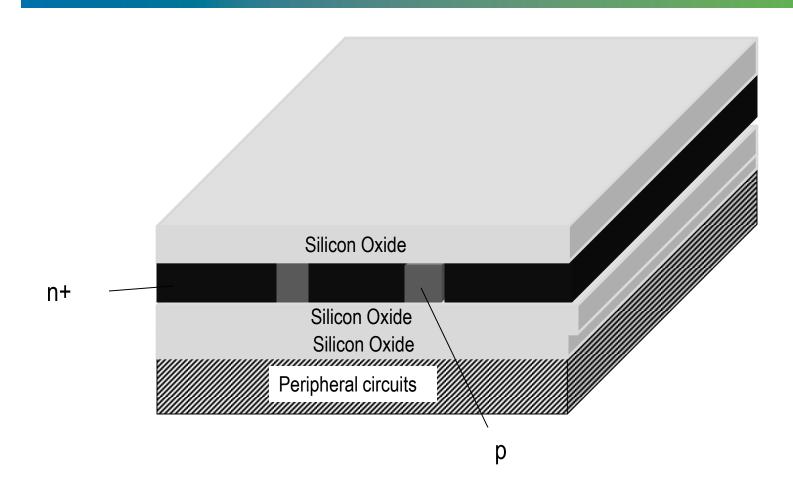

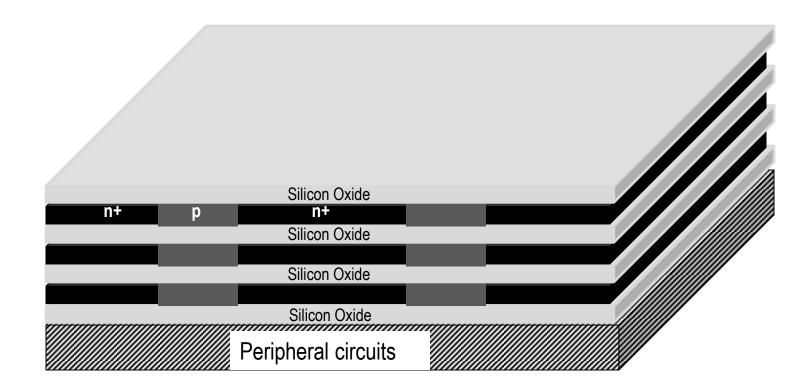

#### Using methods similar to Steps 2-5, form multiple Si/SiO<sub>2</sub> layers, RTA

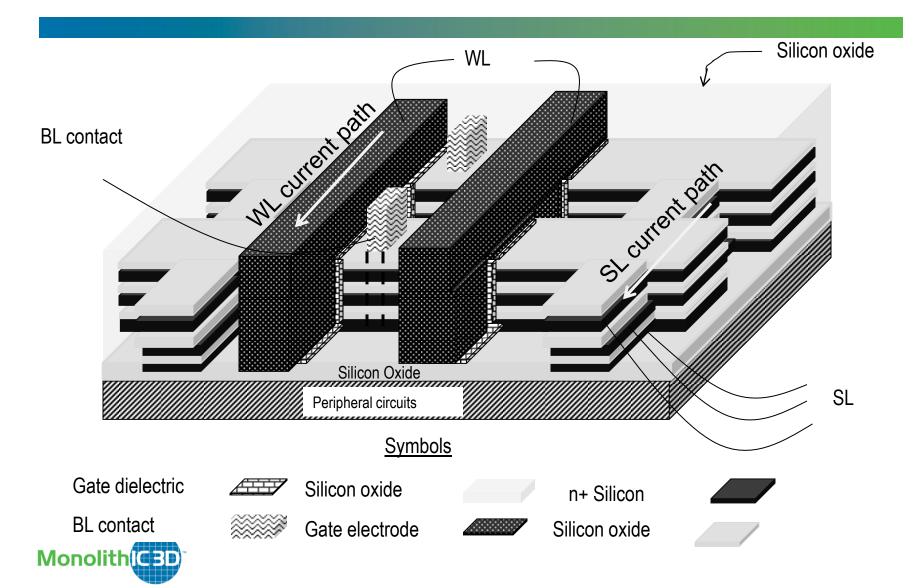

## Process Flow: Step 7 Use lithography and etch to define Silicon regions

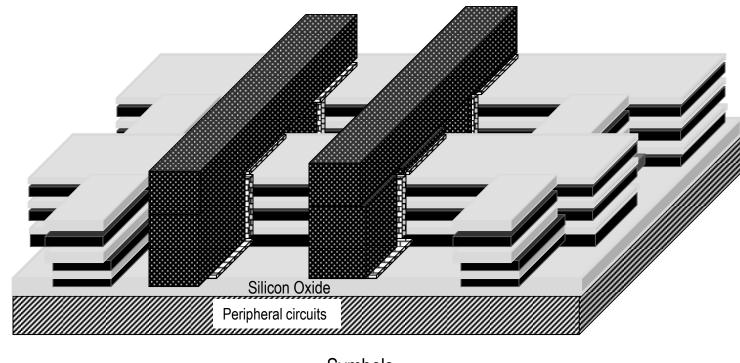

#### **Process Flow: Step 8**

#### Deposit gate dielectric, gate electrode materials, CMP, litho and etch

#### Symbols

Gate electrode

Gate dielectric

## Process Flow: Step 9 Deposit oxide, CMP. Oxide shown transparent for clarity.

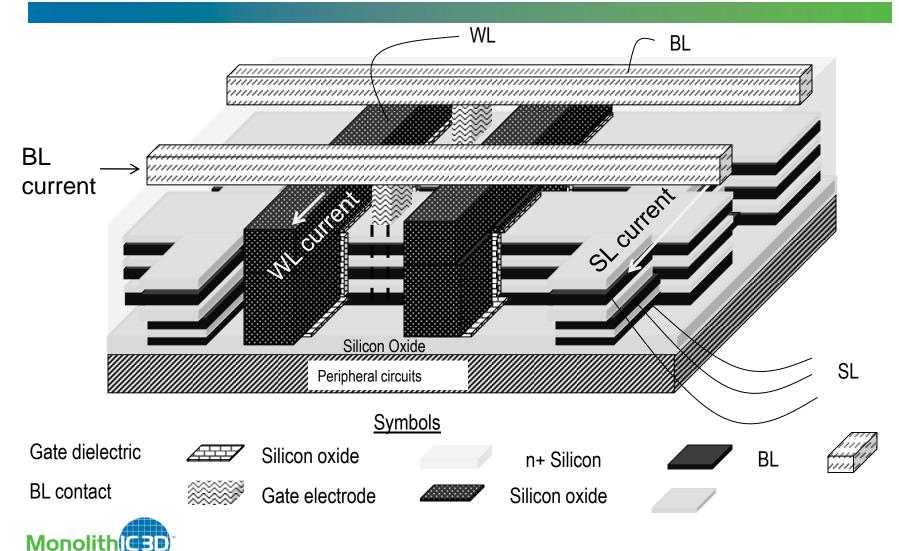

#### **Process Flow: Step 10**

#### Make Bit Line (BL) contacts that are shared among various layers.

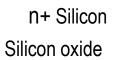

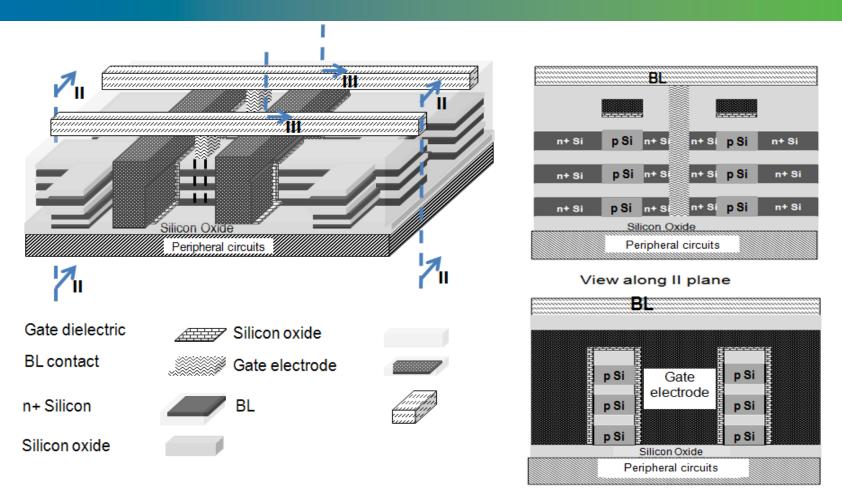

## Process Flow: Step 11 Construct BLs, then contacts to BLs, WLs and SLs at edges of memory array using methods in [Tanaka, et al., VLSI 2007]

## Some cross-sectional views for clarity. Each floating-body cell has unique combination of BL, WL, SL

View along III plane

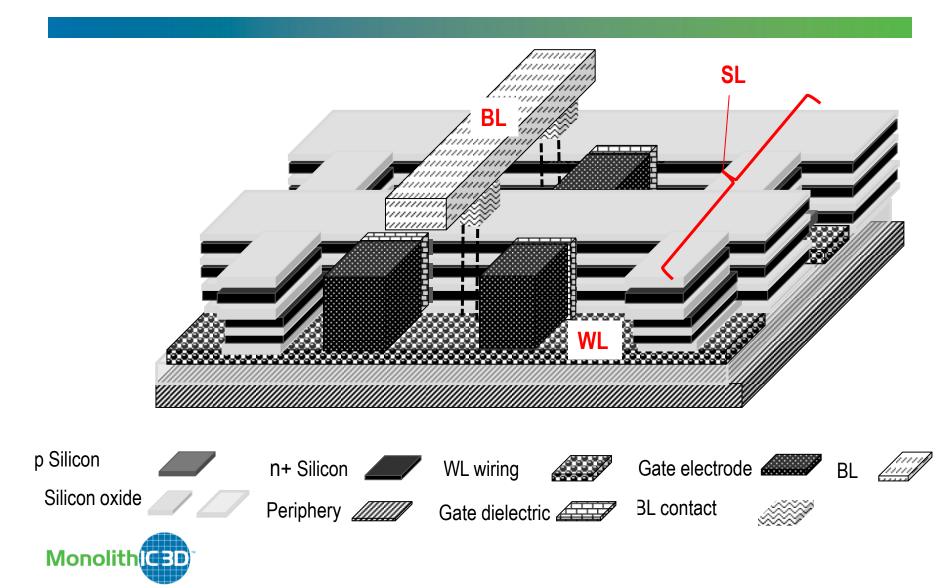

## A different implementation: With independent double gates

## Outline

## > Implications and risks of the technology

## **Density estimation**

|                       | Conventional stacked<br>capacitor DRAM | Monolithic 3D DRAM with<br>4 memory layers                             |

|-----------------------|----------------------------------------|------------------------------------------------------------------------|

| Cell size             | 6F <sup>2</sup>                        | Since non self-aligned, 7.2F <sup>2</sup>                              |

| Density               | X                                      | 3.3x                                                                   |

| Number of litho steps | 26<br>(with 3 stacked cap.<br>masks)   | ~26<br>(3 extra masks for memory layers,<br>but no stacked cap. masks) |

# 3.3x improvement in density vs. standard DRAM, but similar number of critical litho steps!!!

Negligible prior work in Monolithic 3D DRAM with shared litho steps, poly Si 3D doesn't work for DRAM (unlike NAND flash) due to leakage

## Scalability

- ➢ Multiple generations of cost per bit

improvement possible

(eg) 22nm 2D →

22nm 3D 2 layers →

22nm 3D 4 layers → ...

- > Use same 22nm litho tools for 6+

years above. Tool value goes down

50% every 2 years → Cheap ☺

- Avoids cost + risk of next-gen litho

## Reduces or avoids some difficulties with scaling-down

#### EUV delays and risk

**Capacitor manufacturing**

(EETimes 2002) "EUV to be in production in 2007"

(EETimes 2003) "EUV to be leading candidate for the 32nm node in 2009"

(EETimes 2004) "<u>EUV to be pushed out to 2013</u>"

(EETimes 2010) "EUV late for 10nm node milestone in 2015"

|    | 45<br>nm | 32<br>nm | 22<br>nm | 15<br>nm | 10<br>nm |

|----|----------|----------|----------|----------|----------|

| 3  | 40       | 50       | 60       | 65       | 70       |

| AR | 47       | 56       | 99       | 147      | 193      |

**Continuous transistor updates**

Planar  $\rightarrow$  RCAT  $\rightarrow$  S-RCAT  $\rightarrow$  Finfet  $\rightarrow$  Vertical devices

## **Risks**

#### Floating-body RAM

Retention, reliability, smaller-size devices, etc

#### Cost of ion-cut

Supposed to be <\$50-75 per layer since one implant, bond, cleave, CMP step.

But might require optimization to reach this value.

## Outline

## **Summary of Monolithic 3D DRAM Technology**

Monolithic 3D with shared litho steps Single crystal Si Floating body RAM *Under development...*

- > 3.3x density of conventional DRAM, but similar number of litho steps

- > Scalable (eg) 22nm 2D → 22nm 3D 2 layers → 22nm 3D 4 layers → ...

- > Cheap depreciated tools, less litho cost + risk, avoids many cap. & transistor upgrades

- **<u>Risks</u>** = Floating body RAM, ion-cut cost

## **Backup slides**

## A note on overlay

- Implant n+ in p Si regions layer-bylayer, then form gate

non self-aligned process

- ITRS <20% overlay requirement</li>

ASML 1950i = 3.5nm overlay for

38nm printing. <10% overlay.</li>

- So, gate length = 1.2F. Penalty of

0.2F for non-self-aligned process

## **Bias schemes for floating body RAM**

#### Bipolar Mode [S. Alam, et al, TED 2010]

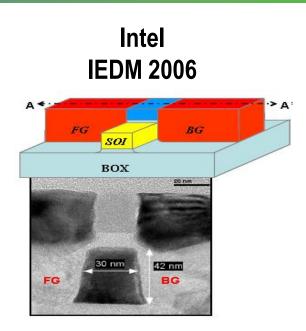

#### MOS Mode [Intel, IEDM 2006]

|         | $V_{o}$ | $V_{FG}$ | VBG  | Vs |

|---------|---------|----------|------|----|

| Program | 2       | 1.5      | -1.5 | 0  |

| Erase   | -1      | 0.7      | -1.5 | 0  |

| Read    | 0.2     | 0.7      | -1.5 | 0  |

| Hold    | 0       | -1       | -1.5 | 0  |

## **Contact processing with shared litho steps**

### Similar to Toshiba BiCS scheme [VLSI 2007]