# Ion Implant Applications to Enable Advances in Semiconductor Technologies

K.V. ("Vivek") Rao, Ph.D. Applied Materials, Inc.

NCCAVS Junction Technologies User Group Meeting October 20, 2017

Applied Materials External Use

# Outline

- Technology Scaling Challenges

- Implant Damage and Profile Engineering

- Stress Memorization Technique

- Fin Damage & Strain Engineering

- Work Function Engineering

- Contact Engineering

- Uniformity Improvement with Implants

- Summary

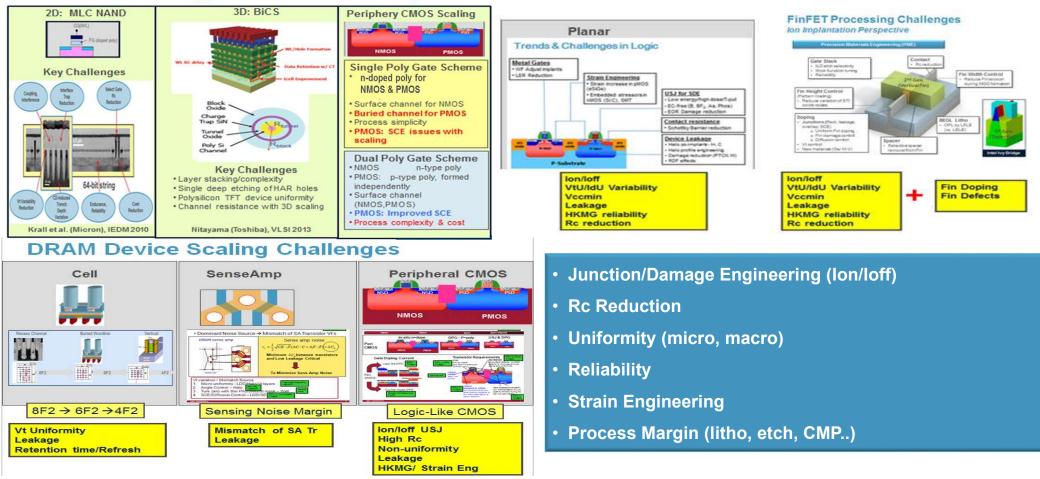

# **Key Device Scaling Challenges**

#### NAND Technology Trend and Challenges

#### Logic/Foundry Device Scaling Challenges

3 | External Use

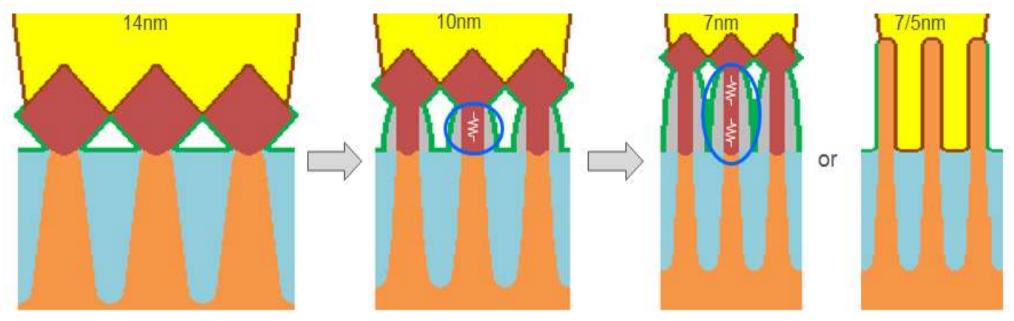

# **Transistor Roadmap**

| Node          | Ν |                   | N+1 |                | N+2                                             |   | N+3        |               |

|---------------|---|-------------------|-----|----------------|-------------------------------------------------|---|------------|---------------|

| Architecture  |   | FinFET            |     | Scaled tall ve | rtical FinFE                                    | T | Gate All A | Around (hGAA) |

| Channel       |   | Silicon           |     |                | SiGe p-channel Si / SiGe superlattice           |   |            |               |

| Extension I/I |   | Beam Line         |     |                | PLAD<br>Non-line-of-sight doping                |   |            |               |

| Contact       |   | Trench Contact    |     |                | Replacement Contact / Wrap Around Contact (WAC) |   |            |               |

| Contact I/I   |   | Ge PSI, Beam line |     |                | Beam line / PLAD, SBH                           |   |            |               |

Architecture and materials changes with CMOS scaling

→ incorporate damage engineering and conformal implant solutions

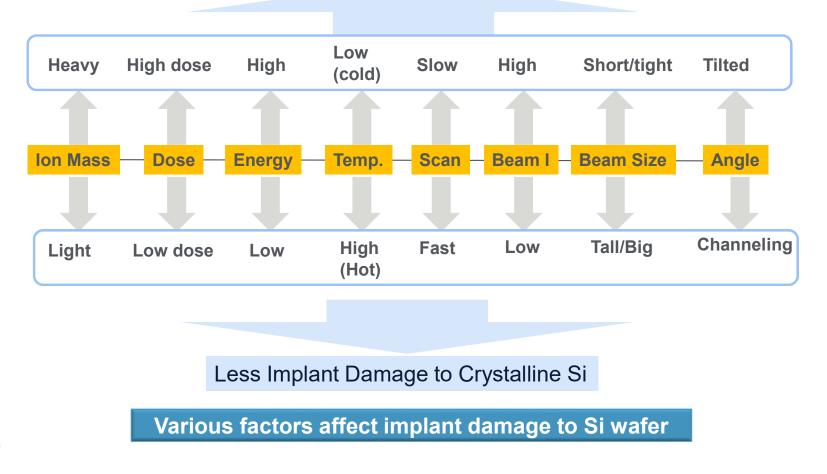

# **Implant Damage Engineering Knobs**

More Implant Damage to Crystalline Si

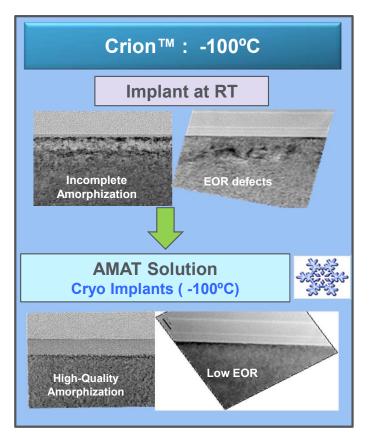

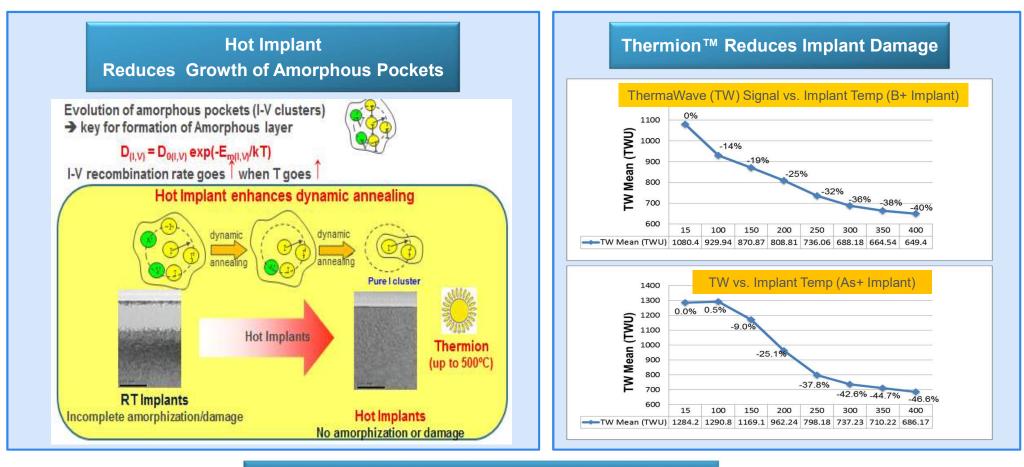

# **Damage Engineering with Thermal Implants**

# **Damage Engineering delivers:** (a) improved activation (b) reduced damage (c) reduced variability

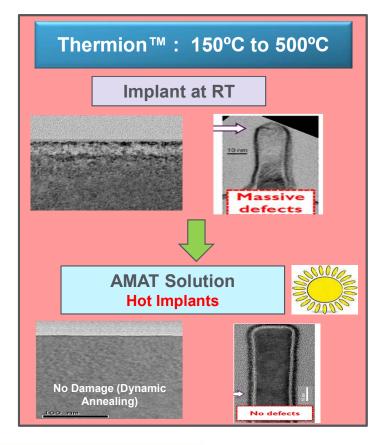

# **Thermion™ (Hot Implants): Damage Reduction**

Damage reduced as implant temp is increased

7 | External Use

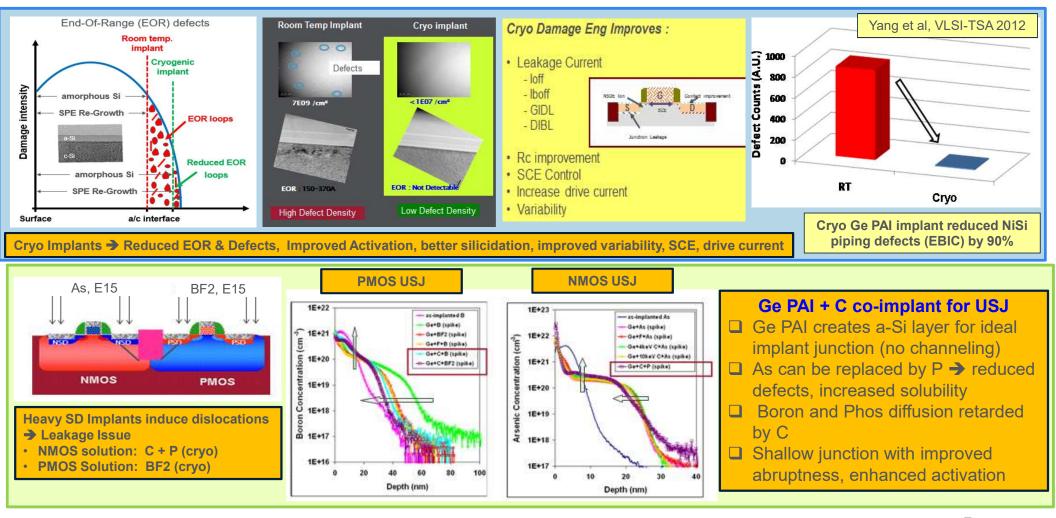

### Source/Drain Engineering: Cryo & Co-Implant Solutions

8 | External Use

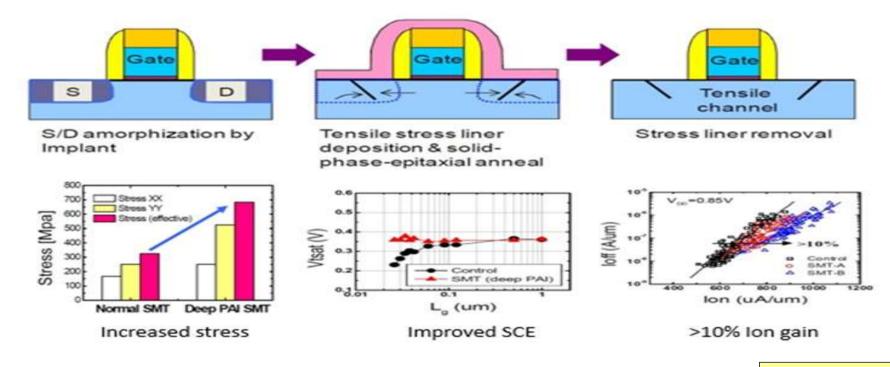

# **Strain Engineering for Planar NFET**

[1] Lim et al, IEDM 2010

32nm NFET SD stress memorization technique (SMT) with deep amorphization with cryo Ge PAI

- Resulted in 10% Ion gain

- Potential application of SMT to n-FinFET

9 | External Use

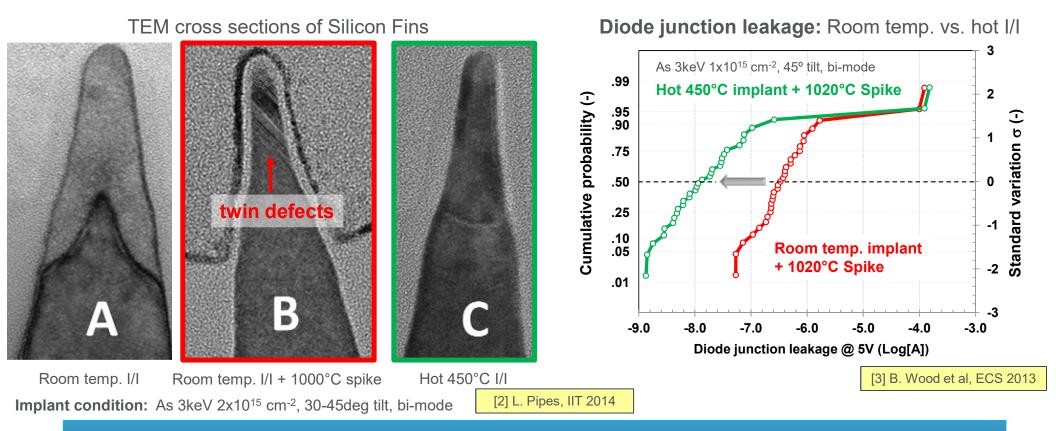

### Si Channel: Hot Implants (As or P) for Extension or WAC

S/D ext or WAC implant can amorphize the fin, which results in twin defects after anneal

Hot implant can eliminate the formation of amorphous Si and twin defects

10 | External Use

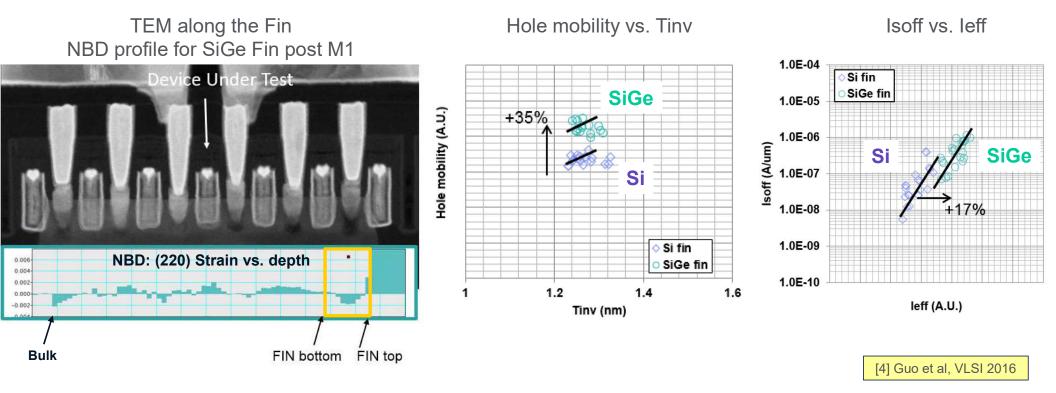

## **P-FinFET: SiGe Channel Performance Benefit over Si**

Strained SiGe results in compressive strain, which results in hole mobility enhancement

17% PFET leff benefit can be observed for SiGe over Si channel for long-channel devices

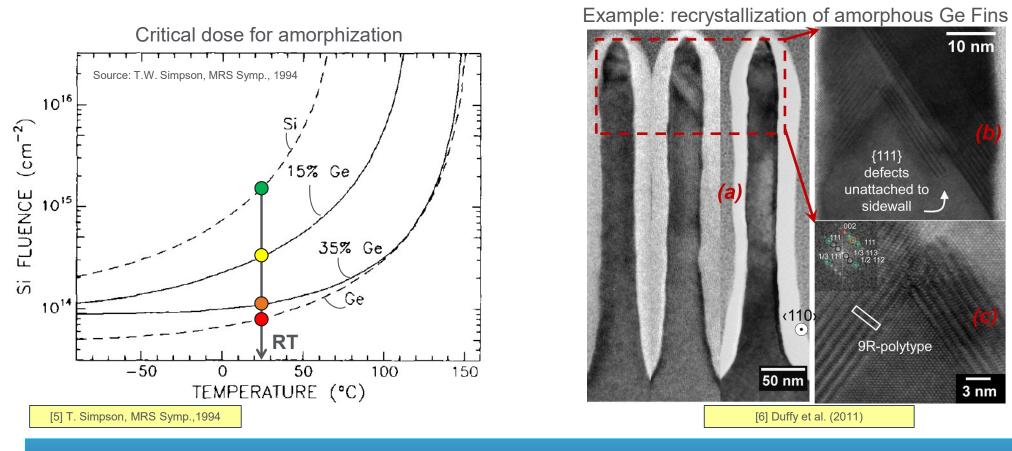

### SiGe Channel: More Sensitive to Amorphization and Defects

10 nm

3 nm

{111}

defects unattached to

sidewall

9R-polytype

111

1/3 111 1/3 113

(110)

[6] Duffy et al. (2011)

50 nm

- Critical dose for amorphization of SiGe<sub>0.3</sub> is only ~ $10^{14}$  cm<sup>-2</sup>; for silicon it is ~ $10^{15}$  cm<sup>-2</sup>

- This makes SiGe fins even more vulnerable for amorphization and defects than Si fins

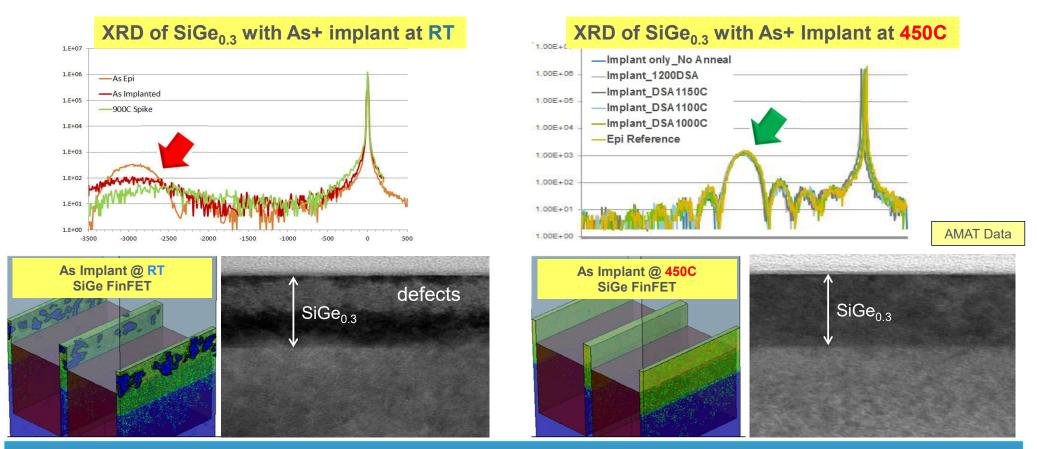

#### SiGe Channel: Hot Implant to Avoid Relaxation & Defects

RT implant → SiGe channel strain is lost. Even after 900°C spike anneal, strain does not recover

Hot 450°C implant → channel strain is retained. SiGe has not relaxed

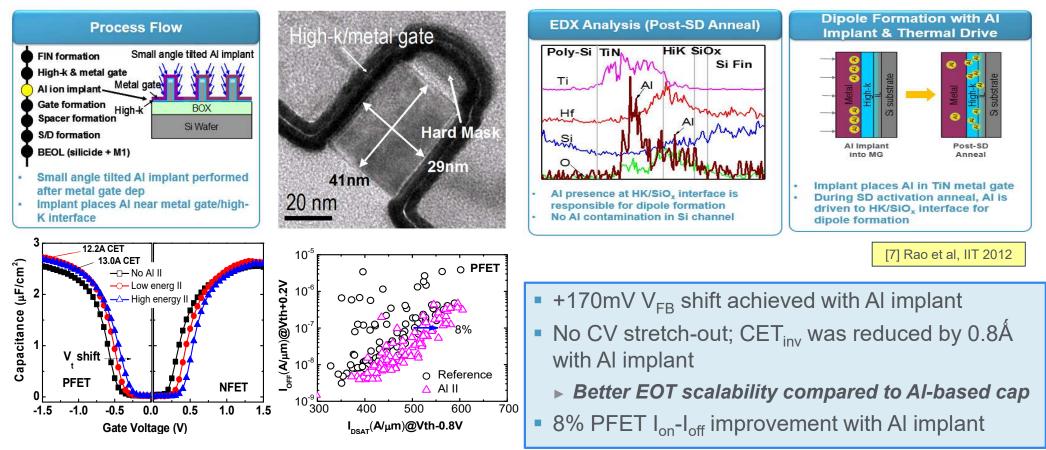

### **HKMG Work Function Engineering** *Multi-Vt Offerings for SOC by Changing the AI+ implant conditions*

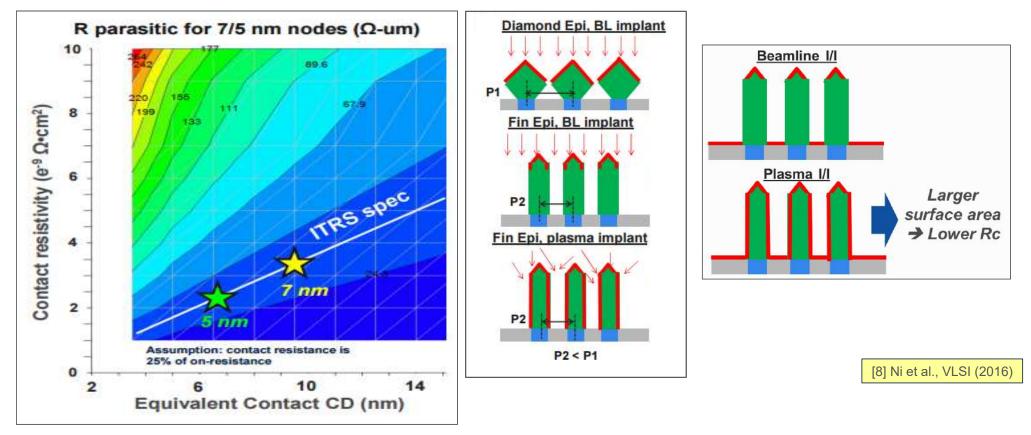

# **Impact of Scaling on External Resistance**

- Fin pitch scaling reduces contact area  $\rightarrow$  increases Rc

- Tall fin height results in increase of S/D resistance (RSD)

- Need Wrap-Around-Contact (WAC) to break trend of increasing Rc and RSD

- Requires uniform top / sidewall doping solutions for NFET & PFET

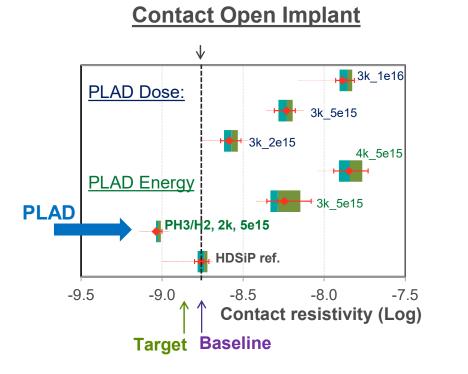

# PLAD for n-FinFET Contacts: Future Requirements for Rc

High aspect ratio (HAR) contacts → Wrap-around contacts (WAC) → PLAD conformal doping

16 | External Use

# Plasma Doping (PLAD) for nFET Contact Implant

HD:SiP epi (High Dose) 2.5e21/cm<sup>3</sup> P PMD Dep **RMG** Anneal Contact pattern, open, and strip PLAD PH3 implant  $\rightarrow$  wet clean (SPM&SC1) Siconi pre-clean/Ti/TiN Dep DSA 800°C contact anneal Number of contact holes in the chain ~ 13,000 Metal nar CC length N+ 100 nm

- PLAD PH3 doping into contact resulted in NMOS contact resistivity,  $\rho c < 1E-9 \Omega.cm^2$

- High Dose: May cause P agglomeration

- High E: May amorphize Si beyond SPE regrowth and TiSi<sub>x</sub> consumption

[8] Ni et al.,

VLSI (2016)

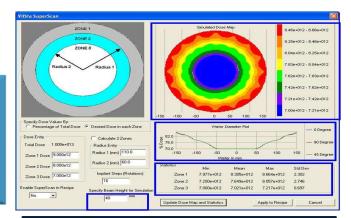

#### SuperScan for Yield Improvement

Ability to Vary Dose Across Wafer

#### Custom dose patterns to Improve device performance & die yield

- Compensates for CMP/etch/thin film/thermal variations

- Designed for R&D and production apps

- Independent NMOS & PMOS Vt and Id uniformity tuning

- Available on VIISta HC, MC and HE implanters

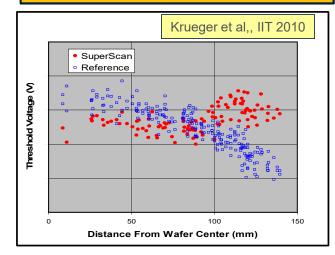

#### Custom dose pattern with SuperScan

28nm PMOS Vt radial uniformity improvement with halo implant with SuperScan

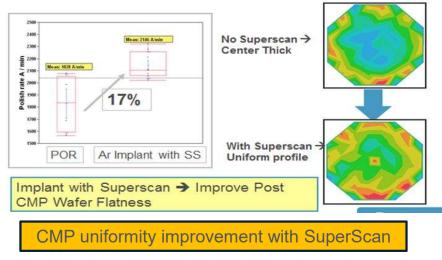

#### STI CMP - HDP Oxide

Macro Rate Polish Rate Modulation with Superscan

18 | External Use

### **Summary**

- Changes in architecture and materials being incorporated with technology scaling

- Ion implant solutions enable technology scaling

- Implant damage engineering is key to improve device performance, reduce variability and improve yield

- Optimization of ion implant conditions for various applications; examples:

- Cryo/co-implants for profile and junction engineering

- Stress Memorization Technique for planar CMOS

- Hot implants for fin defect reduction and reduced leakage

- HKMG work function engineering for Vt tuning

- ▶ Rc reduction with contact implants (including PLAD for conformal doping for Wrap-Around Contacts)

#### References

- [1] K.Y. Lim et al., 10.1.1, IEDM 2010.

- [2] L. Pipes, IIT 2014.

- [3] B. Wood, ECS Trans. 2013 58(9): 249-256.

- [4] D. Guo et al., VLSI 2016.

- [5] T. W. Simpson, MRS Symposium, 1994.

- [6] R. Duffy et al., APL (2011).

- [7] K.V. Rao et al, IIT 2012, p38-41.

- [8] C. N. Ni et al., VLSI 2016.