#### From The Future Si Technology Perspective: Challenges and Opportunities, Dr. Kinam Kim, Samsung

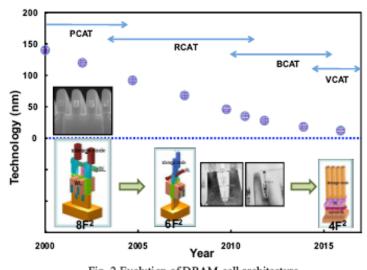

Fig. 2 Evolution of DRAM cell architecture

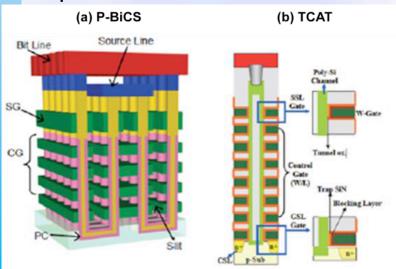

#### Example of vertical NAND structures

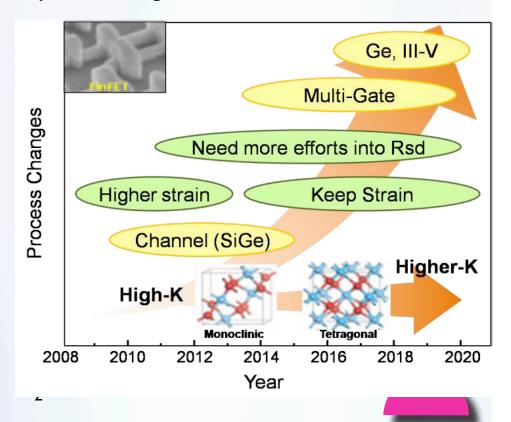

Key technologies for the future Si CMOS era

#### ibs

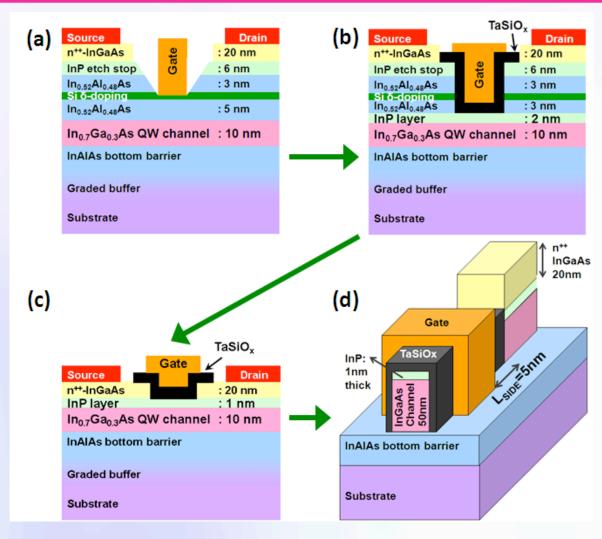

Non-Planar, Multi-Gate InGaAs Quantum Well Field Effect Transistors with High-K Gate Dielectric and Ultra-Scaled Gate-to-Drain/Gate-to-Source Separation for Low Power Logic Applications, Intel

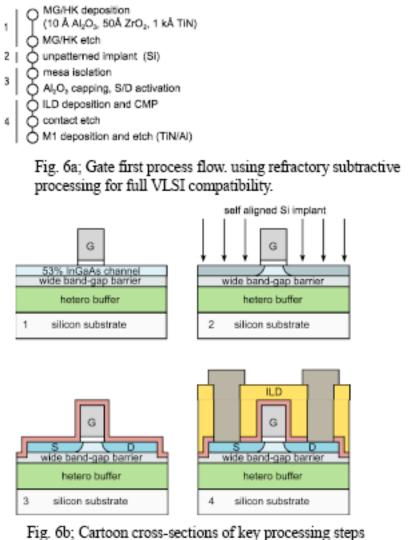

#### Self-aligned III-V MOSFETs heterointegrated on a 200 mm Si substrate using an industry standard process flow, Sematech

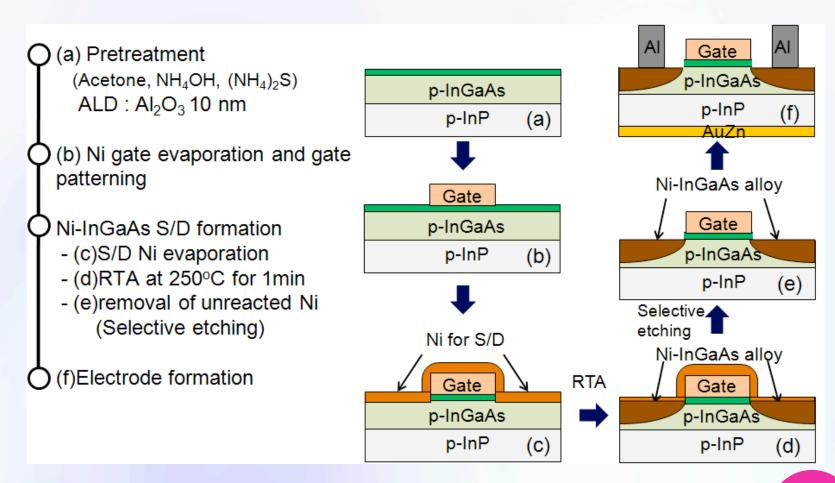

### Self-aligned metal Source/Drain InxGa1-xAs n-MOSFETs using Ni-InGaAs alloy, University of Tokyo

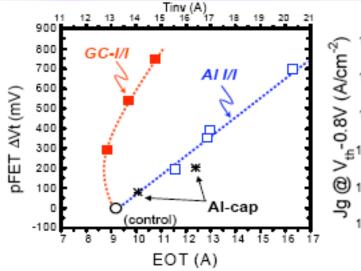

## Physical Origin of pFET Threshold Voltage Modulation by Ge Channel Ion Implantation (GC-I/I), Toshiba & IBM

Room temp. or cryogenic Ge I/I

Re-crystallization anneal

Interfacial layer (IL) formation

Gate dielectric HfO<sub>2</sub> deposition

Metal gate deposition

Fig. 5: pFET  $\Delta V_{TH}$ -EOT plots of Al I/I into IL and GC-I/I. Plots of Al-cap on top of HK are also shown as a reference. Large pFET  $V_{TH}$  shifts can be realized by both cases, however, huge EOT degradation occurs in the Al I/I case similar to Al-cap trend. On the other hand, GC-I/I induces~+500mV  $V_{TH}$  shift with no  $T_{inv}$  increase.

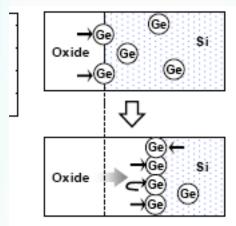

Fig. 19: Schematic of Ge pile-up at IL/Si interface. Ge piled-up at IL/Si interface forms fixed charge/dipoles resulting in enhanced pFET ΔV<sub>TH</sub> in the case of RTO IL process.

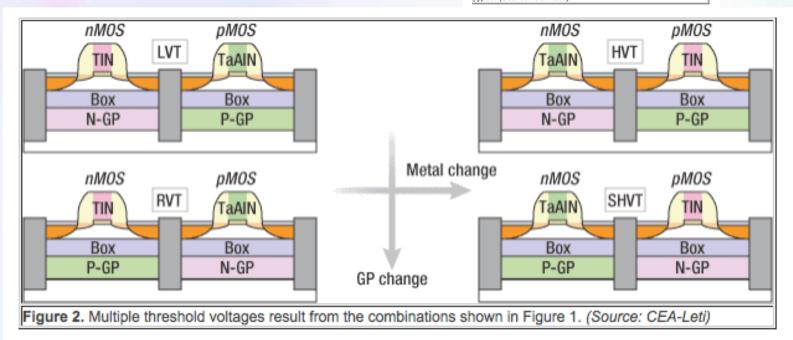

Work-function Engineering in Gate First Technology for Multi-VT Dual-Gate FDSOI CMOS on UTBOX, CEA-

**LETI & STMicroelectronics**

Ground plane implants are In<sup>+</sup> and As+

voltages with two metal workfunctions and two ground plane types, (Source: CEA-Leti)

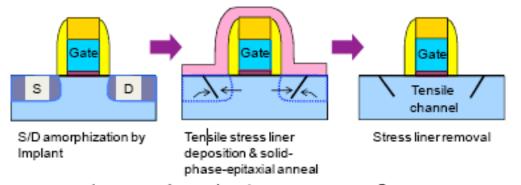

# Novel Stress-Memorization-Technology (SMT) for High Electron Mobility Enhancement of Gate Last High-k/Metal Gate Devices, Samsung

Fig. 1. Schematic S/D SMT process flow.

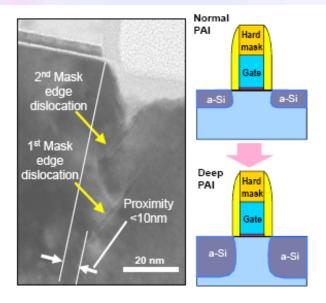

Fig. 4. Mask-edge dislocation image of SMT sample with deep PAI: multiple mask edge defects can be observed.

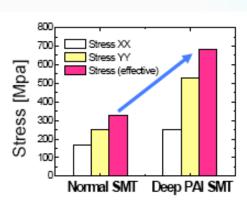

Fig. 5. Simulated SMT-induced channel stress: deep PAI SMT (multiple mask edge dislocation) shows much higher channel stress than the normal shallow PAI SMT (single mask edge dislocation).

# Contact Resistance Reduction to FinFET Source/Drain Using Dielectric Dipole Mitigated Schottky Barrier Height Tuning, Sematech

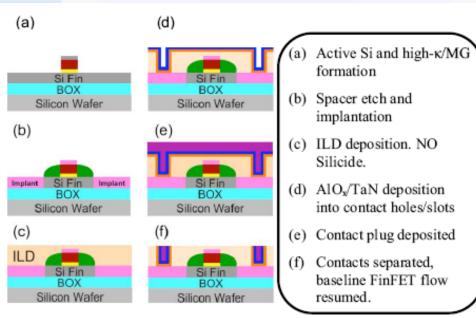

Fig. 3. Cross sectional schematic illustrating FinFET fabrication using DDM-SBH tuning technique.

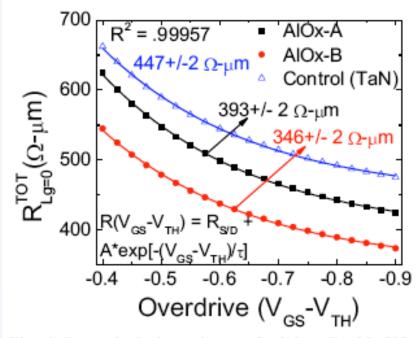

Fig. 6. R<sub>S/D</sub> calculation using method described in [9]. Addition of AlO<sub>x</sub> in the contact hole results in ~25% reduction in R<sub>S/D</sub>. The strong overdrive dependence on R<sub>S/D</sub> is due to underlap architecture.

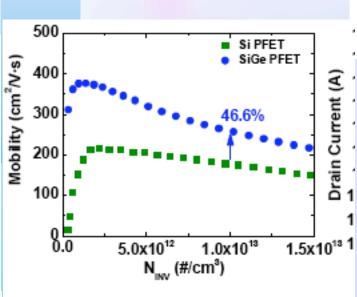

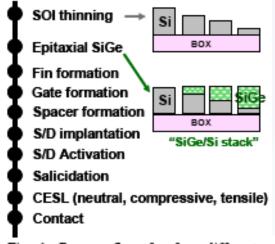

## Strained SiGe and Si FinFETs for High Performance Logic with SiGe/Si stack on SOI, Sematech

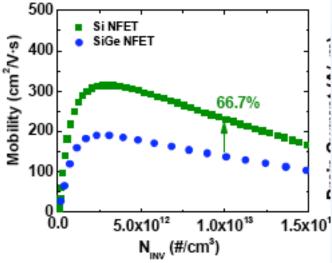

t Fig. 17. SiGe (20nm)/Si (20nm) improved f mobility on p-FinFET by ~46% compared to Si.

Fig. 1. Process flow for four different SiGe/Si stack FinFET

Fig. 19. SiGe (20nm)/Si (20nm) nFinFET shows ~67% degraded mobility relative to Si.

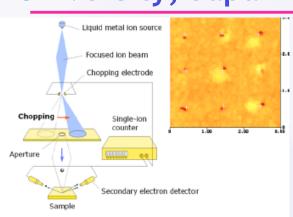

# Reliable Single Atom Doping and Discrete Dopant Effects on Transistor Performance, Shinada, Waseda University, Japan

Fig. 1 Single atom doping method for evaluating the influence of various discrete dopant distribution on device performance. Single ions

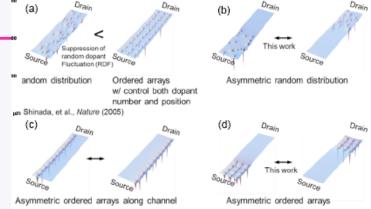

Fig. 2 Systematic studies of discrete dopants on transistor performance. Ordered distribution of dopant atom serves to improve the device performance (a). The influence of asymmetric discrete dopant distributions on the electrical properties has been investigated in this work (b, d). Note that the number of single-ions is controlled by detecting secondary electrons for all devices

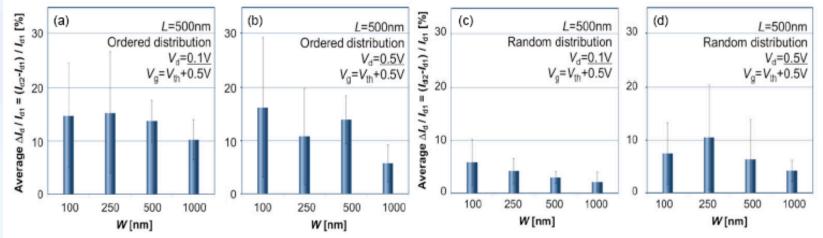

Fig. 10 Bar chart of  $\Delta I_d/I_{d1}$  for devices with ordered (a, b) and random (c, d) distribution of dopants. All devices show the positive variation of  $\Delta I_d$  by interchanging source and drain terminals. The current increase is believed to be attributed to the suppression of injection velocity degradation at the source-side due to the asymmetric discrete dopant distribution.  $\Delta I_d$  tends to increase with increasing in  $V_d$ .