Millios<sup>TM</sup> - millisecond flash anneal for 22nm node

Sing-Pin Tay Mattson Technology, Fremont, CA, USA

Steve McCoy Mattson Technology Canada, Vancouver, BC, Canada

— A Partner You Trust. Performance You Value.

Semicon West TechSITE Junction Technology Group Symposium, July 15, 2010

#### Acknowledgements

- K.L. Lee et al., IBM Research Division, T.J. Watson Research Center, Yorktown Heights, NY.

- J. Chan, G. Stuart & D. Camm, Mattson Technology Canada, Vancouver, BC.

- B. Peuse & P. Timans, *Mattson Technology*, *Fremont*, CA.

## Outline

- Introduction

- Advanced USJ requirements

- The emergence of millisecond anneal

- MSA for Activation with minimal Diffusion

- Adequate defect anneal must be maintained

- Abrupt USJ formation with long ms-flash

- Experimental Results and DiscussionsConclusions

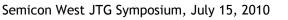

### **Advanced USJ Requirements**

- Minimize Dopant Diffusion

- Maximize electrical activation

- Maintain adequate defect annealing

- Junction leakage is a significant issue for low power CMOS

- Heavy doping in channel/halo contributes to increased junction leakage

- Need to optimize all 3 "dimensions"

- MSA is emerging as a process solution

|                                                                                                                   |              |                      |                      |              |              |              | •            |

|-------------------------------------------------------------------------------------------------------------------|--------------|----------------------|----------------------|--------------|--------------|--------------|--------------|

| Year of Production                                                                                                | 2009         | 2010                 | 2011                 | 2012         | 2013         | 2014         | 2015         |

| MPU Printed Gate Length (nm)                                                                                      | 47           | 41                   | 35                   | 31           | 28           | 25           | 22           |

| MPU Physical Gate Length (nm)                                                                                     | 29           | 27                   | 24                   | 22           | 20           | 18           | 17           |

| Drain extension X <sub>j</sub> (nm) for bulk MPU/ASIC<br>[A]                                                      | 13           | 12                   | 10.5                 | 9.5          | 8.7          | 8            | 7.3          |

| Maximum allowable parasitic series<br>resistance for bulk NMOS MPU/ASIC × width<br>(( $\Omega$ -µm) from PIDS [B] | 170          | 170                  | 160                  | 140          | 130          | 110          | 110          |

| Maximum drain extension sheet resistance for<br>bulk MPU/ASIC (NMOS) (Isq) [B]                                    | 650          | 670                  | 660                  | 680          | 750          | 810          | 900          |

| Contact maximum resistivity for bulk<br>MPU/ASIC (Q-cm²) [I]                                                      | 1.60E-<br>07 | 1.38 <b>E-</b><br>07 | 8.00 <b>E-</b><br>08 | 4.00E-<br>08 | 2.00E-<br>08 | 1.00E-<br>08 | 8.00E-<br>09 |

| <b>ATRS</b>                                                                                                       |              |                      |                      |              |              |              |              |

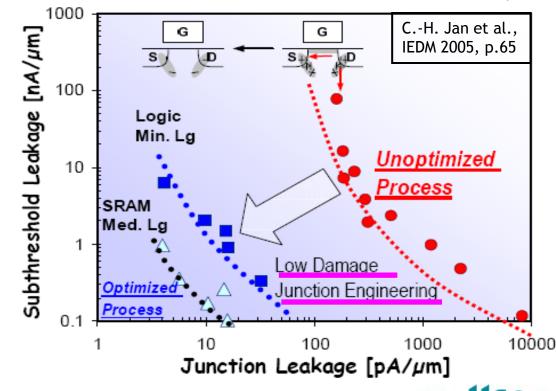

### Millisecond Annealing with Millios<sup>™</sup> fRTP<sup>™</sup>

5

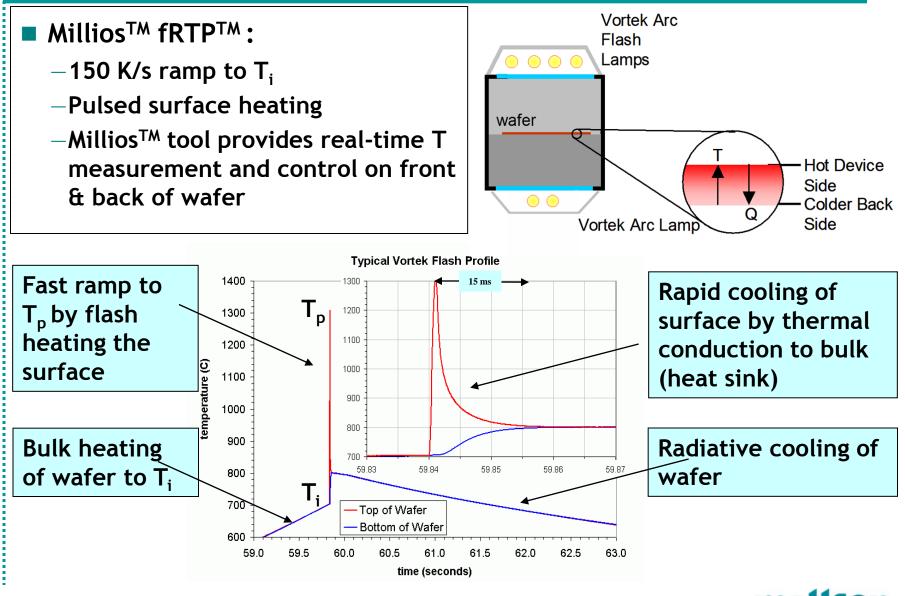

### **Diffusion and Activation with Millisecond Annealing**

Performance You Value.

Semicon West JTG Symposium, July 15, 2010

6

## The Need of a Long ms-Flash Anneal

- For 22 nm technology and beyond where gate pitch is <80nm, a difficult trade-off exists:</p>

- Need to increase SD area for lower contact resistance

- Need for adequate final spacer width to prevent SD encroachment to SDE, which degrades device SCE performance

- This trade-off tends to drive the use of thinner SDE offset spacer and the corresponding reduction of spike RTA temperature for device centering

- Although subsequent diffusionless millisecond anneal can improve the dopant activation, defects anneal remains inadequate with lower spike RTA temperature

- Process approaches with only diffusion-less MSA offer inadequate defect anneal and profile control to fully optimize device performance

- Looking forward into 15nm node a junction depth of 7-10nm will be needed

- A new anneal approach to provide nm-scale junction profile control for device centering, improved defects anneal and dopant activation will be required

- $-\,$  Long pulse seems to be the most promising way to fill the need

- Therefore, we have developed a high temperature (1200-1300°C), long ms-anneal approach (1-2.5 ms) in the Mattson Millios<sup>TM</sup> system

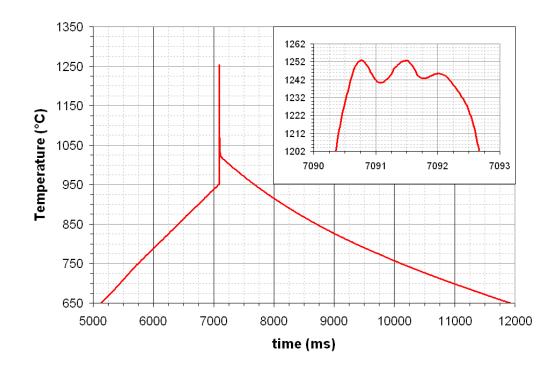

## Real-Time Control in a Long ms-Flash

■ Real time control of lamps in Millios<sup>™</sup> allows for flat top temperate profiles

- Maximizes activation

- Reduces diffusion and deactivation during heating and cooling

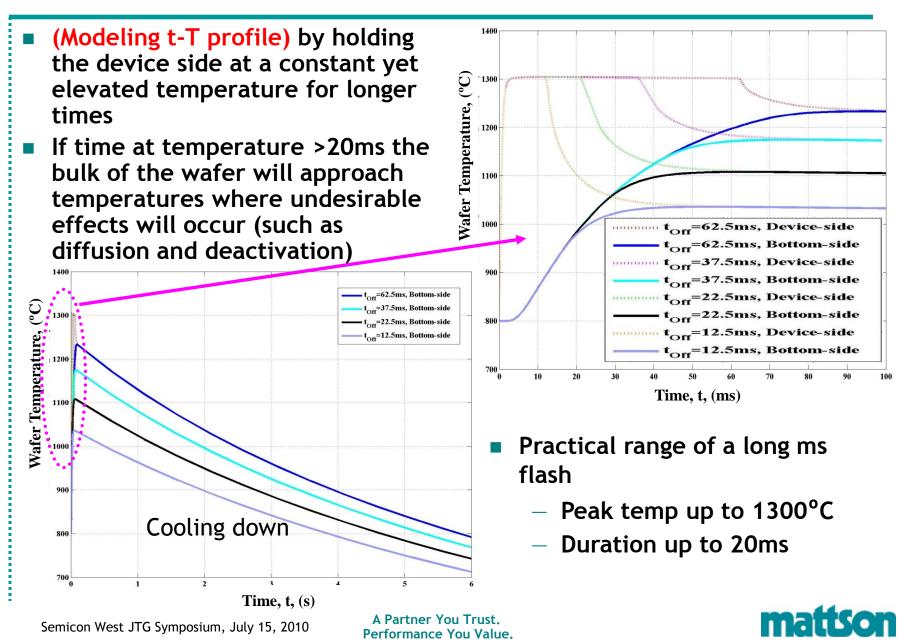

## Practical Range of a Long ms-Flash

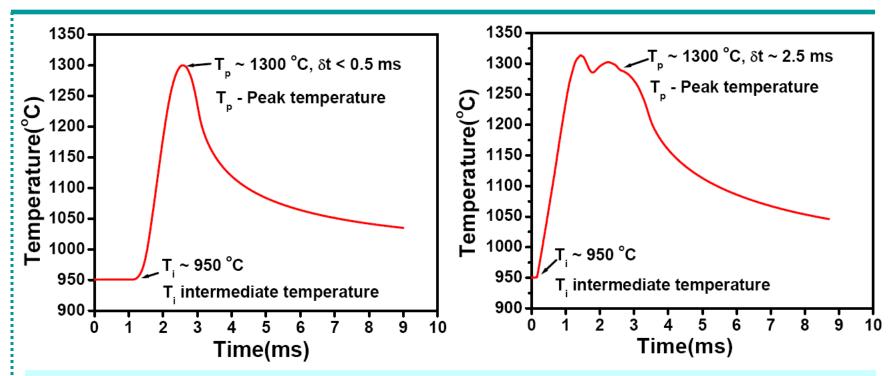

#### Time-Temp. profile: a short ms-flash vs. a long ms-flash

K.L. Lee et al. (IBM) and S. McCoy et al. (Mattson), Int'l Workshop of Junction Technology, May 2010

#### These are t-T profiles of blanket wafers

The surface reflectivity of device wafers changes from 70% to 10% relative to blanket wafers, thus enabling a larger range of (T<sub>p</sub> -T<sub>i</sub>) in as much as 550°C for long ms-anneal of device wafers

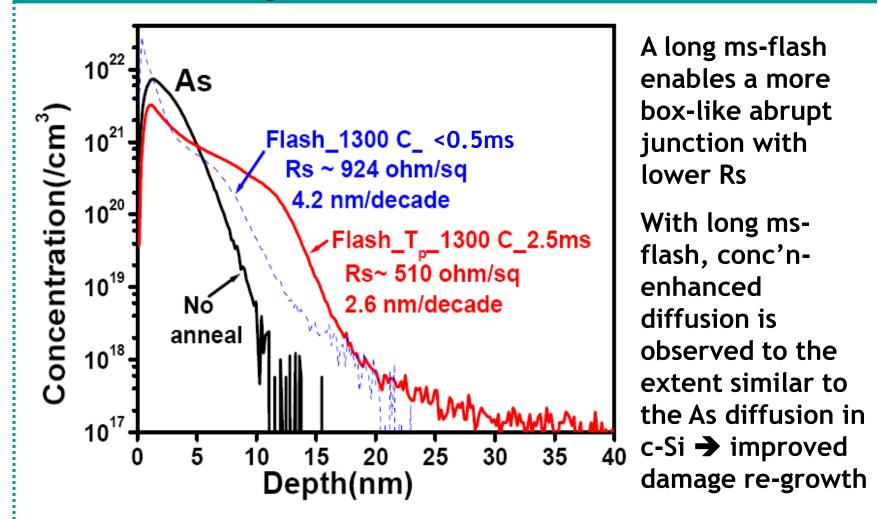

# Comparison of As junction formation with a short and long-ms flash

K.L. Lee et al. (IBM) and S. McCoy et al. (MTSN), IWJT, May 2010

Semicon West JTG Symposium, July 15, 2010

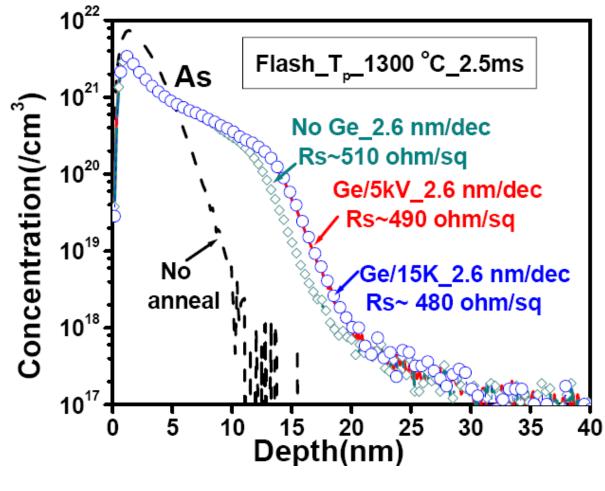

# Comparison of As junction formation with different Ge PAI (0, 5kV, 15kV) and long-ms Flash

Dhm/sq And regrowth during long msflash

> →Final As junction profile dominated by As diffusion in c-Si

Again, long ms-

flash enables a

box-like abrupt

similar Rs indep.

dissolution of Ge

junction with

of Ge PAI

→ Rapid

K.L. Lee et al. (IBM) and S. McCoy et al. (MTSN), IWJT, May 2010

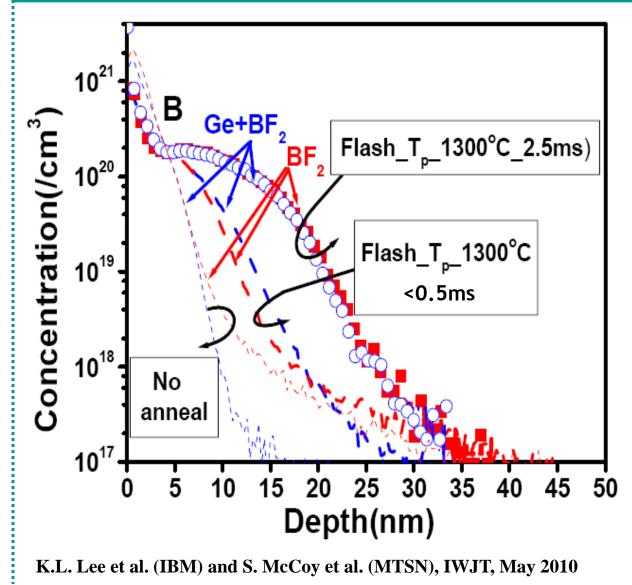

# Comparison of B junction formation with short and long ms-flash anneal

A Partner You Trust. Performance You Value. Again, long msflash enables a more box-like abrupt junction

For short ms-flash the EOR of Ge PAI provides excess interstitials to enhance diffusion

For long ms-flash final B junction is same with or w/o Ge PAI → Rapid dissolution of Ge PAI EOR damages and regrowth

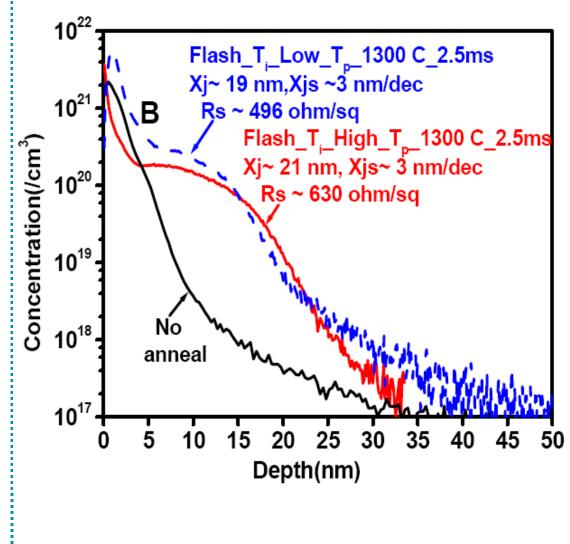

# Comparison of B junctions with different energy, doses and flash Ti temperatures

Using higher BF<sub>2</sub> I/I energy & dose, and an absorber on blanket I/I wafer to simulate device wafer reflectivity, long msflash with lower T<sub>i</sub> at T<sub>p</sub> of 1300°C was enabled and compared to one with higher T<sub>i</sub>

Lower T<sub>i</sub> case yields shallower Xj (19 vs 21 nm), lower Rs (496 vs 630 ohm/sq) and similar junction abruptness Of ~3nm/dec

K.L. Lee et al. (IBM) and S. McCoy et al. (MTSN), IWJT, May 2010

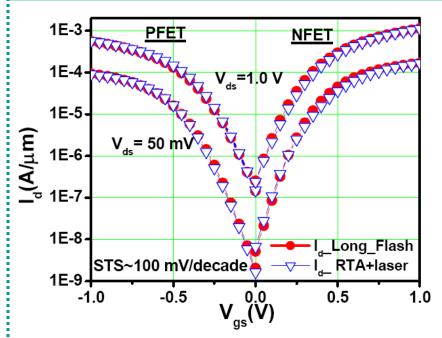

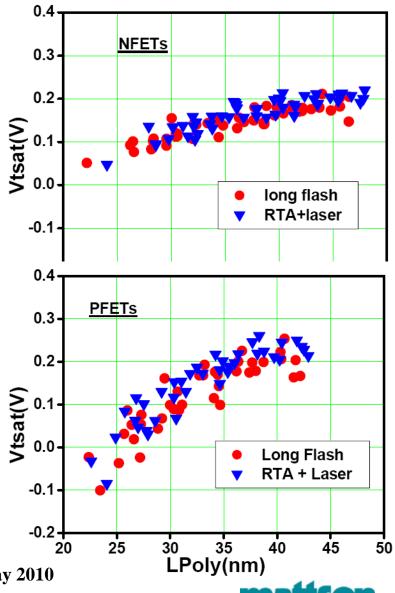

## $\rm I_d$ vs $\rm V_{gs}$ of PFETs and NFETs at Vds of 50 mV & 1V

Long ms-flash implemented in a SOI process with a Poly/SiON gate stack was compared with a "combo process" of Spike-RTA + Laser Anneal

High perf. P- & N-FETs with matching I<sub>d</sub>-V<sub>gs</sub> and similar V<sub>t(sat)</sub> roll-off have been obtained for both annealing schemes

K.L. Lee et al. (IBM) and S. McCoy et al. (MTSN), IWJT, May 2010

A Partner You Trust.

Performance You Value.

Semicon West JTG Symposium, July 15, 2010

### Conclusions

- High temp long ms-flash anneal has been employed to improve defect annealing while maximizing dopant activation with minimal diffusion

- Mattson Millios<sup>TM</sup>, with the long ms-flash anneal (2.5ms) capability, has been demonstrated to better activate dopants in sub-20 nm N+ & P+ SD with more box-like abrupt junctions compared to shorter ms-flash anneal (<0.5ms)</p>

- By means of this, high performance SOI CMOS has been achieved with single long ms-flash and matches well with CMOS created with a "combo" of spike RTA + laser anneal

- Mattson Millios<sup>TM</sup> capabilities are being developed to enable a long ms-flash anneal, up to a practical limit of 20ms with peak temp of 1300°C

- The Millios<sup>™</sup> is capable of measuring & controlling both the top & bottom side temp in real time over a wide range of temperature, extending down to 250°C & up to 1400°C