# **Advanced Anneal Solutions for Silicides**

Shankar Muthukrishnan

**RTP Anneals GPM**

July 15th 2010

## **Challenges Scaling Nickel Silicide Contacts**

- Diffusion control for thinner layer formation

- Silicide-Silicon interface morphology

- Avoiding yield limiting piping defects, especially with proximity to SDE, channel

- Sensitivity to agglomeration

#### Improved silicide contact is key to scaling

### **Integration Alternatives to Suppress NiSi Piping**

- Pre amorphous implant (PAI)

- Pre clean using "flourine" dry etching

- Co implant dopant in substrate (F, C)

- Nickel alloy (Pt)

- Modifying anneals

## **Nickel-Silicide Process Steps**

#### NiPt Salicide Flow:

|                                                                 | Traditional anneals | Advanced alternative |

|-----------------------------------------------------------------|---------------------|----------------------|

| pre clean (native oxide removal)                                |                     |                      |

| metal deposition (NiPt/TiN)                                     |                     |                      |

| RTP-1 anneal : Ni diffusion into Si creating Ni <sub>2</sub> Si | 280-300°C Soak      | 200-250°C Soak       |

| non-reacted (NiPt) metal removal by selective etching           |                     |                      |

| RTP-2 anneal : transformation into low resistance NiSi          | 400-500°C Soak      | ~850°C millisecond   |

|                                                                 |                     |                      |

## **Soak to Millisecond Transition for Silicides**

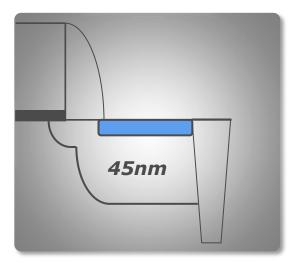

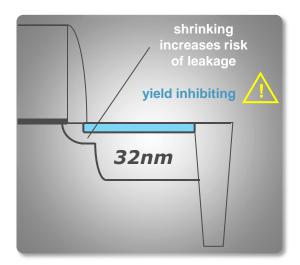

|                              | Logic (65nm) | Logic (45nm)           | Logic (32nm)  |

|------------------------------|--------------|------------------------|---------------|

| Ni Silicidation / Diffusion  | Soak         | Low temp Soak          | Low temp Soak |

| NiSi Phase<br>Transformation | Soak         | Soak or<br>Millisecond | Millisecond   |

#### Driven by

- Enabling thinner silicides without comprising conductivity or yield

### Millisecond Provides

- Improved Yield performance

- Improved Junction Leakage performance

- Fewer leakage-inducing defects through steep temperature profile

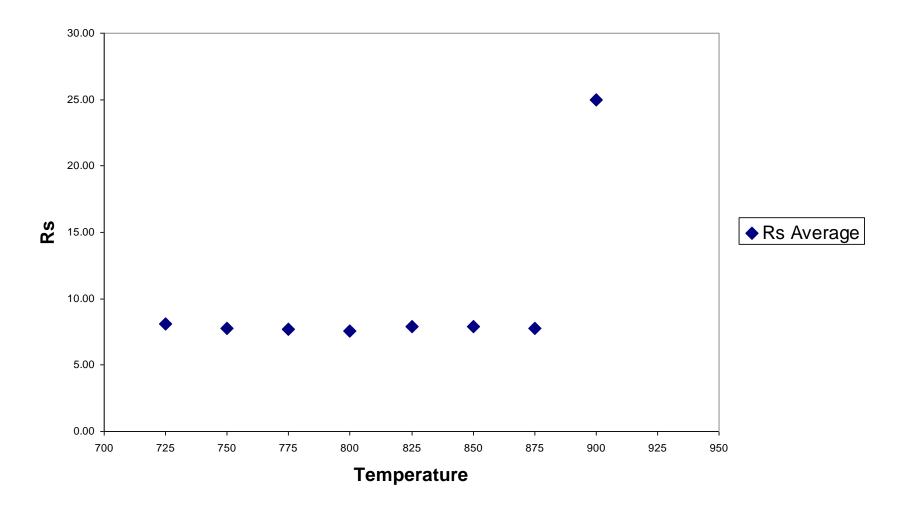

### **Nickel Silicidation Transformation Curve**

Large process window available for RTA 2

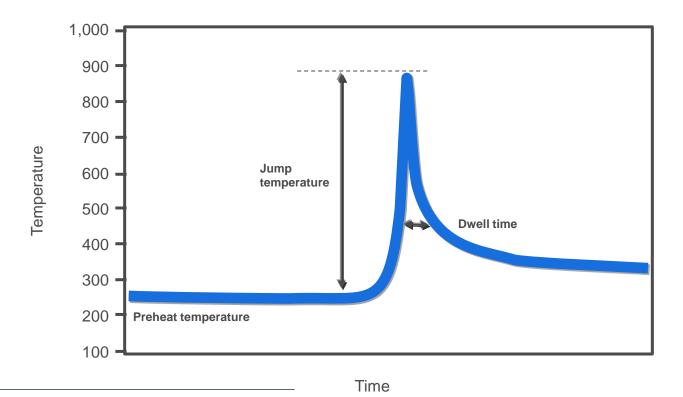

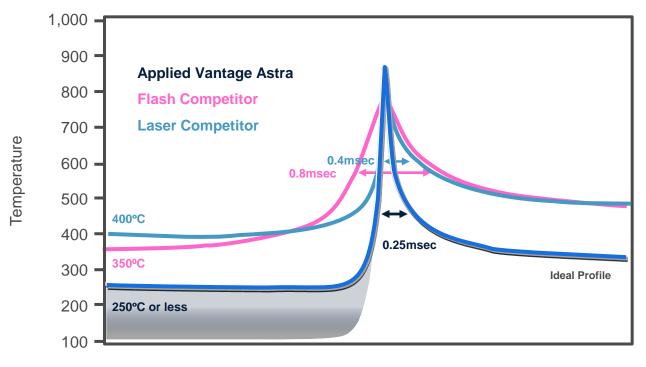

## **The Ideal Time-Temperature Profile for NiSi**

#### Key parameters to consider

Preheat : Must be low enough to avoid uncontrolled diffusion

Jump temp : Must be high enough to enable optimal activation w/o wafer breakage or agglomeration

Dwell time : Must be short to avoid wafer bow and breakage

Above profile is key to enabling optimal nickel silicide

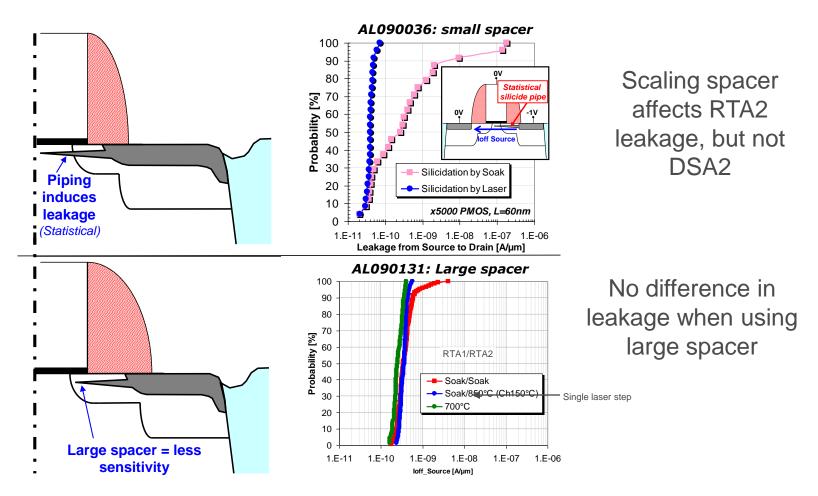

### Yield Results and Scaling Impact for NiSi Process

Data source : IMEC IEDM 2009

### **Results: NiSi Morphology Improvement**

Source: IEEE - RTP2009 Conference, Advances on 32nm NiPt Salicide Process, Dr. Chen et al. Co-published by UMC / Applied Materials

Process B (lower RTP-1 Soak) roughness reduced vs process A (baseline) Process C (lower RTP-1 Soak + DSA RTP-2) achieves lowest roughness

## **Results: NiSi Piping Defects Reduction**

**Piping Defects Count TEM Top View** 100 80 Normalized Defects (%) 60% 60 Α 40 30% 20 B С 0 T1 Soak T1-40°C Soak T1-40°C Soak **RTP-1** anneal: **RTP-2** anneal: T2 Soak T2 Soak T2 + 400°C DSA

Based on e-beam Bright Voltage Contrast (BVC) measurement count on a pattern wafer, post CMP

Source: IEEE - RTP2009 Conference, Advances on 32nm NiPt Salicide Process, Dr. Chen et al. Co-published by UMC / Applied Materials

Process B (lower RTP-1 Soak) achieves lower defect count than baseline Process C (lower RTP-1 Soak + RTP-2 DSA) achieves lowest piping defect count

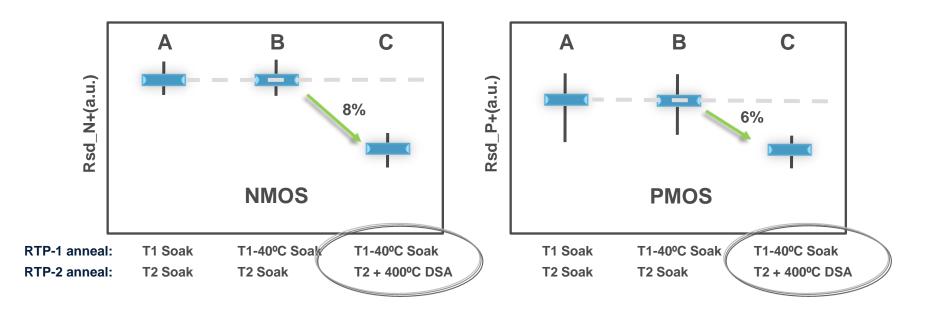

### **Results: Electrical Performance – R<sub>S/D</sub>**

Source: IEEE - RTP2009 Conference, *Advances on 32nm NiPt Salicide Process*, Dr. Chen et al. Co-published by UMC / Applied Materials

The series S/D Rs (Rsd) decreased using DSA

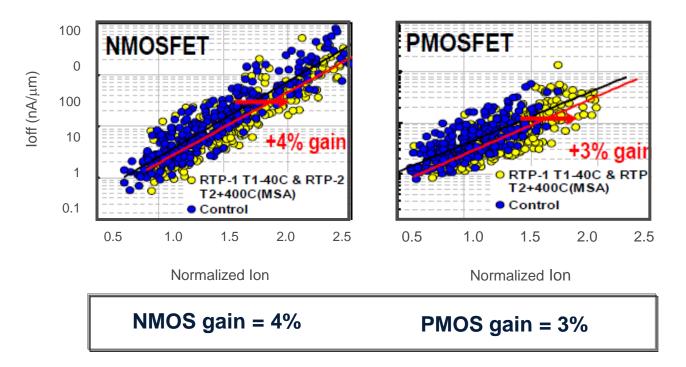

### **Results: Electrical Performance – Ion/Ioff**

RTP-1: Soak @ T1-40°C RTP-2: Millisecond (T2+400°C)

Source: IEEE - RTP2009 Conference, *Advances on 32nm NiPt Salicide Process*, Dr. Chen et al. Co-published by UMC / Applied Materials

Drive current gain achieved by enhancing nickel silicide contact using millisecond annealing with low temperature RTP-1 Soak

## **The Ideal Time-Temperature Profile for NiSi**

### Key parameters to consider

Preheat : Must be low enough to avoid uncontrolled diffusion

Jump temp : Must be high enough to enable optimal activation w/o wafer breakage or agglomeration

Dwell time : Must be short to avoid wafer bow and breakage

Time

### Delivered by Applied Materials' Vantage Astra system

## Applied Vantage<sup>®</sup> Astra<sup>™</sup> DSA System

### Uniquely powerful silicidation

- Up to 5% greater device speed

- Higher yields enabled by up to 15x lower leakage

- Less wafer stress

#### Versatile dynamic millisecond anneal

- Broad range of processing conditions

- Ambient control

- Extendible to high-k/metal gate applications

### Compact, reliable, cost-effective

- Simple, compact and smart chamber design

- Solid-state laser with prolonged lifetime

- > 40 WPH per two- chamber system

- Compatible with an RTP chamber on same system as hybrid

### FAST. SMART. RELIABLE. Simply Better Anneal

### Vantage Astra DSA System Photos

# Turning innovations into industries.™