# CMOS Leakage Reduction using Laser Spike Annealing

Presented by: Jeff Hebb, Ph.D.

Contributors: David Owen, Yun Wang, Shrinivas Shetty, Van Le, Shaoyin Chen, Andy Hawryluk

Ultratech, Inc.

July 17, 2009

# Outline

- Introduction

- Advantages of high annealing temperatures

- •HK+MG

- Role of stress for advanced CMOS

- •Extendibility to alternate device structures

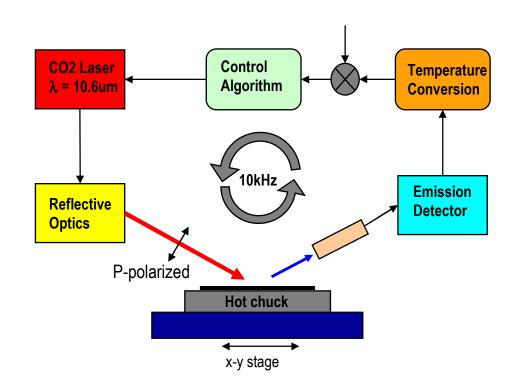

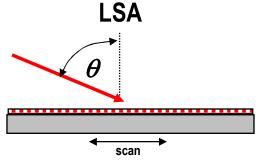

# **LSA System Architecture**

#### LSA Key Attributes

- 1. Within-die uniformity

- Long wavelength,

- p-polarized

- Brewster angle

- 2. Wafer-to-wafer repeatability

- Temperature feedback control

- 3. Low stress

- Flexible dwell time

- Effective stress dissiptaion

System is designed to minimize within-die and within-wafer variations

Ultratech

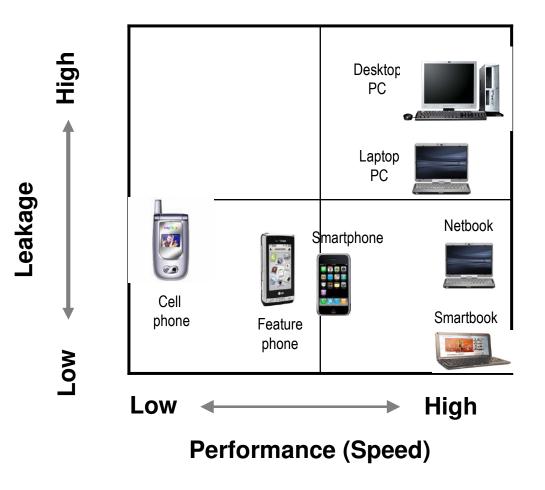

### Leakage and Power Requirements for Advanced Devices

#### **Key Highlights**

- Trends toward multi-media

"connected" devices have

placed unprecedented

demands on simultaneous

power and leakage

- Leakage reduction is critical for:

- Battery life

- Cooling requirements

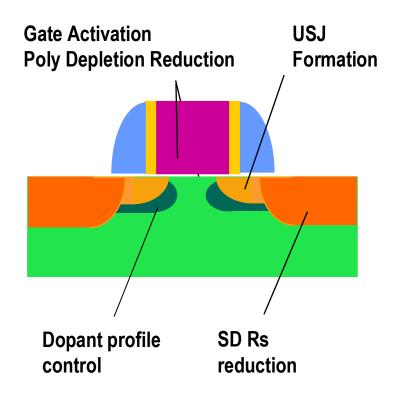

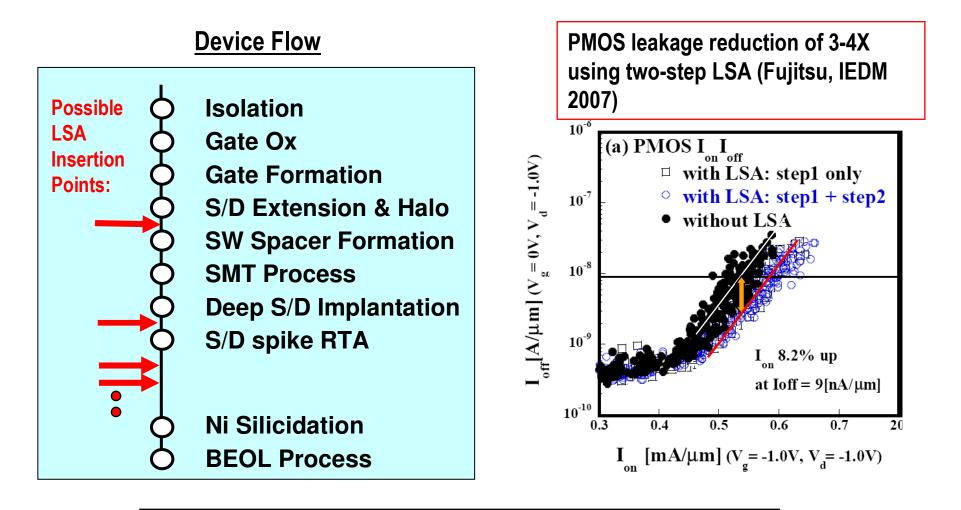

## **Laser Spike Annealing for USJ Formation**

- Thinner Tox\_inv due to reduced poly depletion

- Improved Id due to reduced series resistance

- Reduced SCE due to ultra-shallow junction

- Multiple steps being used to maximize gains from LSA

- Tradeoff's between leakage and speed by reverse oxide scaling, junction re-optimization, etc

### Introduction

### Advantages of high annealing temperatures

- •HK+MG

- Role of stress for advanced CMOS

- •Extendibility to alternate device structures

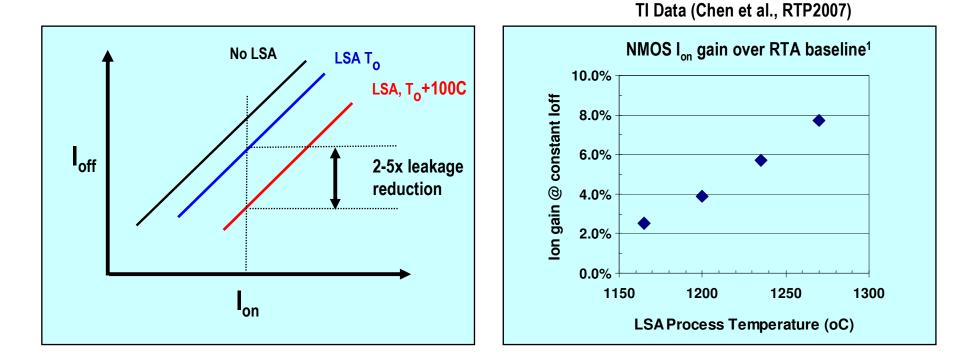

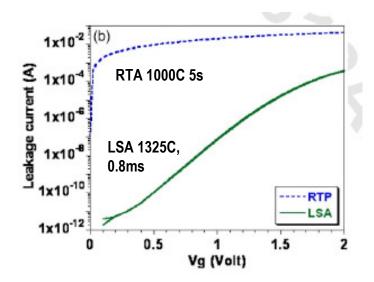

## Higher temperatures of LSA gives lower leakage

Typically, an increase in LSA peak temperature of 100C reduces leakage by 2-5X, depending on device integration (e.g, Adachi et al. Toshiba, IEDM 2005).

## **Multiple LSA steps for leakage reduction**

Multiple LSA steps is mainstream for advanced nodes

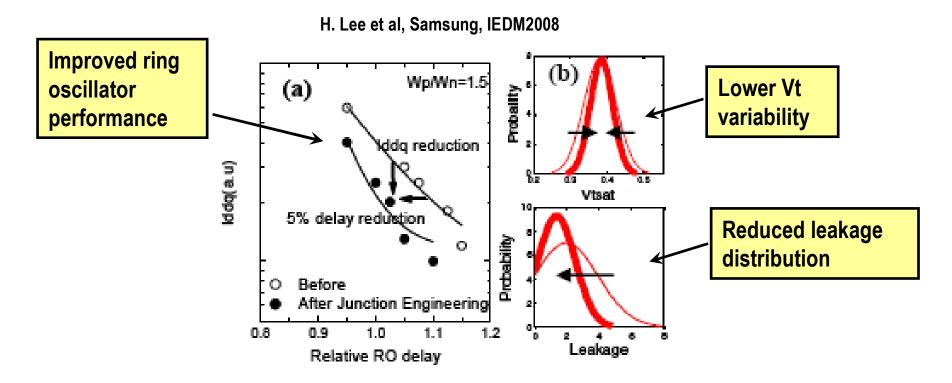

## Vt Variability & Leakage Reduction For Low Power Application (Samsung Results)

#### LSA/Implant optimization gives leakage reduction and improved uniformity

**AVS West Coast Junction Technology Group Meeting**

- Introduction

- •Advantages of high annealing temperatures

### •HK+MG

- Role of stress for advanced CMOS

- •Extendibility to alternate device structures

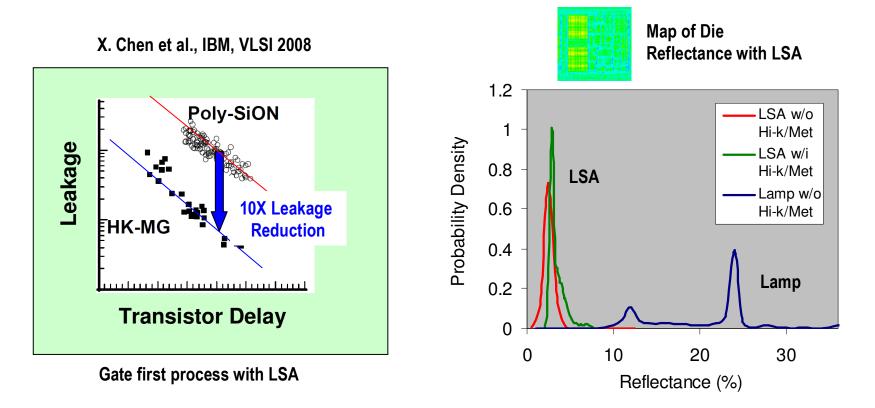

## LSA Compatibility with High K + Metal Gate

LSA demonstrated to be compatible with "gate first" HK+MG integration

Pattern suppression still effective for HK+MG due to small thickness of metal gate

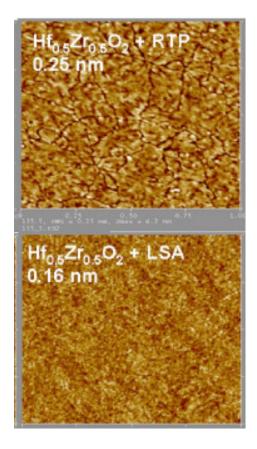

## High-k Morphology & Leakage Improvement

(a) AFM morphology

(b) Leakage characteristics

\*source: D.H. Triyoso, to be published in APL

**AVS West Coast Junction Technology Group Meeting**

- Introduction

- •Advantages of high annealing temperatures

- •HK+MG

- Role of stress for advanced CMOS

- •Extendibility to alternate device structures

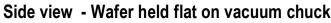

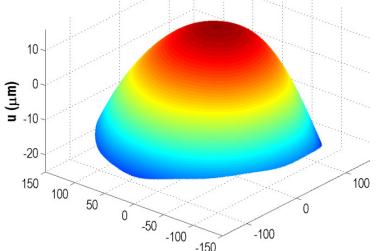

# Wafer Stress in LSA

Top view: Simulated stress during LSA. Less than 5% of the wafer area is stressed

#### **Temperature gradients**

Minimal pattern effects give uniform stress

#### **Stress dissipation**

- Stress is localized minimizes thermal shock.

- Stress is dissipated by rest of the wafer and to wafer chuck

#### **Dwell time**

Dwell time flexibility allows low wafer warpage for critical process steps

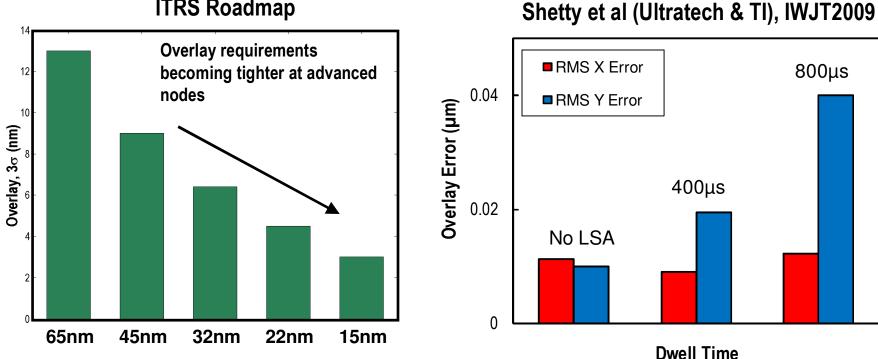

## **Relationship Between Stress & Overlay**

**ITRS Roadmap**

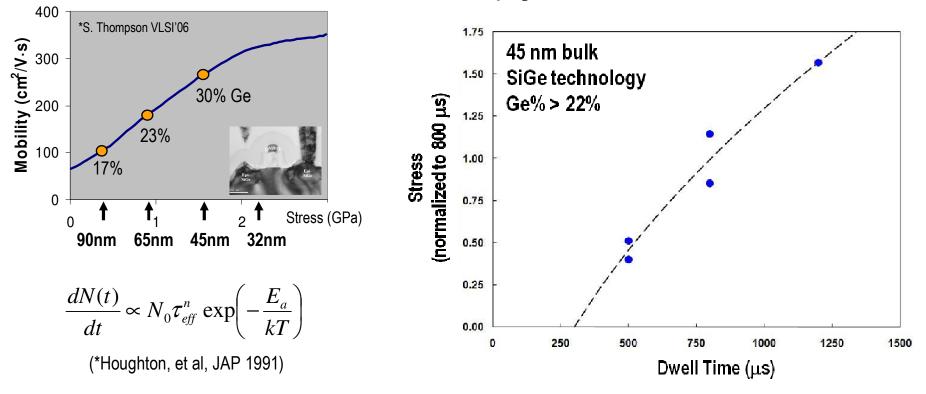

- LSA dwell time flexibility critical for compatibility with e-SiGe at sub-65nm

- Same principles apply for Si:C for sub-32nm

Julv 16. 2009

## Low Dwell Time for Overlay Improvement

Warpage & stress are reduced at low dwell times

- Dislocation formation scales exponentially with T and t<sup>1/2</sup>, so reducing time is beneficial for reducing overlay errors

- Dislocation formation will become more severe as Ge concentration is increased

## **Overview of Coherent Gradient Sensing System**

- Measurement technology: Lateral shearing interferometer

- >700,000 points (310 μm per pixel)

- Rapid image capture, no scanning

- Analysis and algorithms

- Full analysis in less than 2 minutes

- Full wafer stress variations can be correlated to die-level issues

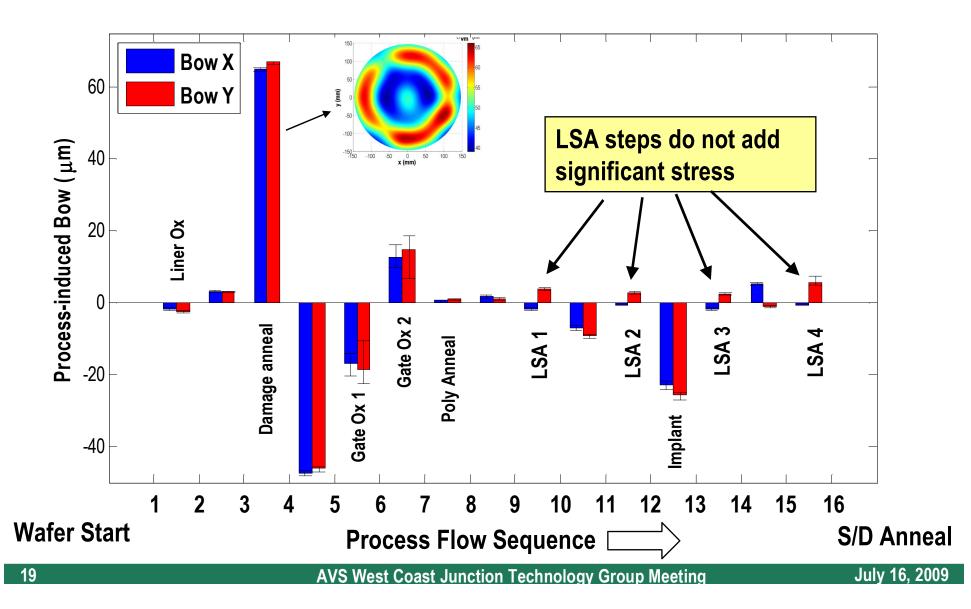

## **Stress Fingerprinting and Correlation to Leakage**

- Coherent Gradient Sensing (CGS) system used to measure wafer level stress at 16 process points in a 65nm DSP process flow

- Measurement points span ~120 process steps from wafer start through source-drain anneal

- Within-wafer and wafer-to-wafer stress variations were characterized for each process or set of processes

- Correlations between electrical parameters & stress were explored

- Parameters: PMOS & NMOS drive current, leakage current, drain current and threshold voltage

- Data used to identify which process steps and stress metrics to which electrical performance is most sensitive

## Ultratech Stress fingerprinting results

Fingerprinting: Measuring stress & deformation across multiple steps in line

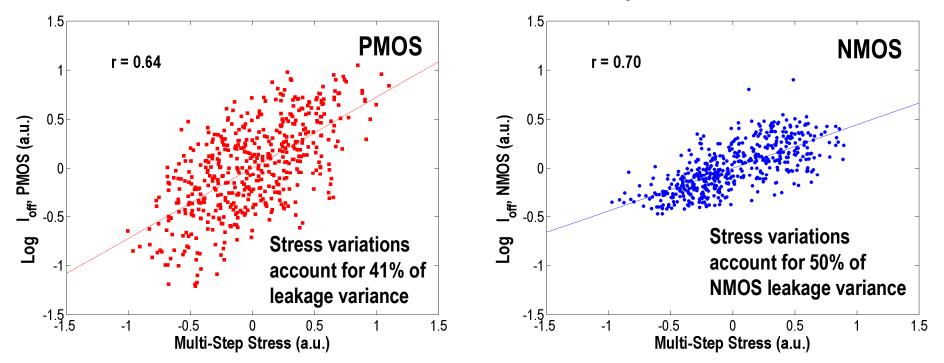

## **Correlation of stress to leakage current**

All Points, All Wafers, All Steps

- There is a significant correlation between wafer level stress and leakage

- Most of the leakage variation is due to within-wafer stress variations

- Low stress of LSA does not contribute significantly to stress correlated leakage

# **PMOS I<sub>OFF</sub>: Within Wafer Variation**

(Multiple Steps)

- Data for each die location represents the average of all 24 wafers in lot lacksquare

- Within wafer stress variations correspond to leakage current variations

- Introduction

- •Advantages of high annealing temperatures

- •HK+MG

- Role of stress for advanced CMOS

- •Extendibility to alternate device structures

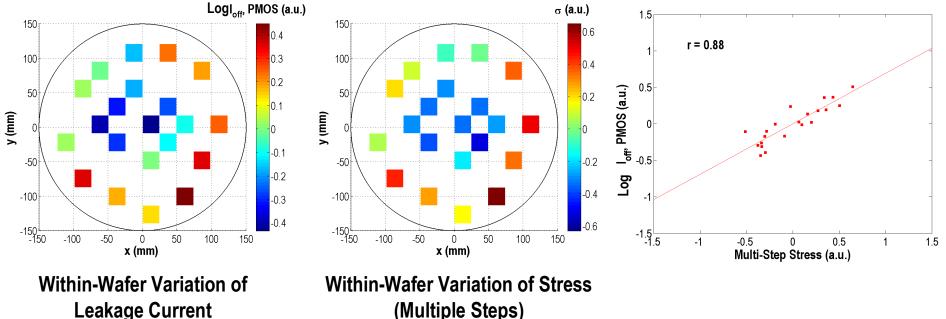

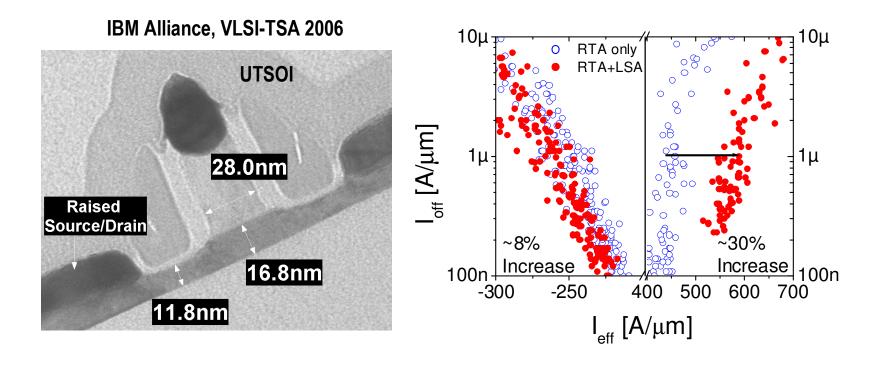

# **LSA Application To UTSOI**

LSA gives 30% enhancement in leff & 10% improvement in RO speed for UTSOI

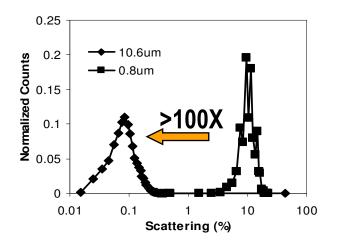

# **Compatibility With Non-Planar Structures**

**Total Integrated Scattering:**

$$TIS = \frac{P_s}{RP_i} \approx \left(\frac{4\pi\sigma}{\lambda}\right)^2$$

- Shadowing effects?

- Thin Si fin is transparent to CO2 wavelength, no shadowing effects

- Scattering effects?

- Height is still << 10.6um, so scattering is minimal for LSA

Long wavelength reduces total amount of scattering

$<sup>\</sup>sigma$  is rms surface roughness

## Summary

- Market trends create stringent requirements for simultaneous high performance and low leakage for advanced CMOS

- LSA tool architecture has inherent advantages for achieving high anneal temperatures, which can be used to reduce leakage

- LSA is compatible with HK+MG because pattern suppression extends to thin metal layers

- LSA has inherent advantages for low stress which make it compatible with strain engineering techniques, and may reduce leakage correlated with wafer-level stress

- LSA is compatible with transistor architectures that may be used at 22nm