External Use

# Paradigm Shifts in CMP

#### State of CMP

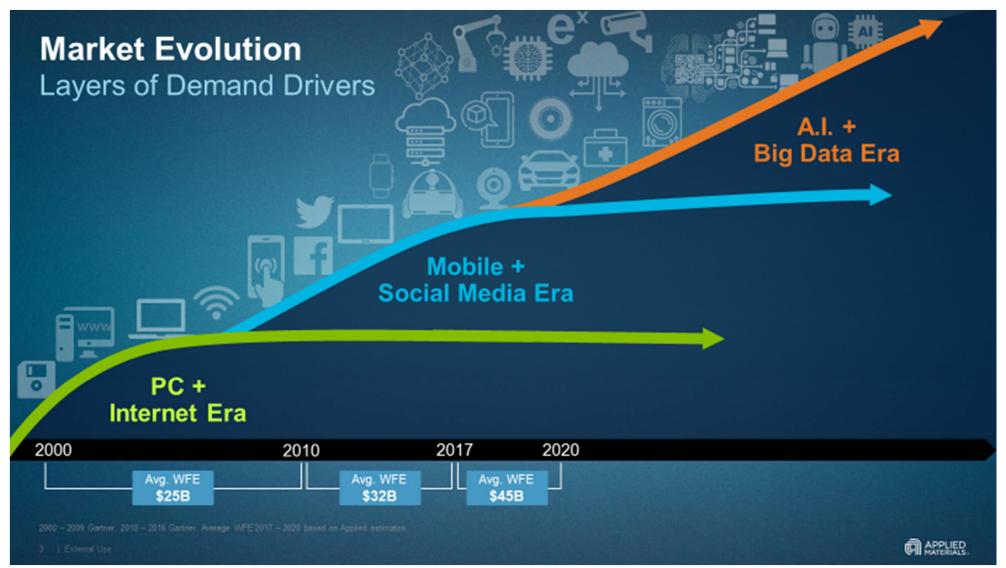

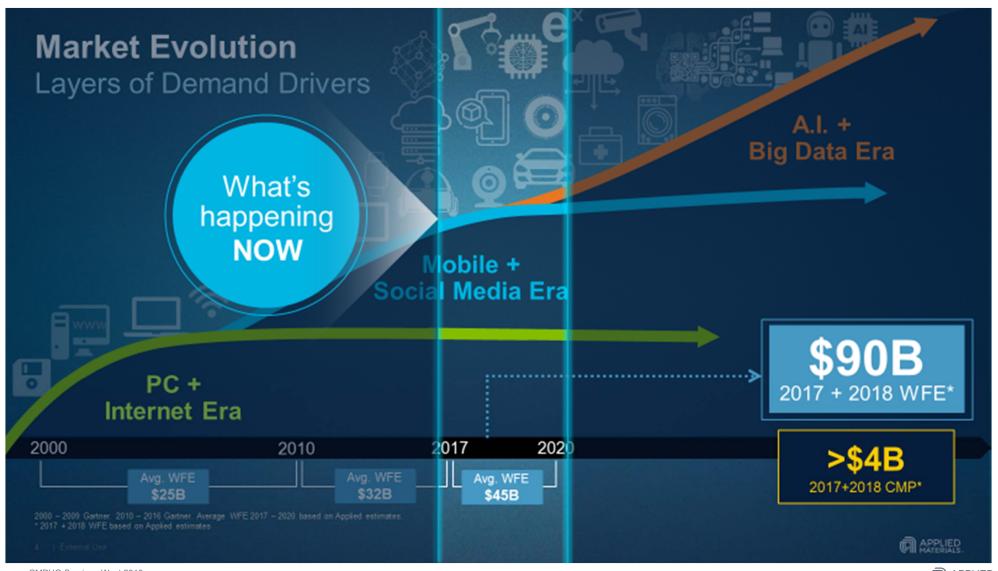

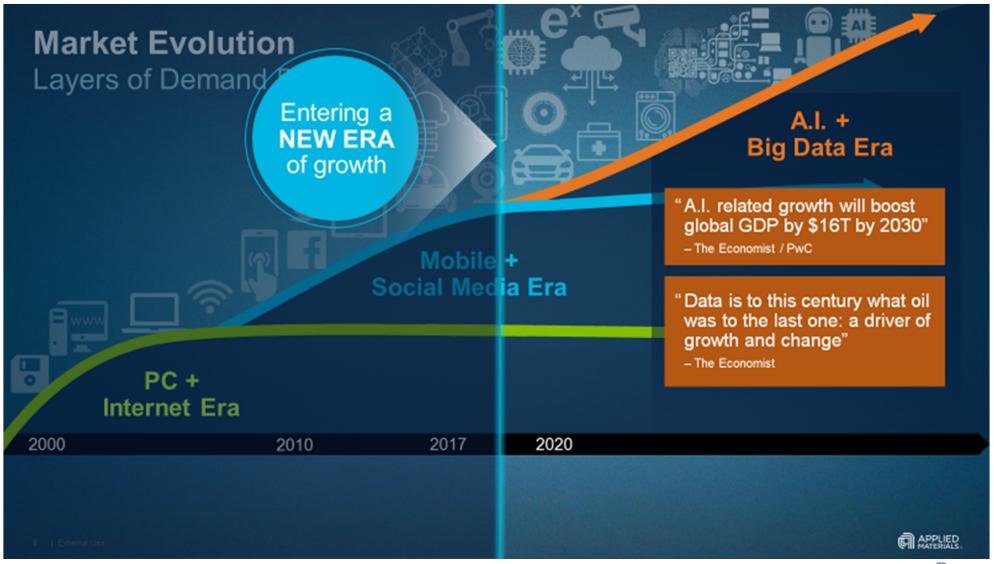

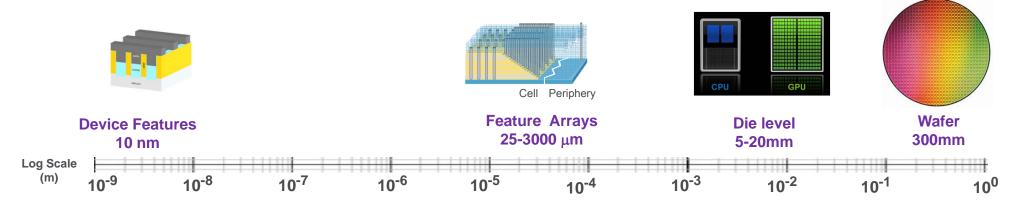

Market Inflections are driving CMP Growth and Complexity

# Paradigm Shifts in CMP

Strategies to address CMP Complexity

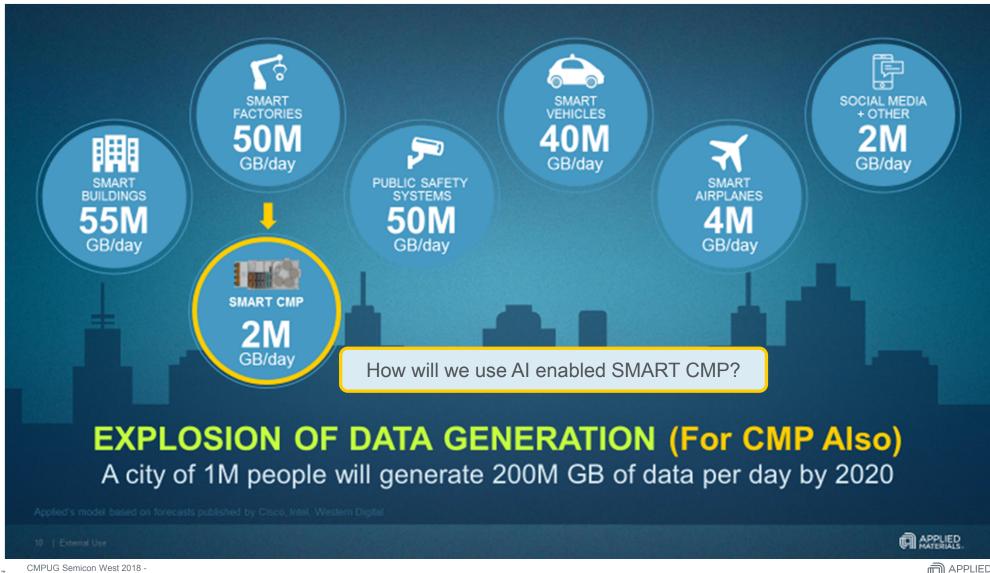

#### **SMART CMP**

Tailored CMP Pads

CMPUG Semicon West 2018 -External Use

#### **CMP Enabled Inflections**

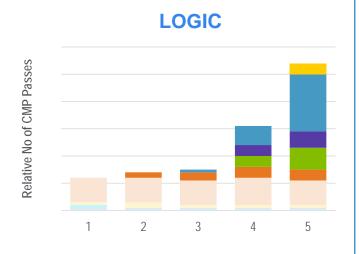

- 3D Transistor: FinFET

- Co contact & local interconnect

- 3D Multi Patterning

- ▶ SA Gate Contact

- Large Die Form Factors

- ▶ GPU

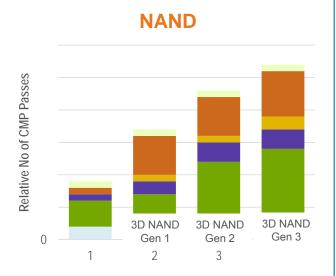

- 3D NAND

- ▶ More W & oxide CMP

- CMOS Under Array

- Stacked Cells

- Multi-Material Polish

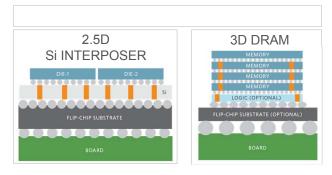

#### **ADVANCED PACKAGING**

- Wafer Level Packaging

- Image Sensors

- ► Redistribution Layer (RDL)

- ► Through Silicon Via (TSV)

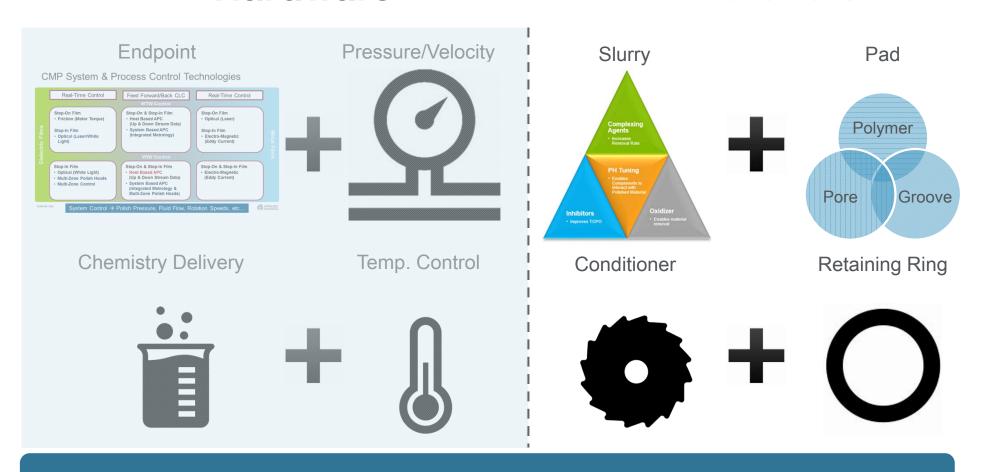

### **Hardware**

#### **Materials**

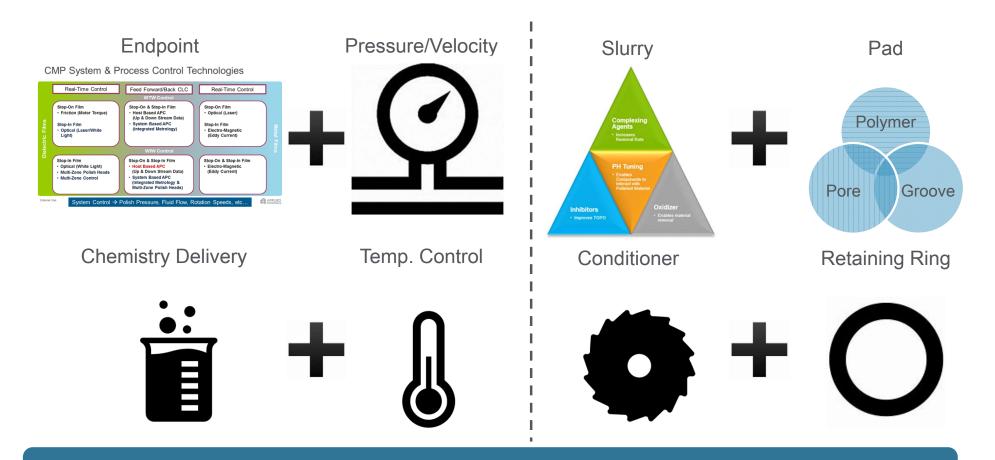

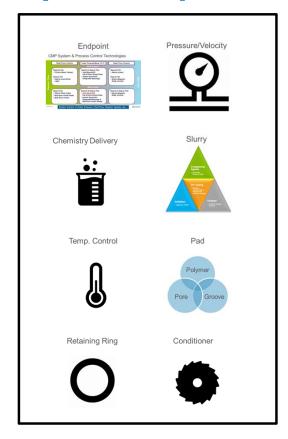

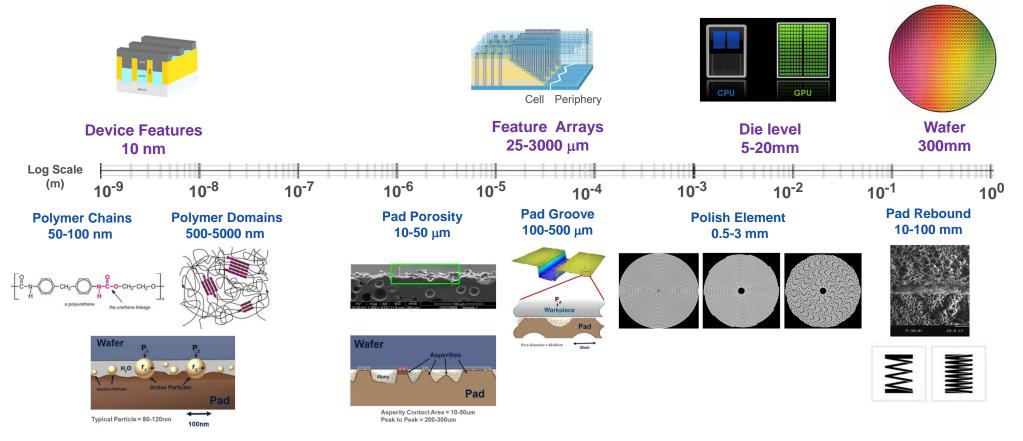

CMP Input Parameters.

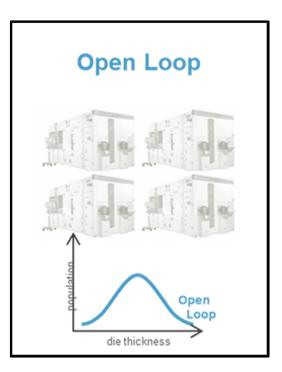

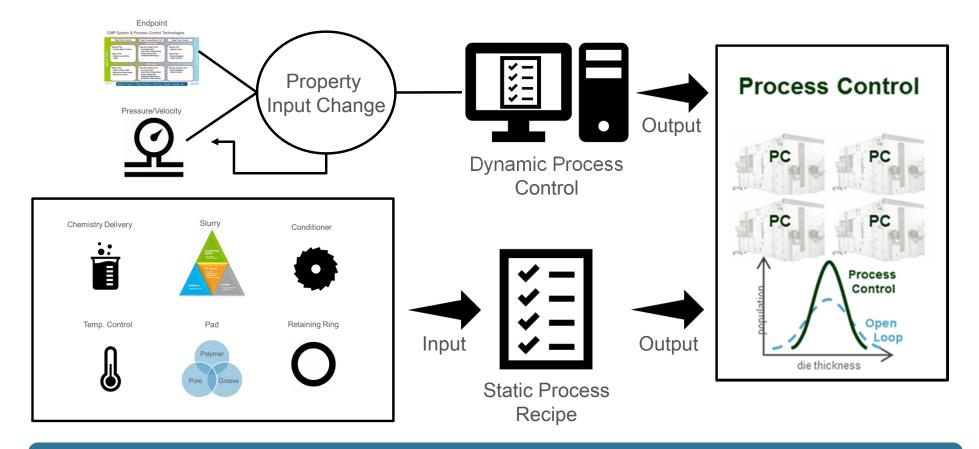

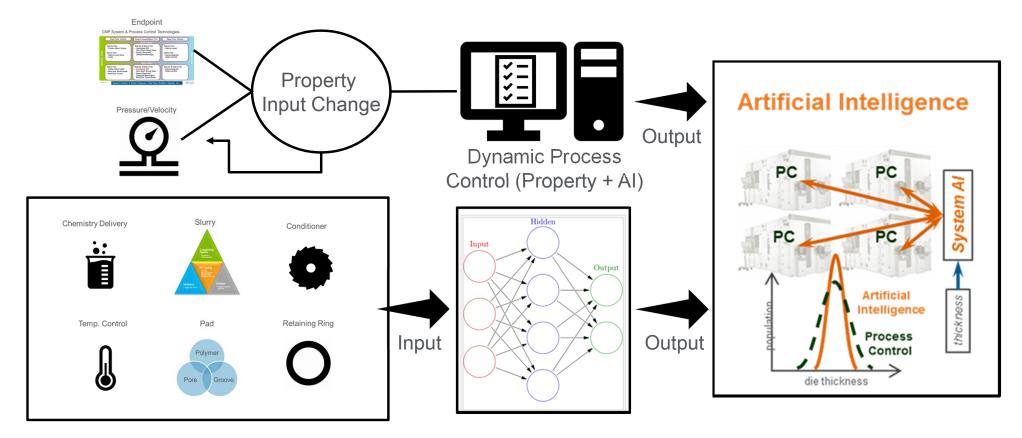

# **Open Loop CMP**

Stability achieved through reduced Input Parameter variability.

#### **Process Controlled CMP**

Performance improved through Dynamic Process Control of Input Parameters.

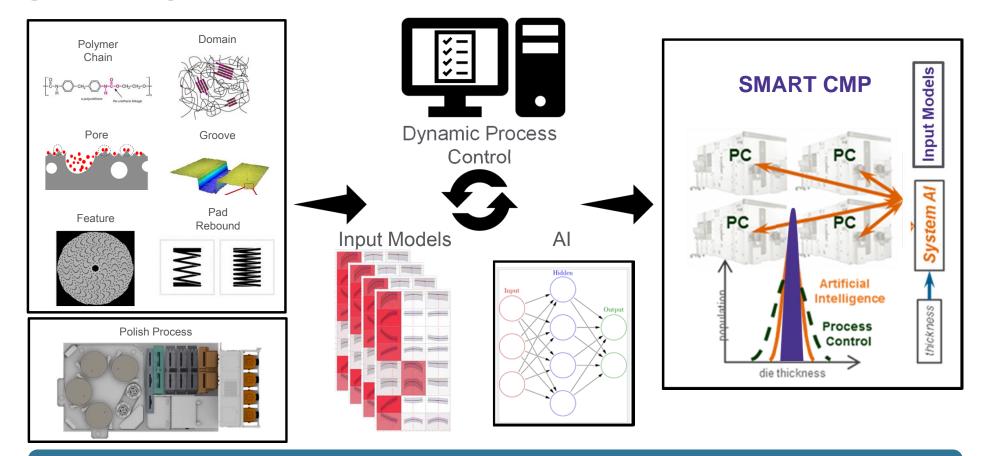

## **Al Augmented Process Controlled CMP**

Al has the promise of optimizing output through the interpolation of multiple Input Parameters.

# Warning with regards to Al Processing

Output success is a function of algorithm training.

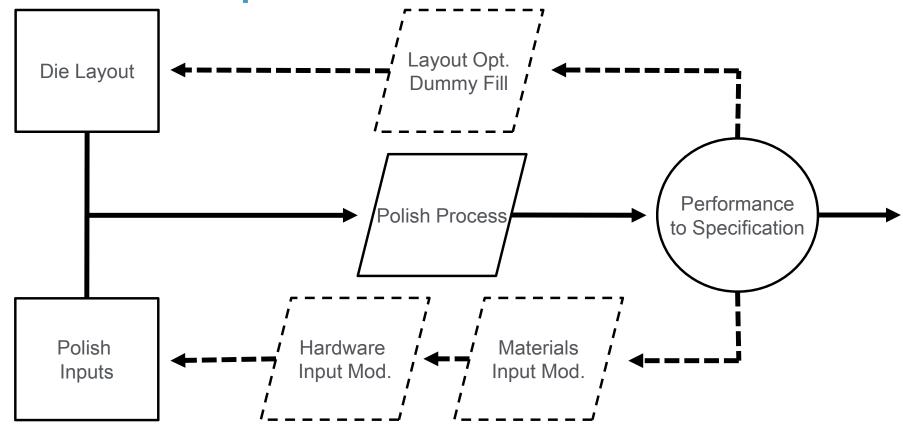

# **CMP Process Optimization**

CMP Polish process versatility continues to enable new integration schemes.

### **Hardware**

### **Materials**

APPLIED MATERIALS

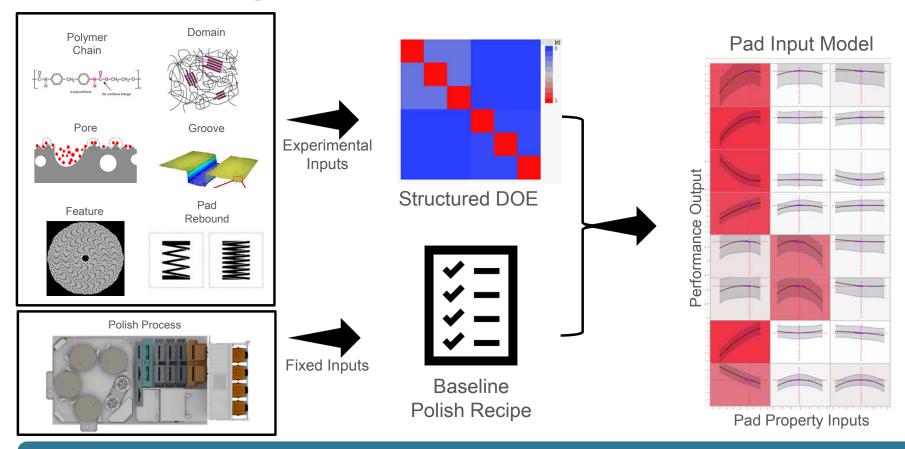

Each Process Input has a Structure/Property Model

# **CMP Pad Structure/Property Input Parameters**

# **CMP Pad Structure/Property Input Parameters**

Structure/Property relationships can be deployed to design locally optimized CMP pads.

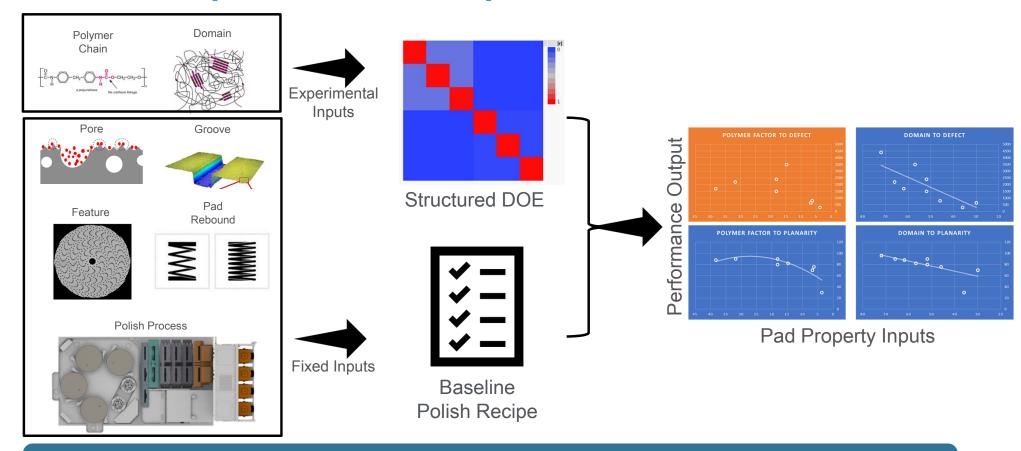

# **CMP Pad Input Parameter Optimization**

Inputs validated against Outputs. Results are developed into Pad Structure/Property Algorithms.

# **CMP Pad Design Optimization**

Rigorous Modeling efforts allow for targeted optimization of CMP Inputs and improvement to Die level Performance Outputs.

#### **SMART CMP**

SMART CMP: Input Parameter Model optimized AI deployed using Dynamic Process Control.