**Electronic Materials**

## **State of CMP Materials**

Marty W. DeGroot July 12, 2017

Dow.com

## The Changing Landscape of CMP: Trends and Challenges for Advanced Devices

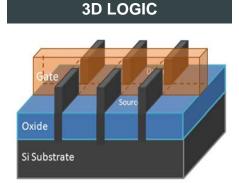

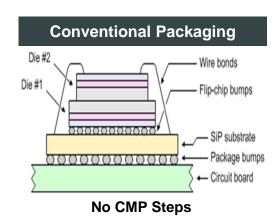

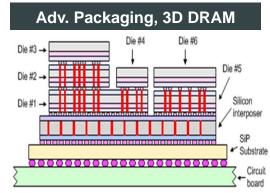

#### More CMP

Advanced device structures leading to increase in the need for CMP

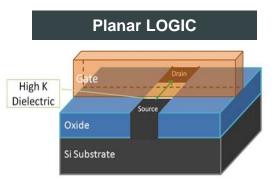

#### Wafer-scale control in FEOL for FinFET devices

- Narrow window of operation: tighter lot-to-lot and with-in lot variation

- Stringent thickness control requirements

- Edge profile control and consistency is critical

#### **Reduced topography and defect tolerance**

- Challenging selectivity requirements

- Low dishing, high PE is increasingly important

- Incoming topography < typical CMP capability</p>

- More CMP near the transistor dishing and defects!

- Emphasis on reduction of micro-scratch count and <u>depth</u>

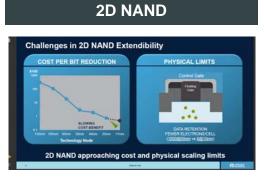

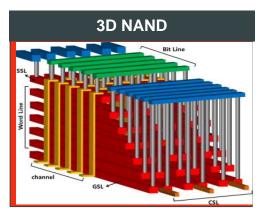

#### **3D stack designs**

- High removal rate for microns thick oxide films

- High planarization and low dishing across mm features

**Dow** Electronic Materials

#### Changes in CMP Scope: Advanced Devices Drive More CMP

Average 9 CMP Steps

Average 19 CMP Steps

Average 1-3 FEOL CMP Steps 2-3 MOL CMP Steps 7-9 Metal BEOL CMP Steps

Average 9-11 FEOL CMP Steps 5-7 MOL CMP Steps 10-13 Metal BEOL CMP Steps

Adv. Packaging, 3D DRAM: 2-4 CMP Steps/Layer

## Shift in CMP Scope: Layer Augmentation in Advanced Devices

|                 |          |        |              | Advance     | ed loaic    |             |                             |               |   |                 |        | Adv       | anced FI  | OSOI     |           |

|-----------------|----------|--------|--------------|-------------|-------------|-------------|-----------------------------|---------------|---|-----------------|--------|-----------|-----------|----------|-----------|

|                 | 19       |        |              |             |             | 10-11 Cu    |                             |               |   |                 | 12     |           |           |          | 10-12 Cu  |

|                 | 18       |        |              |             |             |             |                             | Co IM (3)     |   |                 |        |           |           |          | HM (2-4)  |

|                 | 17       |        |              |             |             |             | 10.10.0.(*)                 | HM (4-12)     | 4 |                 | 11     | -         |           |          |           |

|                 | 16       |        |              |             |             |             | 10-13 Cu (*)<br>Co IM (0-2) | W Plugs       |   | ess             | 10     |           |           |          | W Plugs   |

| ess             | 15<br>14 |        |              |             |             |             | HM (2-6)                    | W-TS<br>Co-TS |   | 0               | 9      |           |           |          | W-TS      |

| Process         | 14       |        |              |             |             | 8-12 Cu (*) | W Plugs                     | HM            |   | Pro             |        |           |           | 10-12 Cu | SAC       |

|                 | 12       |        |              |             |             | HM (2-4)    | W-TS                        | SAC2          |   |                 | 8      |           |           | 10-12 Cu | SAC       |

| CMP             | 11       |        |              |             |             | W-Plugs     | SAC2                        | SAC1          |   | ber of CMP      | 7      |           |           | W Plugs  | W Gate    |

| 5               | 10       |        |              |             |             | W-TS        | SAC1                        | Co Gate       |   |                 | 6      | 9-10 Cu   | 9-10 Cu   | W-TS     | РОР       |

| of              | 9        |        |              |             |             | SAC         | W Gate                      | HM            |   |                 | 0      |           |           |          |           |

| er              | 8        |        |              |             |             | W-Gate      | HM                          | РОР           |   |                 | 5      | w         | W         | SAC      | ILD0      |

| Number          | 7        |        |              |             | 9-10 Cu (*) | НМ          | POP                         | ILDO          |   | dmuN            | 4      | AI/W Gate | AI/W Gate | W Gate   | Gate Poly |

| <u>n</u>        | 6        |        |              | 9-10 Cu     | W-Plugs     | РОР         | ILD0                        | Gate Poly     |   | lu l            |        | ,         | ,         |          |           |

| Z               | 5        |        | 7-8 Cu       | W           | W-TS        | ILDO        | Gate Poly                   | III-V         |   | ~               | 3      | РОР       | POP       | POP      | HM        |

|                 | 4        | 7-8 Cu | W            | AI / W Gate | AI/W Gate   | Gate Poly   | SiGe                        | SiGe          |   |                 | 2      | ILD       | ILD       | ILD      | STI2      |

|                 | 3        | W      | Al Gate      |             | POP         | HM          | HM                          | HM            |   |                 |        | CTI       | CTI       | CTI      | CT11      |

|                 | 2        | ILD    | ILD          | ILD         | ILD         | STI2        | STI2                        | STI2          |   |                 | 1      | STI       | STI       | STI      | STI1      |

|                 | 1        | STI    | STI          | STI         | STI         | STI1        | STI1                        | STI1          |   | # CMP           | Laver  | 15        | 15        | 19       | 25        |

| # CMP           | Layer    | 10     | 12           | 14          | 15          | 18-25       | 24-30                       | 25- 34        |   |                 | ecture | FDSOI     | Planar    | FDSOI    | FinFET    |

| Testa i         |          |        | 1m 45nm 28nm |             | 20nm        | 16/14/10nm  | 7nm                         | 5nm           |   |                 |        |           |           |          |           |

| Technology Node |          | Planar |              | нкмд        |             | FinFETs     |                             | GAA           |   | Technology Node |        | 28nm 14   |           | Inm      |           |

(\*) Co/TaN barrier in IM

|                    |    |             | Ν            | lemory      |                  |                   |             |

|--------------------|----|-------------|--------------|-------------|------------------|-------------------|-------------|

|                    | 16 |             |              |             |                  |                   | Cu (X)      |

|                    | 15 |             |              |             |                  |                   | W via (X)   |

|                    | 14 |             |              |             |                  |                   | w           |

| v.                 | 13 |             |              | ILD         |                  | Cu (X)            | W (X)       |

| sec                | 12 |             | ILD          | Cu (X)      |                  | W via (X)         | W (X)       |

| Process            | 11 |             | Cu           | W via (X)   |                  | w                 | HM (X)      |

|                    | 10 |             | W via (X)    | TiN         |                  | W (X)             | ILD4        |

| CMP                | 9  | Cu          | TiN          | ILD4        | 1                | ILD3              | ILD3        |

| of (               | 8  | W via (X)   | ILD4         | ILD3        | Cu               | SoP (X)           | SoP (X)     |

|                    | 7  | w           | ILD3         | W (X)       | W (X)            | Poly (X)          | Poly (X)    |

| Number             | 6  | ILD3        | W (X)        | ILD2        | ILD              | SoN (X)           | SoN (X)     |

| n                  | 5  | Ox Buff (X) | ILD2         | HM Buff (X) | w                | HM Buff (X)       | HM Buff (X) |

| z                  | 4  | ILD2        | Poly         | Poly        | ILD              | ILD2              | ILD2        |

|                    | 3  | Poly        | ILD1         | ILD1        | Poly             | ILD1              | ILD1        |

|                    | 2  | ILD1        | Ox Buff      | Ox Buff     | Ox Buff (X)      | Ox Buff (X)       | Ox Buff (X) |

|                    | 1  | STI         | STI          | STI         | STI              | STI               | STI         |

| # CMP Layer        |    | 10          | 14           | 17          | 10               | 14-26             | 17-32       |

| Node<br>Technology |    | 3Xnm        | 2Xnm<br>DRAM | 1Xnm        | 2X - 1Xnm Planar | 3D 32-36L<br>NAND | 3D 48-64L   |

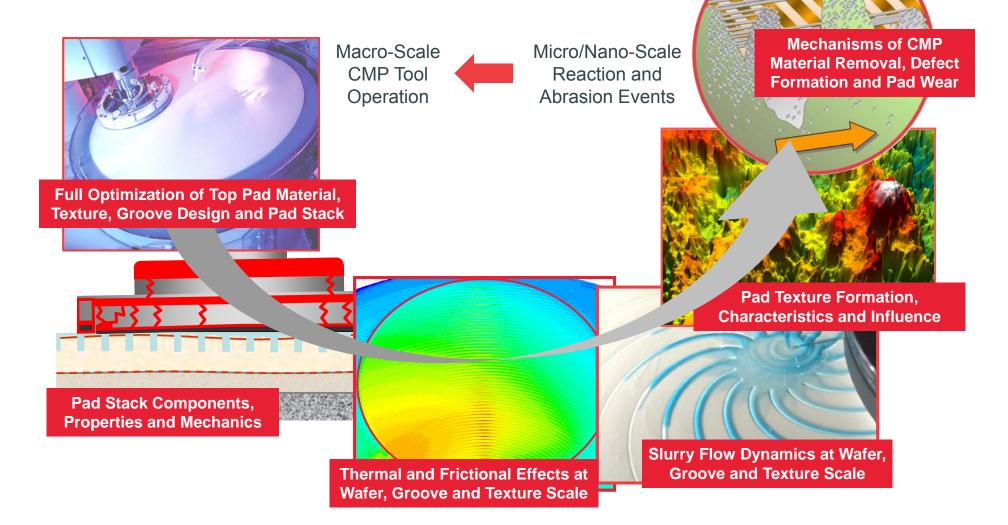

#### CMP Physics Across All Length Scales

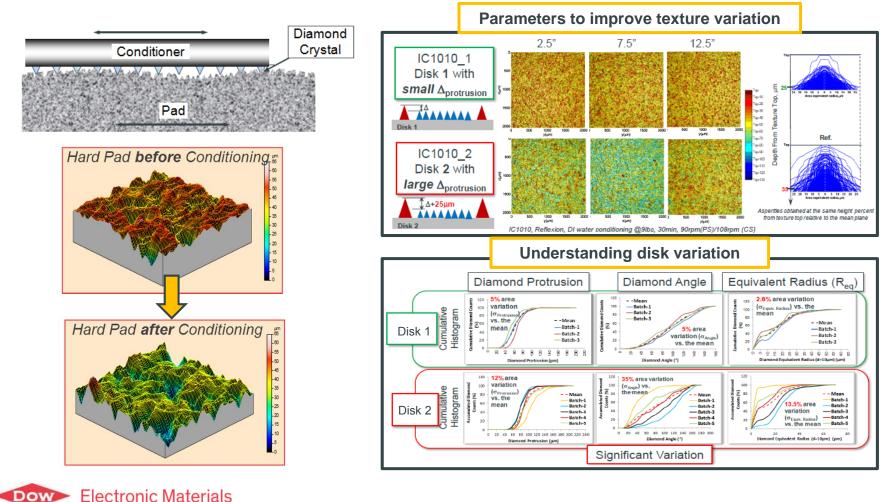

## **Improving Uniformity via Texture & Disk Characterization**

#### Advanced characterization enables precise quantification of:

- Pad texture morphology, uniformity and consistency through lifetime

- Conditioning disk diamond uniformity and wear characteristics

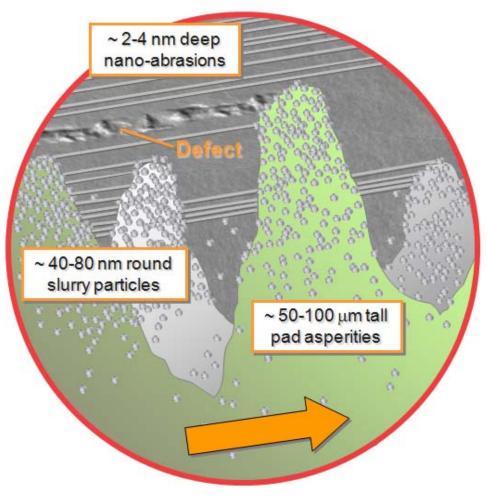

#### CMP Material Removal Events and Defect Events

- Typical CMP process removes 2000 – 8000 Å/min thickness across full surface of wafer

- Implies combination of

- O(10<sup>9</sup>) nano-abrasions by slurry particles

- O(10<sup>7</sup>) micro-abrasions by full asperity tips

- Typical CMP defect counts are O(10) – O(100) defects

- Malfunctions of abrasion that incur defect happen only once in 100,000 to 100,000,000 events

Approaches to defect reduction involve combinations of physical and chemical approaches to minimize the probability of formation or impact of defect forming particles

**Dow** Electronic Materials

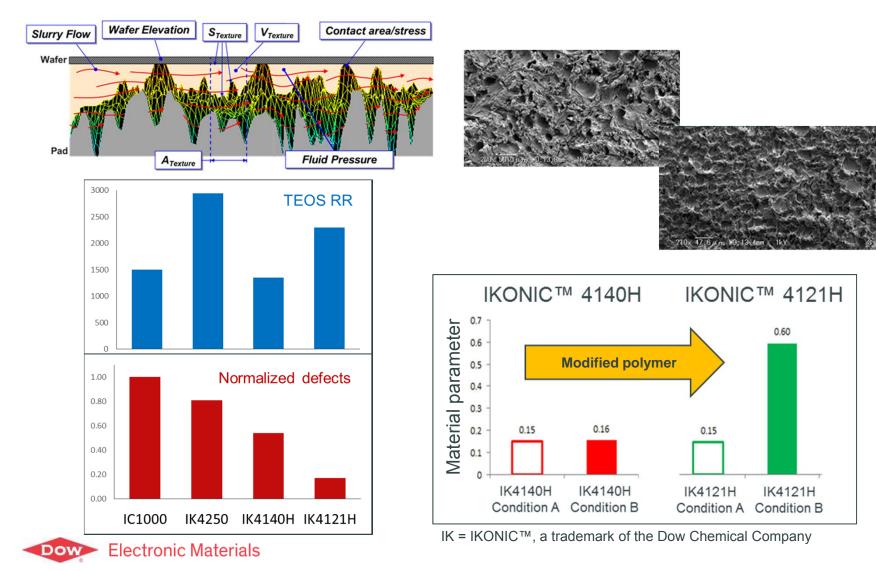

## **Defect Improvement by Polymer Engineering**

Order of magnitude defect improvement possible by polymer design while enabling high PE / RR

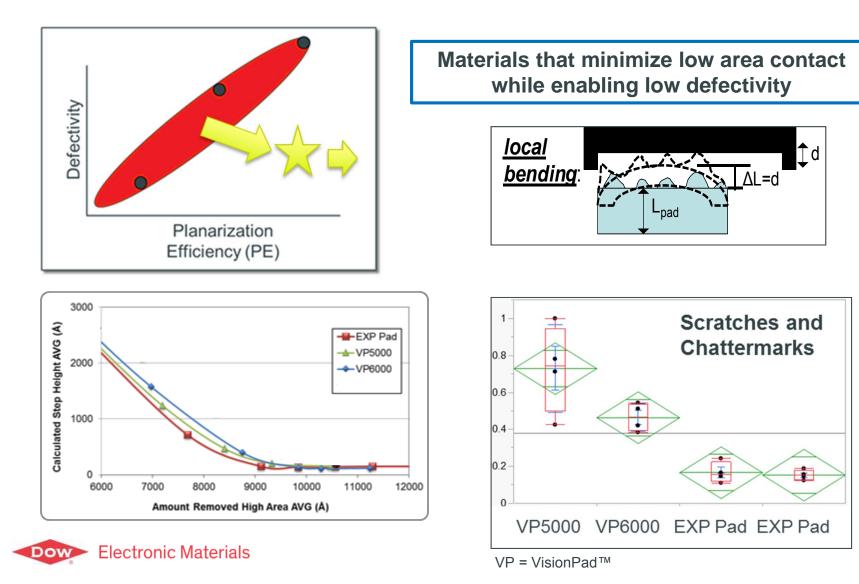

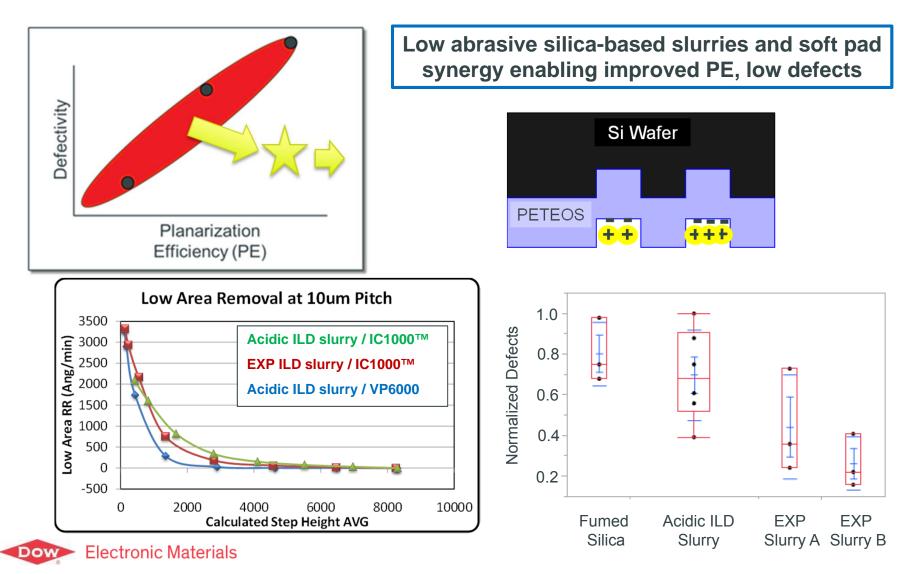

## Challenges in Planarization: Breaking Conventional Trade-offs in PE and Defectivity

## Challenges in Planarization: Breaking Conventional Trade-offs in PE and Defectivity

#### Challenges in Planarization: Long Length PE

## Challenges in Planarization: Long Length PE

## Change in CMP Complexity: **Top Challenges for Advanced Devices**

#### Wafer-scale control in FEOL for FinFET devices

- Narrow window of operation: tighter lot-to-lot and with-in lot variation

- Stringent thickness control requirements:

- Edge profile control and consistency is critical

#### **Reduced topography and defect tolerance**

- Challenging selectivity requirements

- Low dishing, high PE is increasingly important

- Incoming topography < typical CMP capability</p>

- More CMP near the transistor dishing and defects!

- Emphasis on reduction of micro-scratch count and depth

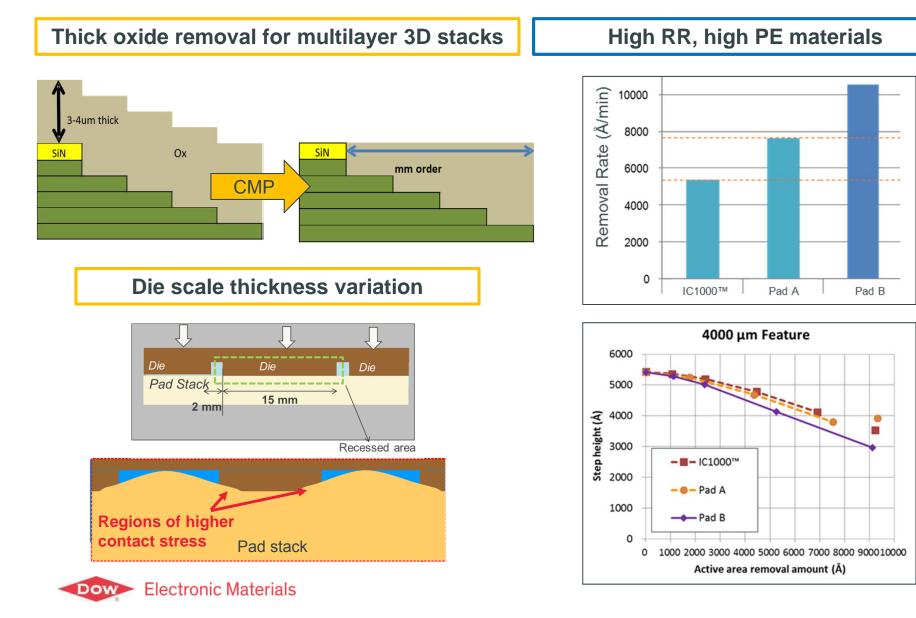

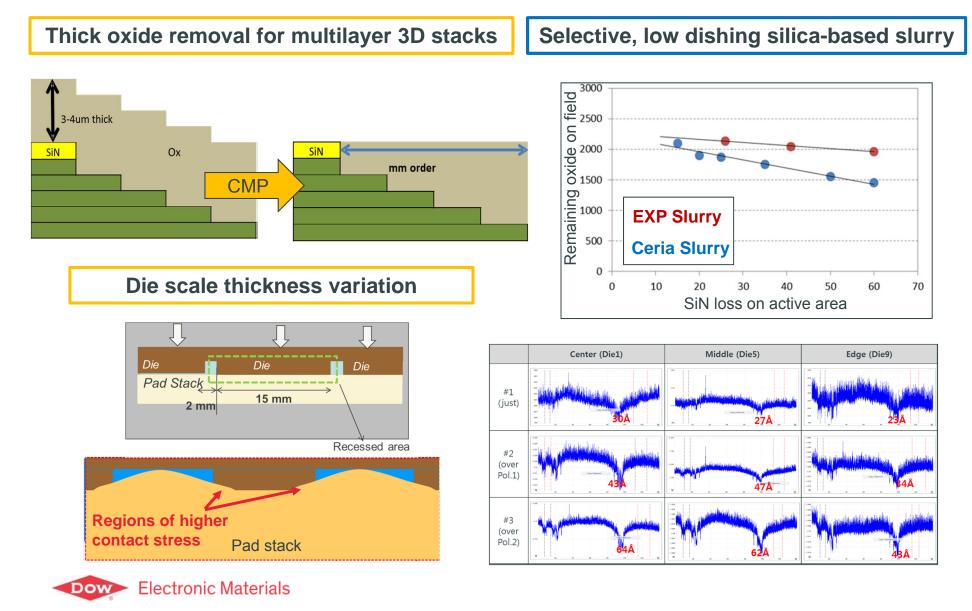

#### **3D stack designs**

- High removal rate for microns thick oxide films

- High planarization and low dishing across mm features

Materials that break **PE/defect trade-offs**

Products that extend planarization length

- **High RR materials**

- Selective. low dishing silica slurry

**Dow** Electronic Materials

# Thank You

Copyright © The Dow Chemical Company. All Rights Reserved. ®™ Trademark of The Dow Chemical Company ("Dow") or an affiliated company of Dow