# CMP's Transition to 450mm Manufacturing: Current Status and Future Directions

Christopher Borst<sup>1</sup>, Daniel Franca<sup>1</sup>, Huey-Ming Wang<sup>2</sup>

1 – SUNY Polytechnic Institute, assignee to G450C 2 – GLOBALFOUNDRIES, assignee to G450C

College of Nanoscale Science and Engineering Albany, NY

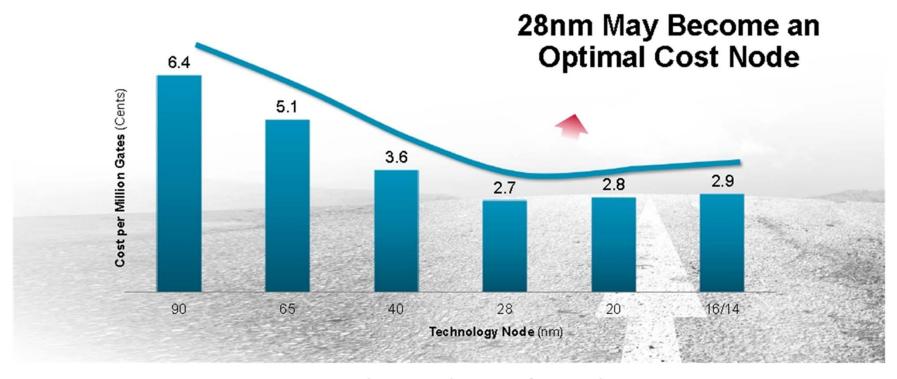

### **Development Cost Drivers**

### COST PER TRANSISTOR RISING - HISTORIC FIRST

- Scott McGregor, President and CEO of Broadcom, January 2015

"...exponential factors (complexity of devices; cost of equipment) are now starting to drive the cost forward. This is going to drive some change..."

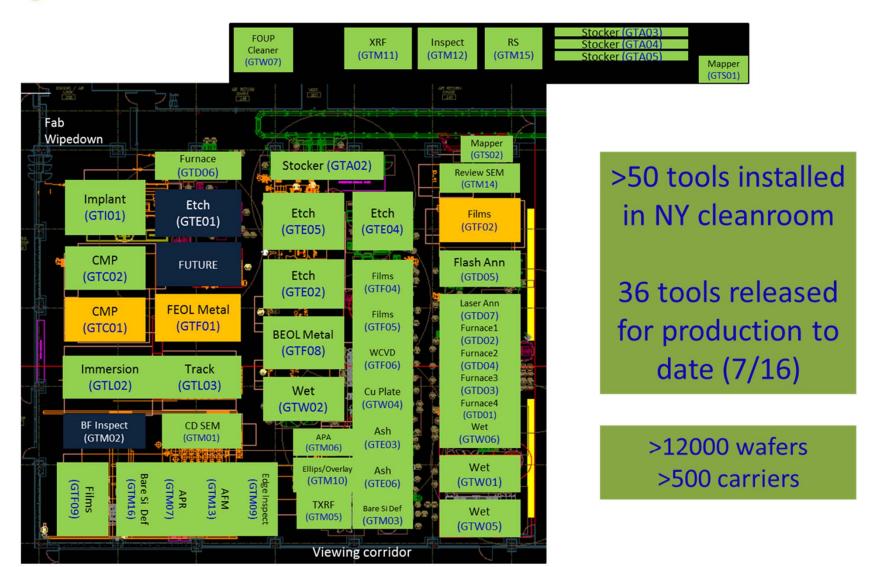

### **Global 450mm Consortium (G450C)**

## What has the Global 450 Consortium (G450C) Program Accomplished?

- Established the 450mm wafer and equipment development environment (wafers, carriers, supply chain)

- Installed and evaluated >50 pieces of equipment, including immersion lithography and 96% of applications for full flow process

- Created non-IP test masks and structures for STI and BEOL short loops

- Established initial metrics and capabilities for examining subfab (resource) consumption

- Met or exceeded goals for generating data on tools, applications

www.g450c.org

### **G450C Operations – NFX Cleanroom**

### **Equipment Performance Metrics (EPM)**

G450C rolled out an EPM update in 2014 that established 10nm node targets for 450mm equipment

#### 450mm Publications

| Document Number | Document Name                                                                         | Publication<br>Date |

|-----------------|---------------------------------------------------------------------------------------|---------------------|

| 072014          | G450C Equipment Performance Metrics (EPM) Published Guidelines for Sub-10nm July 2014 | 07/30/2014          |

A fourth CMP application (Si CMP) was added to the EPM:

| A.2 <u>CMP</u> |     |                |                                   |  |

|----------------|-----|----------------|-----------------------------------|--|

| A.2.1          | CMP | Dielectric CMP | Planarization Dielectric Films    |  |

| A.2.2          | CMP | Metal CMP      | Plug/Metal gate polish            |  |

| A.2.3          | CMP | Metal CMP      | Damascene - Copper/barrier Polish |  |

| A 2.4 - New    | CMP | Si CMP         | Si/Poly-Si/a-Si CMP               |  |

### **CMP EPM - Oxide**

#### 2.1 Dielectric CMP - Planarization Dielectric Films

| Category    | Attribute                                   | Units                   | 14nm     | < 10nm   | Notes                              |

|-------------|---------------------------------------------|-------------------------|----------|----------|------------------------------------|

|             |                                             |                         | Metrics  | Metrics  |                                    |

| Equipment   | auto pad condition                          | NA                      | required | required |                                    |

| Performance | in-situ thickness monitoring                | NA                      | required | required |                                    |

|             | end point detection                         | NA                      | required | required |                                    |

|             | automated process control                   | NA                      | required | required | Capable of<br>integrating with APC |

|             | integrated with post CMP clean              | NA                      | required | required |                                    |

|             | dry-in & dry-out                            | NΔ                      | required | required |                                    |

| Process     | RR total variability (3σ)                   | %                       | < 4      | < 2.8    |                                    |

| Targets     | RR within wafer uniformity (3σ)             | %                       | < 3      | <2.1     |                                    |

|             | dielectric thinning (10~20% over polish)    | inning (10~20% nm SOBT3 | SOBT3    | SOBT3    | SOBT3 = same or better             |

|             | removal rate                                | nm/min                  | SORT3    | SORT3    | than 300mm tool                    |

|             | removal rate stability parameter            | %                       | < 5      | < 5      | drift, pad life > 500<br>wafers    |

|             | dishing/over/under erosion, patterned wafer | nm                      | 5        | 3.5      |                                    |

|             | edge exclusion                              | mm                      | 1.5      | 1.5      |                                    |

### **CMP EPM – Oxide (continued)**

#### 2.1 Dielectric CMP - Planarization Dielectric Films

|     | Category                   | Attribute                             | Units     | 14nm<br>Metrics     | < 10nm<br>Metrics   | Notes                                     |

|-----|----------------------------|---------------------------------------|-----------|---------------------|---------------------|-------------------------------------------|

| ш   | Process<br>Characteristics | slurry waste                          | LPM/wafer | < 1.5X of<br>300mm  | < 1.5X of<br>300mm  |                                           |

|     |                            | pad consumption                       | wafers    | > 1200              | > 1200              | rate on per platen<br>basic / all platens |

| - 1 | Defect<br>Performance      | PWP on bare Si                        | #/cm²     | ≤ 0.002 @ ≥<br>30nm | ≤ 0.002 @ ≥<br>21nm |                                           |

| -   |                            | PWP on backside Si                    | #/cm²     | ≤ 0.28 @ ≥<br>50nm  | ≤ 0.28 @ ≥<br>50nm  |                                           |

| 1   |                            | critical scratch length               | nm        | 10                  | 7                   |                                           |

| L   |                            | critical scratch count                | #/wafer   | 50                  | 50                  |                                           |

| Γ   | Manufacturing              | Availability                          | %         | > 95                | > 95                |                                           |

| 1   | Target (@HVM)              | MTBF                                  | hours     | > 350               | > 350               |                                           |

| -   |                            | MTTR                                  | hours     | < 3                 | < 3                 |                                           |

|     |                            | productivity scalar relative to 300mm |           | ≥1                  | ≥1                  |                                           |

|     |                            | foot print scalar relative to 300mm   |           | ≤1                  | ≤1                  | normalized to run<br>rate                 |

<sup>\*</sup> CMP is one of the key processes where consumables cost must be brought down significantly, either with new designs for 450 mm or engineering improvements over time

### **CMP EPM – Oxide – Current Status**

#### 2.1 Dielectric CMP - Planarization Dielectric Films

| Category    | Attribute                                   | Units  | 14nm     | < 10nm   | Notes                           |

|-------------|---------------------------------------------|--------|----------|----------|---------------------------------|

|             |                                             |        | Metrics  | Metrics  |                                 |

| Equipment   | auto pad condition                          | NA     | required | required |                                 |

| Performance | in-situ thickness monitoring                | NA     | required | required |                                 |

|             | end point detection                         | NA     | required | required |                                 |

|             | automated process control                   | NA     | required | required | Capable of integrating with APC |

|             | integrated with post CMP clean              | NA     | required | required |                                 |

|             | dry-in & dry-out                            | NΔ     | required | required |                                 |

| Process     | RR total variability (3σ)                   | %      | < 4      | < 2.8 🗶  |                                 |

| Targets     | RR within wafer uniformity                  | %      | < 3      | <2.1     |                                 |

|             | (3σ)                                        |        |          | V        |                                 |

|             |                                             |        |          |          |                                 |

|             | dielectric thinning (10~20% over polish)    | nm     | SOBT3    | SOBT3    | SOBT3 = same or bette           |

|             | removal rate                                | nm/min | SORT3    | SORT3    | than 300mm tool                 |

|             | removal rate stability parameter            | %      | < 5      | <5 ✓     | drift, pad life > 500<br>wafers |

|             | dishing/over/under erosion, patterned wafer | nm     | 5        | 3.5      |                                 |

|             | edge exclusion                              | mm     | 1.5      | 1.5 🗶    |                                 |

RR total variability  $(3\sigma)$  = SQRT[ (WTW variation-3 $\sigma$ )<sup>2</sup> + (WIWNU%-3 $\sigma$ )<sup>2</sup>]

### **CMP EPM – Oxide – Current Status**

#### 2.1 Dielectric CMP – Planarization Dielectric Films

| Category        | Attribute                     | Units             | 14nm        | < 10nm      | Notes               |

|-----------------|-------------------------------|-------------------|-------------|-------------|---------------------|

|                 |                               |                   | Metrics     | Metrics     |                     |

| Process         | slurry waste                  | LPM/wafer         | < 1.5X of   | < 1.5X of   |                     |

| Characteristics | V                             |                   | 300mm       | 300mm       |                     |

|                 | pad consumption               | wafers            | > 1200      | > 1200      | rate on per platen  |

|                 | V                             |                   |             |             | basic / all platens |

| Defect          | PWP on bare Si                | #/cm <sup>2</sup> | ≤ 0.002 @ ≥ | ≤ 0.002 @ ≥ |                     |

| Performance     | <b>V</b>                      |                   | 30nm        | 21nm        |                     |

|                 | PWP on backside Si            | #/cm <sup>2</sup> | ≤ 0.28 @ ≥  | ≤ 0.28 @ ≥  |                     |

|                 |                               |                   | 50nm        | 50nm        |                     |

|                 | critical scratch length       | nm                | 10          | 7           |                     |

|                 | critical scratch count        | #/wafer           | 50          | 50          |                     |

| Manufacturing   | Availability                  | %                 | > 95        | > 95        |                     |

| Target (@HVM)   | MTBF                          | hours             | > 350       | > 350       |                     |

|                 | MTTR                          | hours             | < 3         | < 3         |                     |

|                 | productivity scalar relative  |                   | ≥1          | ≥1          |                     |

| /               | to 300mm                      |                   |             |             |                     |

| <b>✓</b>        | foot print scalar relative to |                   | ≤1          | ≤1          | normalized to run   |

|                 | 300mm                         |                   |             |             | rate                |

<sup>\*</sup> CMP is one of the key processes where consumables cost must be brought down significantly, either with new designs for 450 mm or engineering improvements over time

### **Consumables Directions for 450mm**

What may drive CMP consumable differences for 450mm

equipment?

☐ Standard :6rings, 144 points

- From the EPM:

- Equivalent process performance to 300

- Equivalent equipment productivity to 300

- Edge exclusion 1.5mm

- Equivalent normalized throughput

- Assume the probability of equipment configuration change due to size increase (2 platens)

- ✓ Albany have 2platen config

300mm area 65 points

start radius: 37.25mm

- Assume that requirements of process/equipment yield for 450mm will drive CMP control improvements

- (Wafer scrap hurts 2.25x as much)

### **Consumables Directions for 450mm - Slurry**

Co-develop / optimize slurry sets for larger wafers, while keeping flow rates reasonable

- Improvement of slurry stability / manufacturing tolerances

- 10 nm node requires lower defectivity; tighter particle size control

- Better stability within drum, local reservoir, and slurry loop

- Compatibility with inline or loop filtration (higher flow rates, more susceptible to shear)

- Successful and stable dilution in sub-fab and on-platen

- On-platen mixing

- Two-platen designs could drive higher instance of 'high rate and soft-landing' slurries on one platen

- 'Slurry sets' with ensured compatibility could be much more important

Tracking with 10nm node needs for 300mm

Defectivity/

yield still largely

unknown

(patterned

wafers / test)

Does not seem to be necessary, or a direction of development driven by

### **Consumables Directions for 450mm - Pad**

Pad development for >40 inch platen must continue along (and expand upon) recent advancing trends

- Optimization of pad materials and groove configuration

- to complement 10nm node advanced slurry engineering

- to maximize performance with larger wafers

- to further enable efficient on-platen slurry mixing or transition

- Uniformity of pad material properties

- across pad (larger area, larger wafer contact area)

- pad-to-pad (single-cast or batch uniformity controls)

- Maintain compatibility with improving process control / endpoint systems

Each of these items show preliminary promise (initial results good), but very few pad investigations have been performed due to small demand to date

Patterned wafers, and more CMP applications examined will provide the basis for further engaging the supply chain for improvements as needed

### **Consumables Directions for 450mm - Disk**

Diamond conditioning, and other modes of pad refreshing or cleaning, increase in importance for >40 inch platens

- Platen size could drive disk changes

- larger disks, and/or multiple disks per pad

- better control / predictability at higher pressures may be required to maintain through-life pad performance

- Platen size increase would benefit from improved 'conditioner efficiency'

- higher slurry flow rates, larger slurry 'capture area' under wafer

- developing a better disk, the physics of which are better understood, that complements pad cleaning may have differentiating advantages

One tool in Albany uses larger disks; the other was built to allow 2 disks per pad

Patterned

wafers, and

more CMP

application

results will

provide the

basis for further

engaging the

supply chain for

improvements

as needed

### Summary

G450C's mission has been to evaluate equipment capability versus the EPM specification – (now to 10nm node specs)

The certainties have been realized:

- Wafer and pad get bigger, and process/equipment scrap frequency must reduce

- IDMs require zero performance degradation vs 300mm (including defectivity) and are pushing aggressive targets to consumable consumption rates (and reduced edge exclusion)

Two initial assumptions are correct:

- Slurry flow rate increases (but <2.25x SFR; using slurry set same as 300mm)</li>

- Two-platen configurations will be more prevalent (observed in early G450C tools)

The basic projections still hold, with slightly more clarity to be provided as more wafers are processed and applications investigated. Observations will drive supply chain modifications as needed:

- Consumable manufacture specs and tolerances will only tighten; but yet to be fully determined

- On-platen slurry mixing may become more prevalent

- Residence time for cleaning away slurry from larger wafer during transitions will need to be investigated

- Pad properties and grooving must be optimized to slurry set (more to come as more pads are requested by development users)

450mm CMP tools are available now at CNSE, and preliminary results look very good. Further processing of metal applications and patterned wafers will confirm trends and define next challenges