# SUNY Polytechnic Institute Advanced Planarization Center of Excellence

Brian Sapp brian.sapp@sematech.org

July 16, 2015 SEMICON West 2015 – CMP Technical and Market Trends

- Advanced Planarization Center Overview

- Industry-Standard Mask Set and Baseline Process Flows

- Open Innovation Business Model

- Joint Development and Benchmarking

- Summary

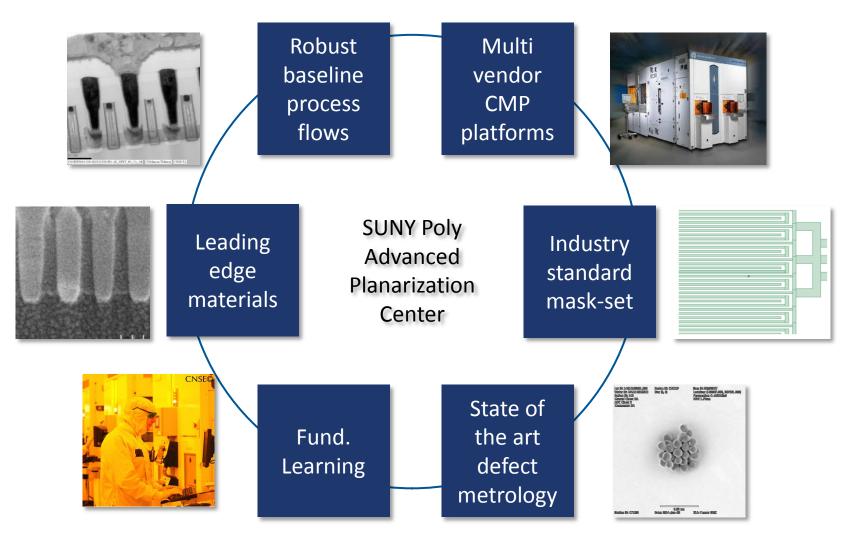

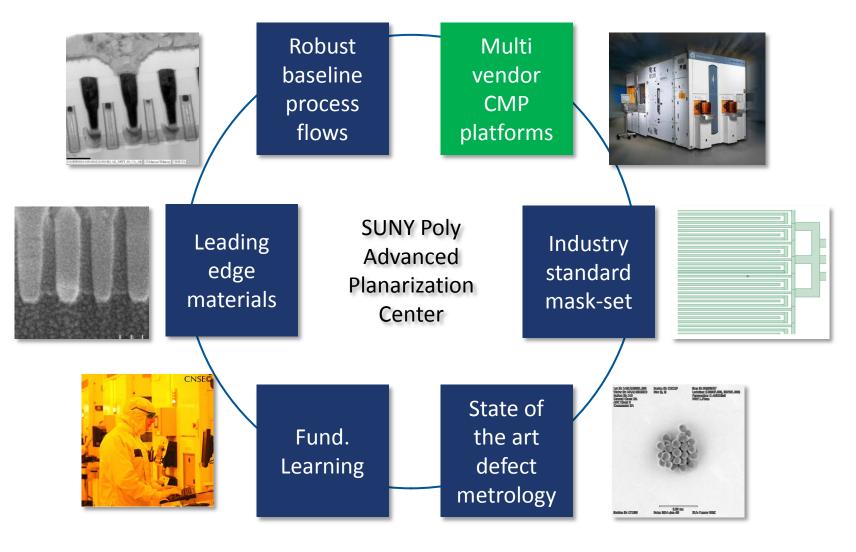

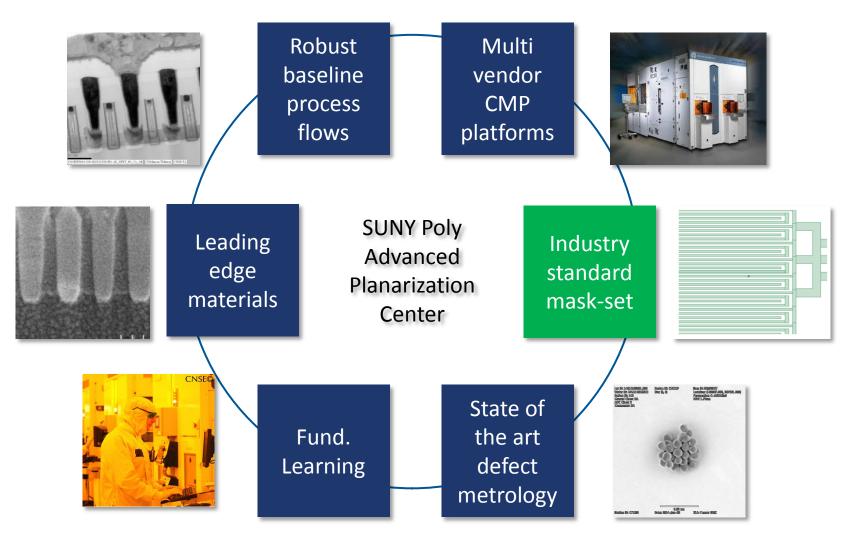

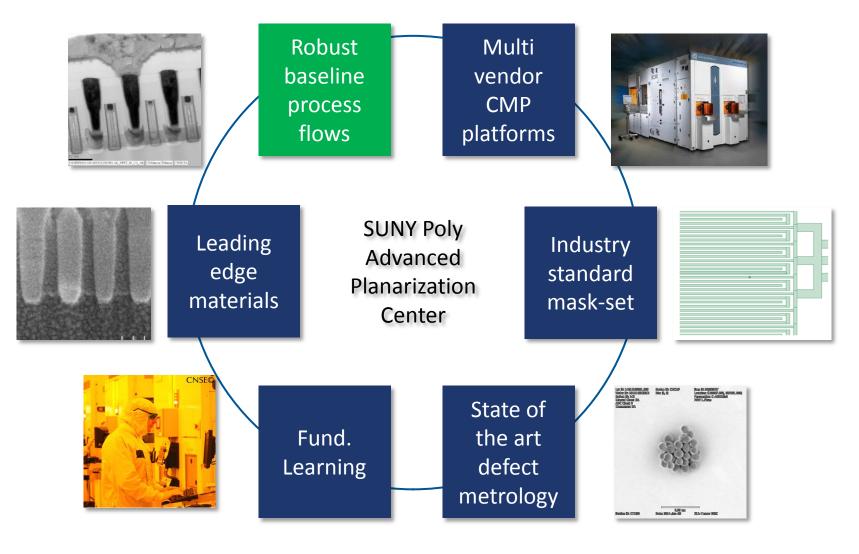

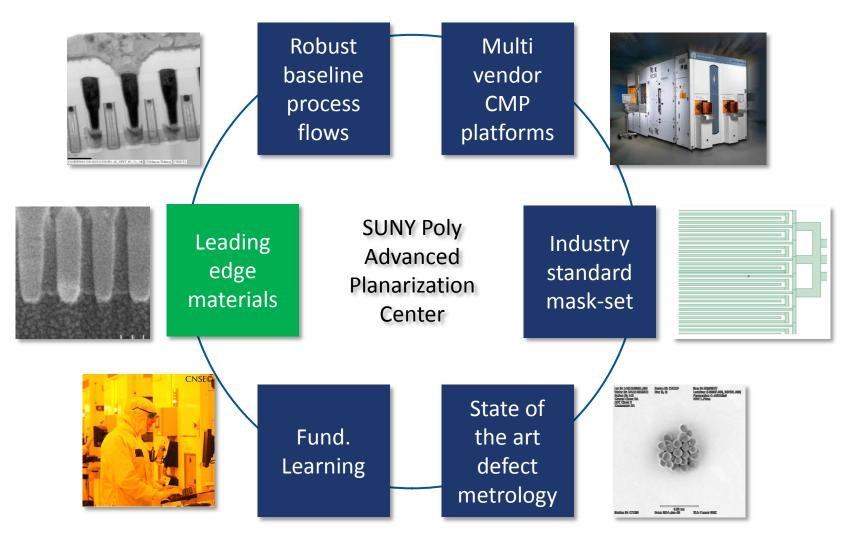

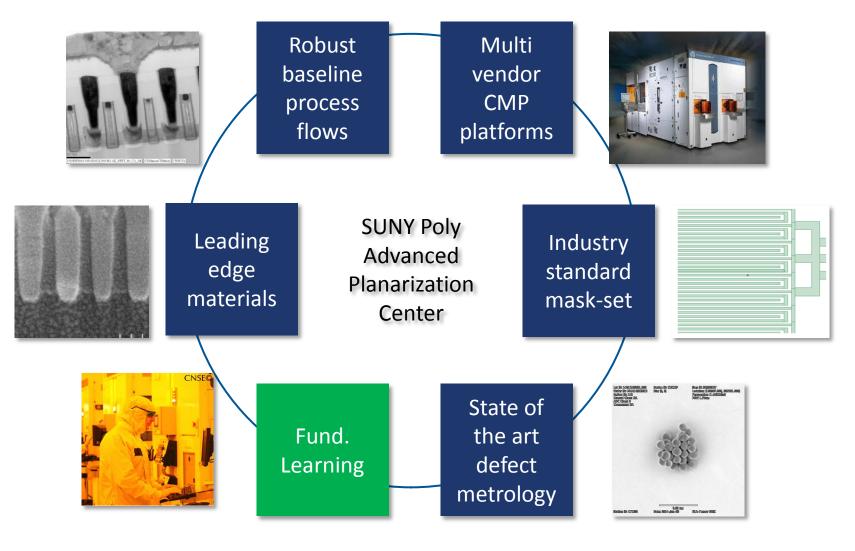

- SUNY Poly SEMATECH and SUNY Poly CNSE established a state-of-the-art Advanced Planarization Center with full foundry services for advanced-node CMP technology development

- Industry-standard mask set with structures for process fingerprinting, dummy fill evaluations, e-test and reliability structures, and advanced metrology features

- Robust fully integrated baseline process flows for all front-end-ofthe-line (FEOL) CMP levels and advanced back-end-of-the-line (BEOL) CMP levels

- Trusted framework for benchmarking among nominal industry competitors

- Suite of leading-edge characterization techniques for CMP consumables and wafer surfaces

#### **Advanced Planarization Center**

#### **Advanced Planarization Center**

#### Multi-Vendor CMP Platforms

#### Applied Materials Reflexion LK

- Profiler and Contour Heads

- Endpoint Motor Torque, FullVision RTPC, FullScan ISRM

- IPA Dryer

- NOVA, iMap on-board metrology

- Ebara F-Rex 300S

- GII and GIII Heads

- Endpoint Eddy Current, SOPM

- IPA Dryer

- Dedicated III-V CMP platform

#### **Advanced Planarization Center**

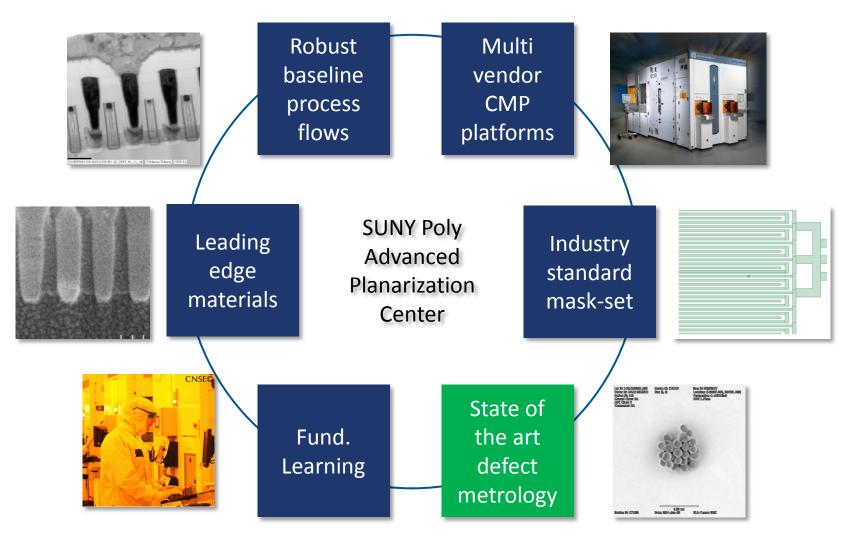

#### State-of-the-Art Defect Metrology

| Defect Inspection |                                              |  |  |

|-------------------|----------------------------------------------|--|--|

|                   |                                              |  |  |

| KLA SP1           | Blanket Defect Inspection >120nm             |  |  |

| KLA SP2           | Blanket Defect Inspection >60nm              |  |  |

| KLA SP3           | Blanket Defect Inspection >34nm              |  |  |

| KLA2835           | Particle Defects on Pattern Inspection >65nm |  |  |

| KLA2915           | Particle Defects on Pattern Inspection >45nm |  |  |

| Defect Review     |                                              |  |  |

| KLA eDR 5200      | Automated SEM Review                         |  |  |

| KLA eDR 7000      | Automated SEM Review w/ EDX                  |  |  |

| AMAT G2 SEM       | Semi-Automated SEM Review                    |  |  |

| WWW.SUNYIT.EDU •  | WWW.SUNYCNSE.COM • WWW.SEMATECH.ORG          |  |  |

#### Other Metrology and Characterization

- Full set of surface analysis and metrology tools including:

- Electron Microscopy (TEM, S/TEM, FIB-SEM, SEM)

- Scanning Probe Microscopy (Bruker Icon, Veeco 3D Insight)

- Electrical Testing (multiple semi/automated stations)

- Surface Spectroscopy (AES, XPS, ToF-SIMS, XRD/XRR, Raman, Ellipsometry)

#### Bruker Icon AFM

Electrical measurements, material property mapping, surface-particle interactions, adhesion, friction

FEI Titan S/TEM 70pm resolution, Super-X EDS chemical characterization

WWW.SUNYIT.EDU

WWW.SUNYCNSE.COM

WWW.SEMATECH.ORG

#### **Advanced Planarization Center**

#### Industry-Standard Mask Set: Past

- SEMATECH/MIT mask set became the de facto CMP workhorse for the industry in the late 1990's

- Twenty years of scaling & new materials demand an updated industry-standard mask set to meet sub-14nm challenges

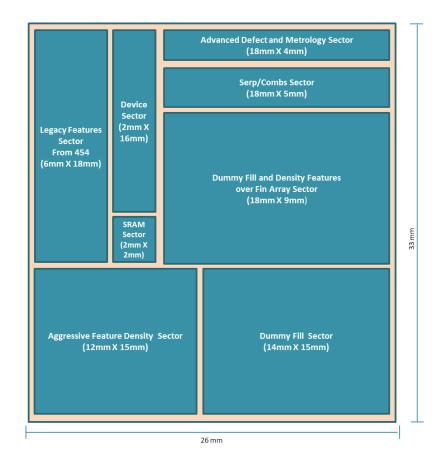

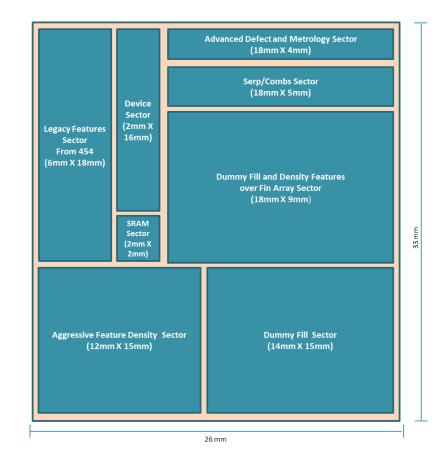

# SUNY POLYTECHNIC Industry-Standard Mask Set: Present

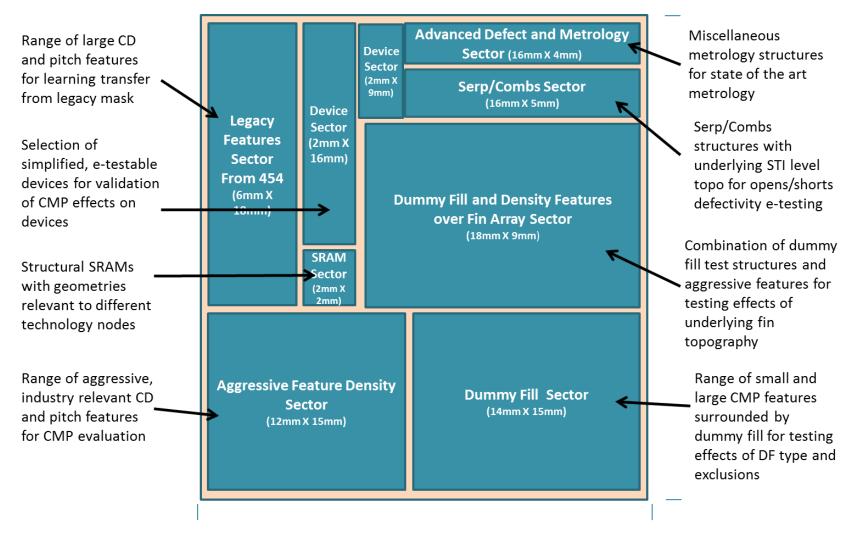

- Features FEOL and BEOL structures for process fingerprinting, dummy fill evaluations, e-test and reliability, and advanced metrology

- Allows for CMP process and consumables testing at relevant critical dimensions

# SUNY POLYTECHNIC Industry-Standard Mask Set: Present

#### □ 14nm FEOL Design

- Macro definitions completed

- Seven process levels

- Supports SADP, FIN, RMG, Gate/Contact LE, & High-K process development

- Layout completed design rule check at mask house

- Taped out July 2015

#### 14nm BEOL Design

- Technical team defining macros and reliability test structures

- Electromigration

- TDDB

- Tape out on schedule for 15Q4

WWW.SUNYCNSE.COM

WWW.SEMATECH.ORG

### Industry-Standard Mask Set: Present

#### **Advanced Planarization Center**

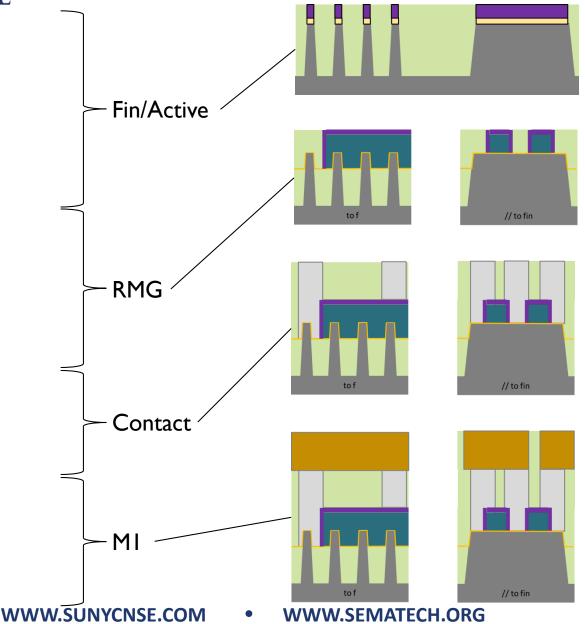

#### SUNY POLYTECHNIC INSTITUTE HM1, HM2 & mandrel dep

Mandrel litho & etch (stop on HM2)

SIT spacer dep and etch

Cut mask litho & etch (stop on HM2) Block litho

Etch HM2, HM1 and fin/active

Oxide fill and CMP

Poly dep & CMP

Gate litho (40/96nm) & etch

Spacer dep & etch (SiN)

ILD 0 dep & POP CMP

HK/MG dep & CMP (TiN/W)

MG recess, SiN dep &  $\ensuremath{\mathsf{CMP}}$

ILD 1 dep

#### Contact litho

Contact etch & fill (Ti/TiN/W)

IMD dep

M1 litho & etch

M1 fill (TaN/Ta/Cu) & CMP

WWW.SUNYIT.EDU

#### **Robust Baseline Process Flows: FEOL**

**Robust Baseline Process Flows**

- 14nm FEOL

- STI CMP

- Poly CMP

- **POP CMP**

- W CMP

- Contact CMP

- 14nm BEOL

- M1 CMP

- M2\V1 CMP

- M3\V2 CMP

- Al CMP

- Health-of-the-line (HOL) maintained, monitored, and record by SPC

- Process, Defectivity, E-test

#### **Advanced Planarization Center**

Leading-edge deposition process capability at SUNY Poly CNSE

Including TEL, Applied Materials, Lam Research

- Industry-relevant materials and materials stacks for integrated learning

- Including III-V, SiC, high-k, low-k, W, Co, Ru, TaN/Ta, TiN/Ti, Cu

### Leading Edge Materials: Case Study

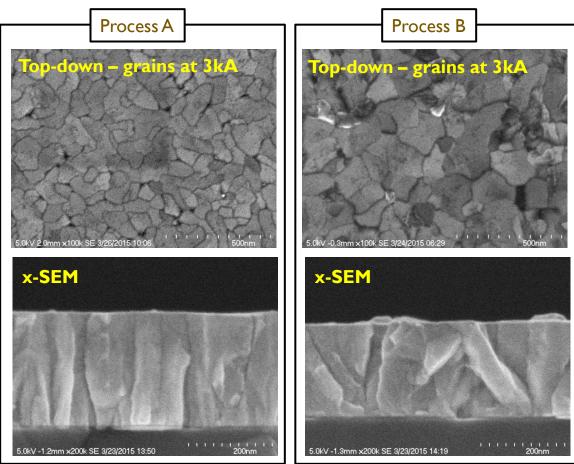

#### **Tungsten films difference and CMP performance impact**

CMP center provides access to processes for W CMP evaluation on both patterned and blanket test structures.

WWW.SUNYIT.EDU

WWW.SUNYCNSE.COM

#### **Blanket Tungsten Film Properties:**

|                                      | Process A | Process B |

|--------------------------------------|-----------|-----------|

| Grain Size at 3000A<br>thickness, nm | 80-100    | 166-200   |

| Grain size at 500A<br>thickness, nm  | 40-50     | 90-100    |

| 3000A W film Wafer<br>Bow, um        | 380       | 275       |

| 3000A W Film<br>Resistivity, Ohms/sq | 0.325     | 0.316     |

| 2000A W film Wafer<br>Bow, um        | 280       | 194       |

| 2000A W Film<br>Resistivity, Ohms/sq | 0.61      | 0.510     |

| 500A W Film<br>Resistivity, Ohms/sq  | 3.16      | 2.58      |

W films properties are significant in determining CMP performance: including initiation phase, removal rates and residual roughness.

WWW.SEMATECH.ORG

#### **Advanced Planarization Center**

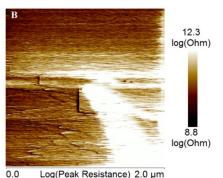

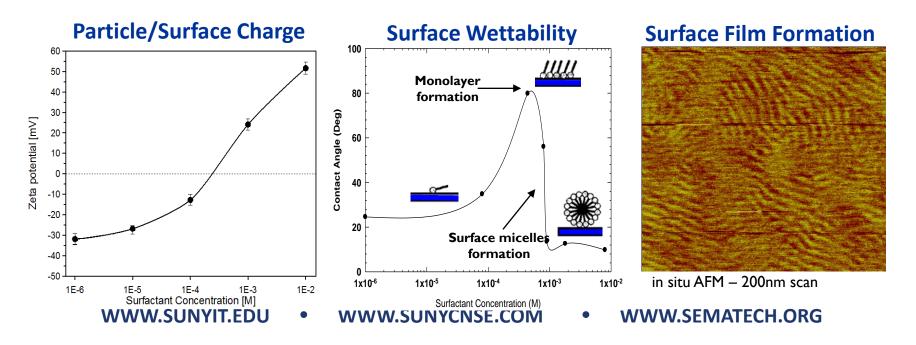

- Analysis of surface state of slurry particles, pad and wafer surfaces for fundamental understanding of CMP and post-CMP cleaning systems

- Studies of influence of surface active slurry and cleaner components on:

- Surface charge/zeta potential

- Wettability/interfacial energy

- **Film formation/steric barrier**

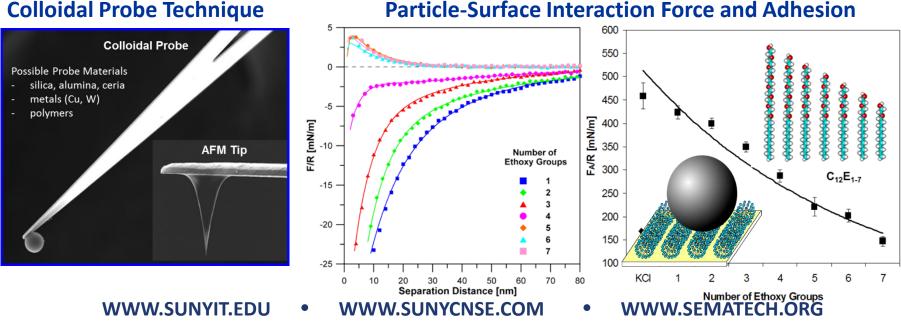

- Comprehensive analysis of interaction forces, adhesion, and nanoscale П friction between components in CMP and post-CMP cleaning using stateof-the art AFM system

- Influence of slurry and cleans chemistry on interaction forces and adhesion

- Characterization of surface state (surface charge/potential, surface energy)

- Characterization of surfactants and water soluble polymers

- Adhesion mapping and nanoscale friction analysis

#### **Particle-Surface Interaction Force and Adhesion**

- The world of R&D collaboration has fundamentally changed

- There are very few places in the world with access to leading edge CMOS manufacturing that are open to truly collaborative research

- There is no supplier today that can afford the leading edge manufacturing infrastructure that chip makers use today for in-house development

- Given the industry consolidation it has become more difficult for supplier to directly partner with chip manufacturers without their development becoming "captive"

- □ SUNY Poly enables truly collaborative research in a leading R&D facility

- Access to state of the art equipment and processes

- A business model that enables suppliers to develop their material, products and IP without becoming captive to a single company

- Opportunity to engage in collaborative research at desired levels from infrastructure access only to fully engaged collaborative research projects

- Flexibility to grow R&D efforts at the desired pace driven by economic development and available opportunities at SUNY Poly SEMATECH

Typically multi-year JDP engagements with projects mutually selected to deliver highest ROI

- Near-term goals chosen to be consistent with long-term strategic goals

- Mix of JDP and benchmarking projects may be run concurrently

- The Advanced Planarization Center's platform provides a framework for the entire CMP community to participate in benchmarking exercises

- Perform on site evaluation of consumables (eg pads) with other selected commercially available consumables (eg slurries)

- Conduct post-CMP metrology and provide appropriately sanitized reports

- The SUNY Poly Advanced Planarization Center is the global leader for CMP research and development and has the experts, resources and open innovation business model to support the industry

- Industry-standard mask set with structures for process fingerprinting, dummy fill evaluations, e-test and reliability structures, and advanced metrology features

- Robust fully integrated baseline process flows for all front-endof-the-line (FEOL) CMP levels and advanced back-end-of-the-line (BEOL) CMP levels

- Trusted framework for benchmarking among nominal industry competitors

- Suite of leading-edge characterization techniques for CMP consumables and wafer surfaces

## 450mm CMP Update

#### **Christopher Borst**

christopher.borst@g450c.org

### July 16, 2015 SEMICON West 2015 – CMP Technical and Market Trends

G450C Key Messages

- The Program and Suppliers continue to achieve excellent technical results

- 51 Tools in Albany

- Nikon Scanner arrived in Albany First Patterned wafers in September 2015

- Notchless wafers with 1.5mm edge exclusion is the Semi standard

- All partners supporting equipment set in NY through Q1 2017

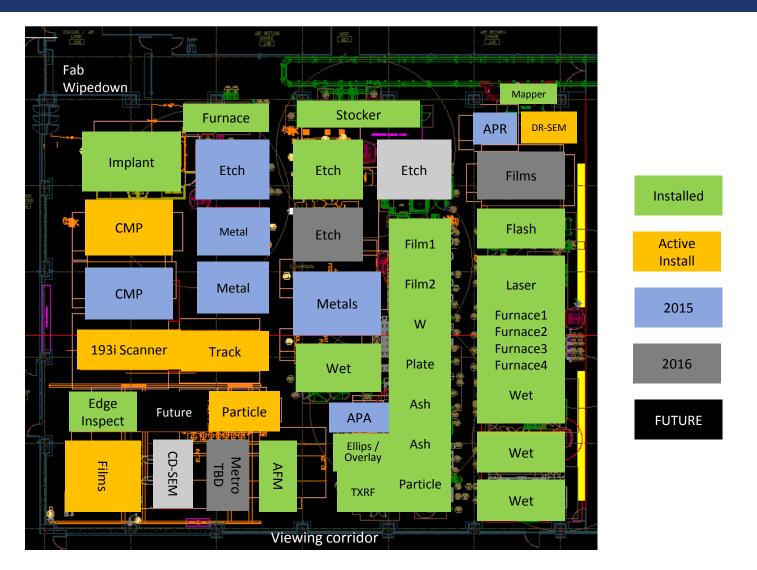

## G450C Fab Layout

- Two 450mm CMP Tools are to be installed at G450C

- Both tools will have process demos on Oxide, STI, Cu, and W

- The 1st 450mm CMP tool installation completed Jun'15

Tool process qualification on Oxide CMP is on-going

Qual of STI & Cu processes will follow

- The 2nd 450mm CMP tool starts installation 4Q'15

Tool is still used for Cu process demos at supplier site

- Qual of W CMP processes on both tools will start 2Q'16

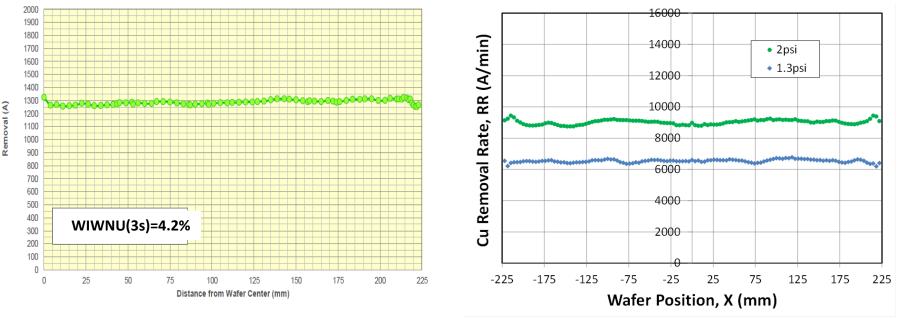

## **GTC01** Performance

### Oxide CMP Process

- Best performance at 1.4psi

- 1.4psi: Removal Rate = 1300 A/min

- WIWNU% (3σ) = 4.2% @ 2mmEE

#### Cu CMP Process

- Best Cu performance

- 2.0psi: Removal Rate = 8970 A/min

- WIWNU% (3σ) = 6.3% @ 3mm EE

- 1.3psi: Removal Rate = 6540 A/min

WWW.SUNYIT.EDU

WWW.SUNYCNSE.COM

WWW.SEMATECH.ORG

## GTC02 Performance

### Oxide CMP Process

- Best performance at 2.0psi

- WIWNU% (3σ) = 3.6% @ 2mm EE

### Cu CMP Process

- Best Cu performance at 1.5psi

- WIWNU% (3σ) = 5.5% @ 4mm EE

- Best Barrier performance at 1.5 psi

WIWNU% (3σ) = 2.9% @ 2mm EE

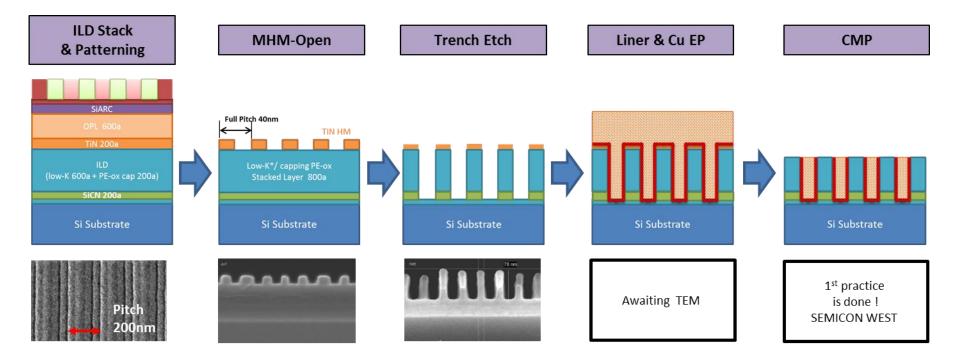

# **SUNY**<sup>POLYTECHNIC</sup> M1 Cu Damascene Module

**G450C** Integration leading BEOL M1 Module Development

Best Cu and barrier CMP processes performed on program tool GTC01

# **SUNY**<sup>POLYTECHNIC</sup> M1 Cu Damascene Module

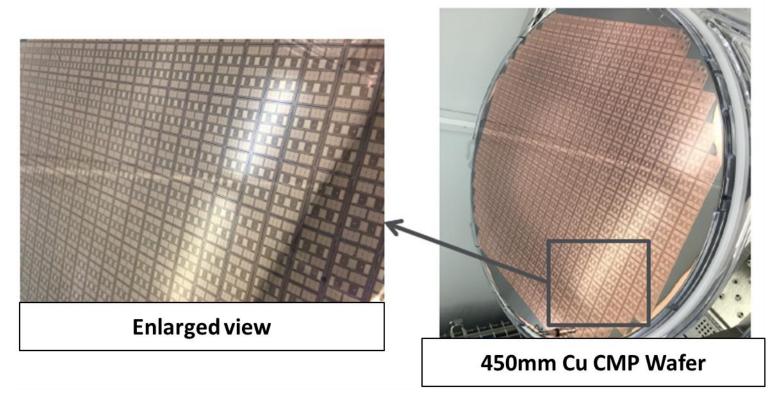

#### M1 CMP Complete

- □ First wafer in the world through M1 Cu Damascene CMP

- G450C test mask; smallest feature 20nm Cu line and space

- The first of two 450mm CMP tools is installed in the CNSE G450C Cleanroom

- Oxide and Cu demonstrations at supplier sites show excellent initial results

- The world's first Cu M1 BEOL 450mm wafer has been generated through G450C – Albany and supplier site equipment, including 450mm Cu / Barrier CMP

- G450C Albany in-house lithography ready for module wafer builds 3Q'15

## SUNY Poly SEMATECH and SUNY POLY CNSE

- Jakub Nalaskowski, Dinesh Penigalapati, Edward Barth, Frank Tolic, Kevin Petrarca, Alexey Vert, Saikumar Vivekanand, Harlan Stamper, Martin Rodgers, Stephen Bennett, Tricia Burroughs, Matt Smalley, Brett Baker-O'Neal, S. "Pops" Papa Rao, Frank Goodwin, Brian Sapp, Christopher Borst

- For more information, please contact "Pops" Papa Rao at <u>Satyavolu.PapaRao@sematech.org</u>.