CMPUG 5/15/2013

Accelerating the next technology revolution

# High mobility channel materials: CMP challenges and opportunities

R. J. W. Hill, I. Ali C. Hobbs P.D. Kirsch – SEMATECH G. Whitener, B. Ward, B. Fortino – Cabot.

Copyright ©2012

SEMATECH, Inc. SEMATECH, and the SEMATECH logo are registered servicemarks of SEMATECH, Inc. International SEMATECH Manufacturing Initiative, ISMI, Advanced Materials Research Center and AMRC are servicemarks of SEMATECH, Inc. All other servicemarks and trademarks are the property of their respective owners.

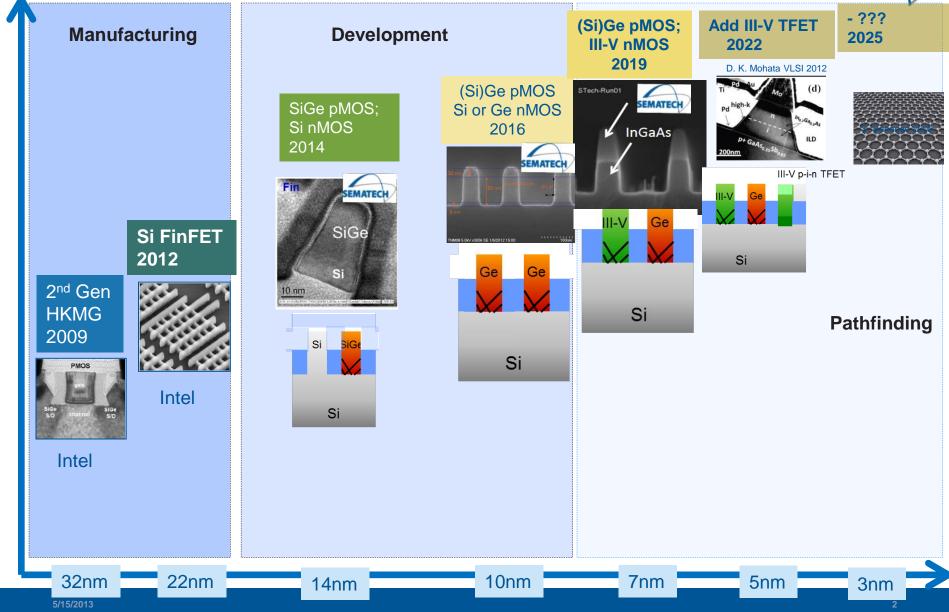

### Possible Logic Technology Roadmap

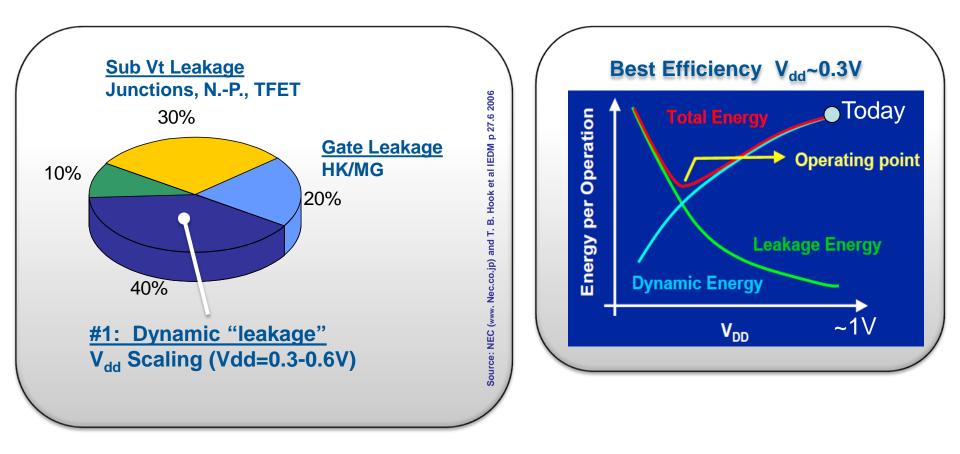

#### How To Address "Must Solve" Power Issue? Pareto Analysis of Power Issue

- Significance: Scaling Supply Voltage is Key to Address Power Issue

- High mobility channel materials enable V<sub>dd</sub> scaling w/o sacrificing performance

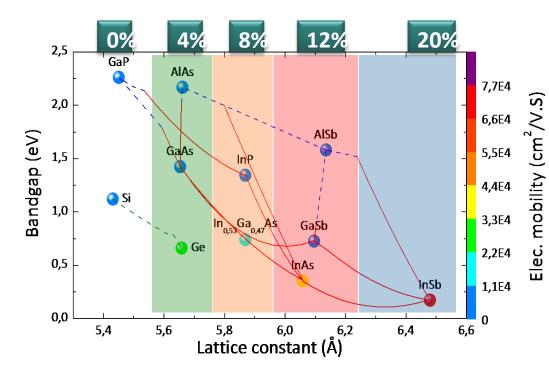

### High-µ on Si Heterointegration challenges

Lattice/thermal mismatch

High mobility ↔ Large lattice

parameter

SEMATECH

Lattice mismatch: InP/Si: 8% InP/Ge: 3.7% Mismatch stress relaxation leads to defects: dislocations, twins, SFs,...

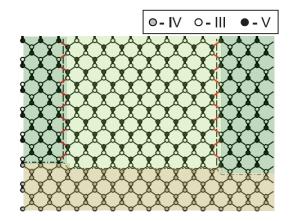

#### 2) Compound Semiconductors -Polar on non-polar:

Anti Phase domains and their Boundaries (APB)

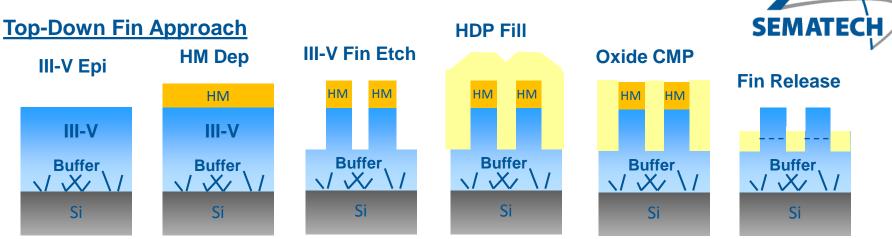

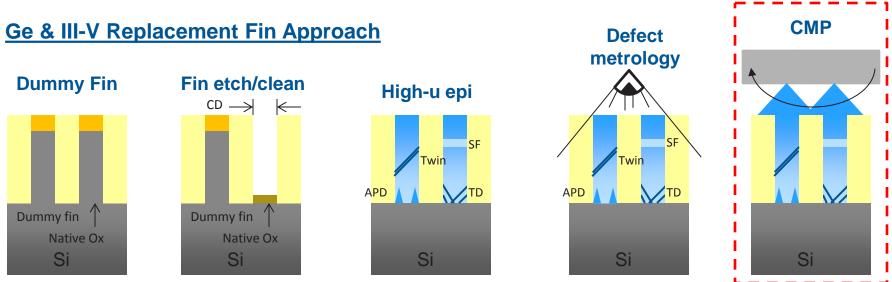

# High-µ Fin Formation Options

HVM'ability debatable, but good research technology to answer fundamental questions and develop modules

Elegant integration, but epitaxy challenging. Is high quality ~10nm fin possible?

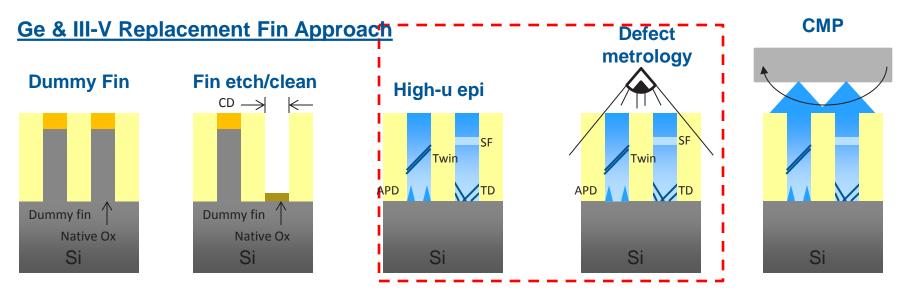

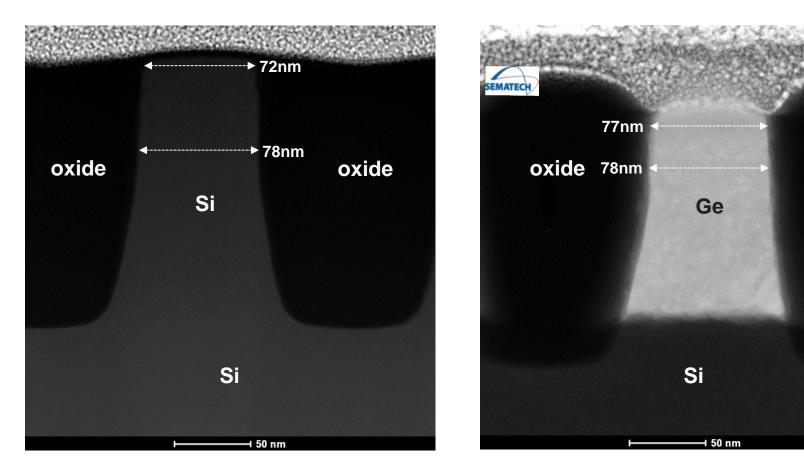

#### **Replacement Ge Fin** *Effective dislocation trapping demonstrated*

oxide

#### • Significance: Quality Ge epi techniques may be needed for non-Si CMOS

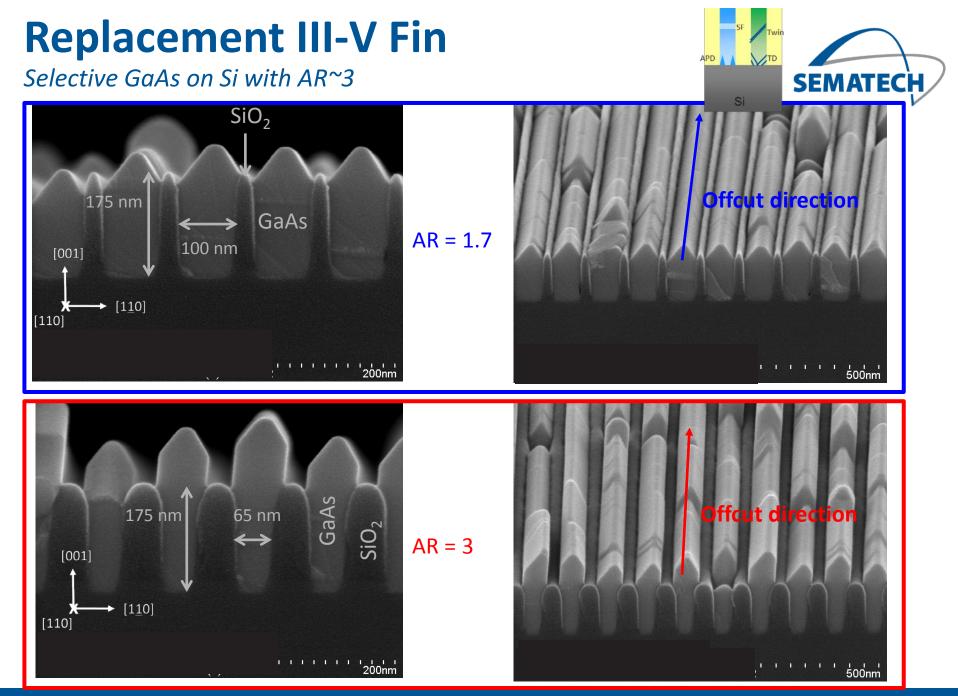

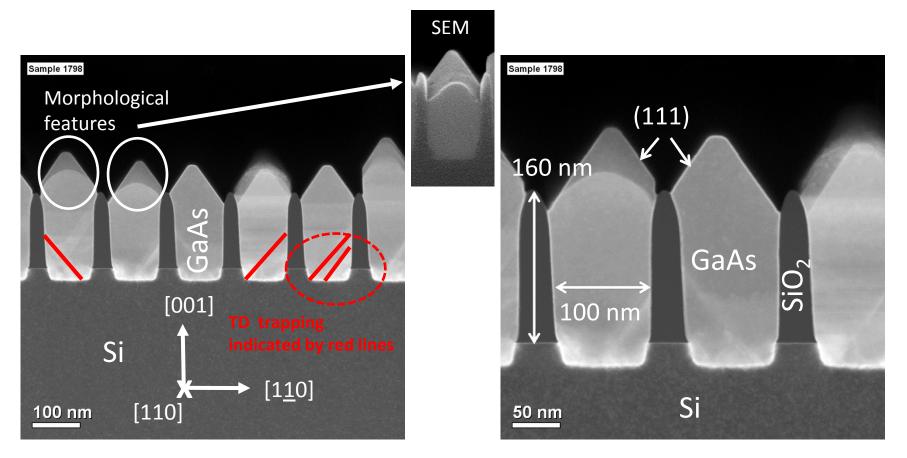

**Replacement III-V Fin**

Effective dislocation trapping demonstrated

- Trapping of *all* threading dislocations

- However, the ART structure promotes the formation of other structural defects (morphology and stacking faults)

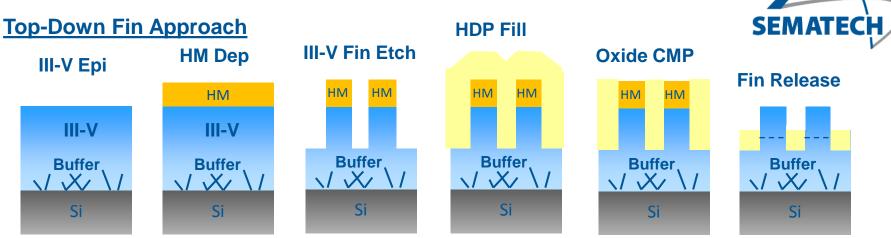

# High-µ Fin Formation Options

HVM'ability debatable, but good research technology to answer fundamental questions and develop modules

Elegant integration, but epitaxy challenging. Is high quality ~10nm fin possible?

#### 5/15/2013

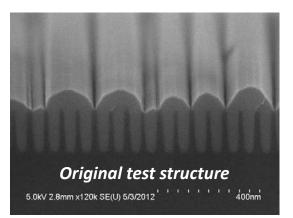

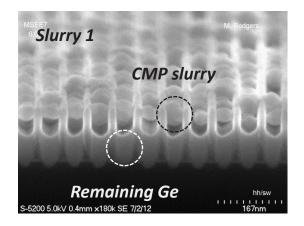

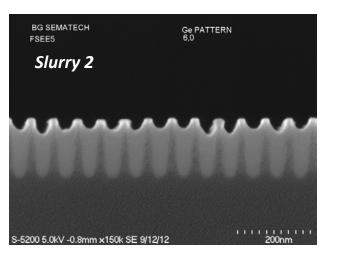

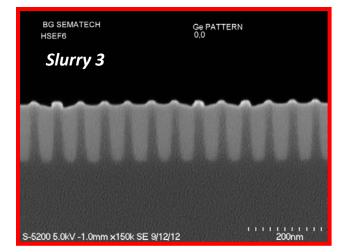

### **Replacement Ge Fin CMP**

#### Ge CMP initial development

- Ge is an 'easy' material to CMP, many slurries are effective.

- Ge/oxide selectivity important for smooth and uniform post CMP morphology

# InGaAs blanket wafer CMP

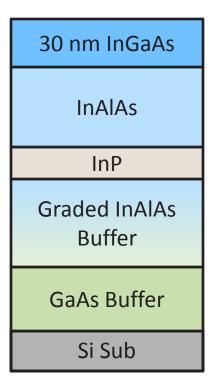

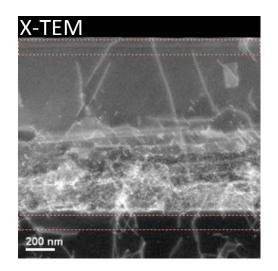

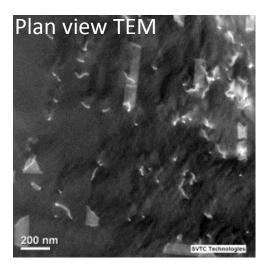

#### Starting layer structure

#### **Representative TEM**

Defectivity ~e9 cm<sup>-2</sup> 'mechanical' wafers for CMP study

- Planar InGaAs hetero-structure: initial CMP learning vehicle

- Next slides will show the results of this test structure

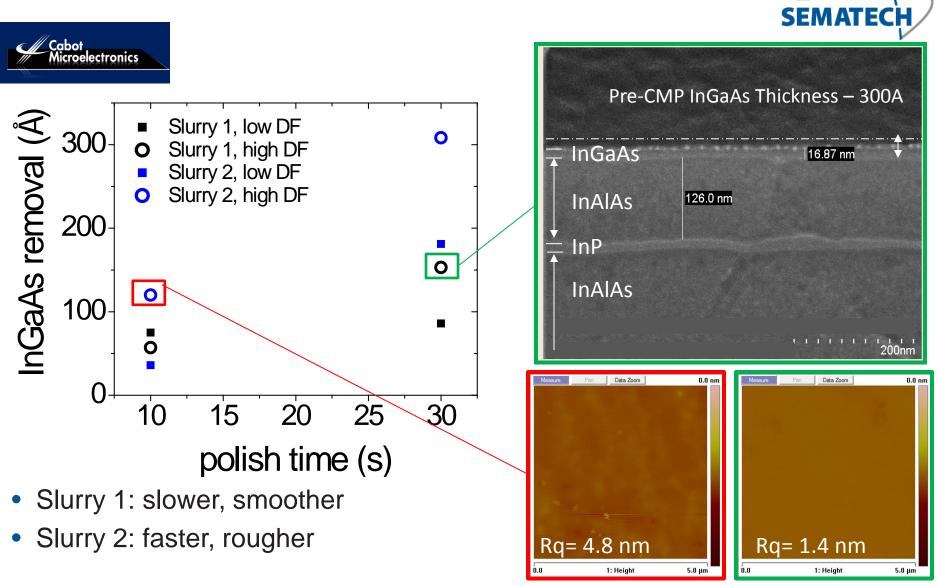

#### InGaAs CMP: polish rate and morphology

#### Controllability and morphology critical for replacement fin application

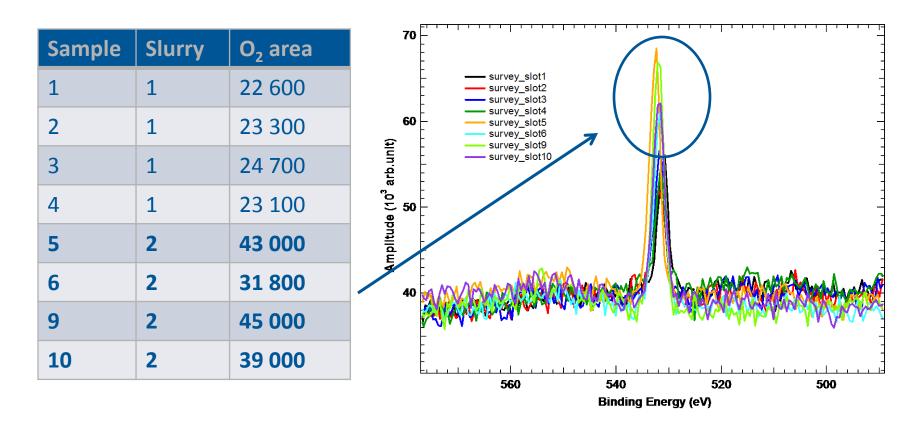

# InGaAs CMP: Controlling native oxide

- Oxide formation controlled by slurry 1

- Significance: surface roughness, stoichiometry and uniformity essential for successful RPL fin integration

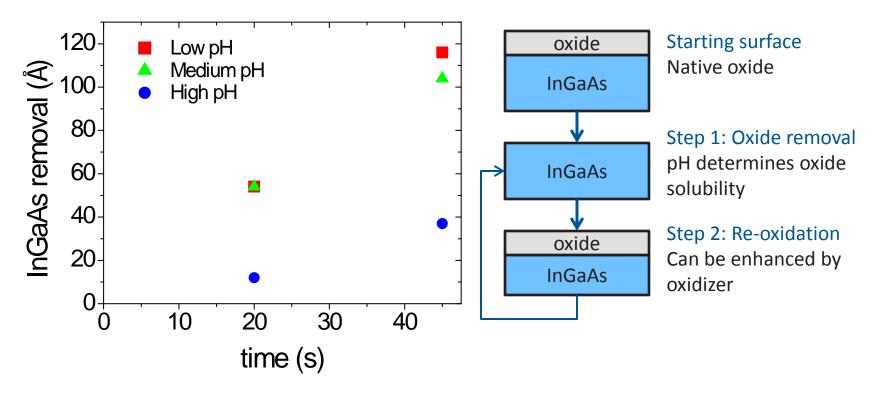

#### Working theory: 2 step mechanism

- Low pH increases oxide solubility and CMP rate.

- AsH<sub>3</sub> generation concern if pH too low

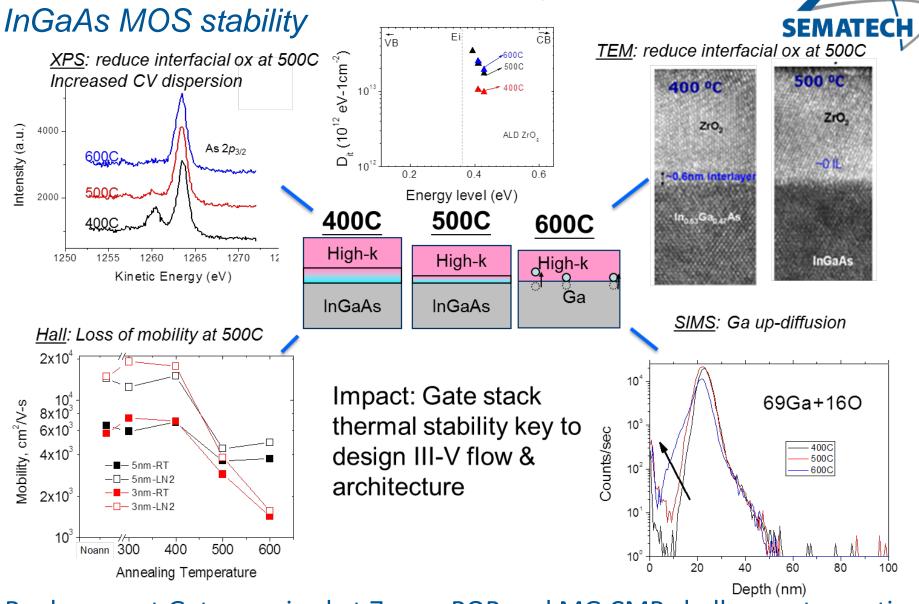

# Importance of Low Thermal Budget

Replacement Gate required at 7nm – POP and MG CMP challenges to continue

### Importance of Low Thermal Budget Short loop verification of gate-last approach

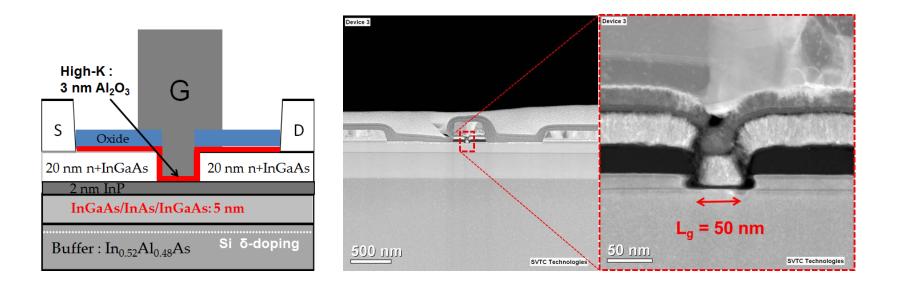

#### Coupon test structure using non-VLSI process flow:

- Fundamental scalability of III-V materials

- Module level learning

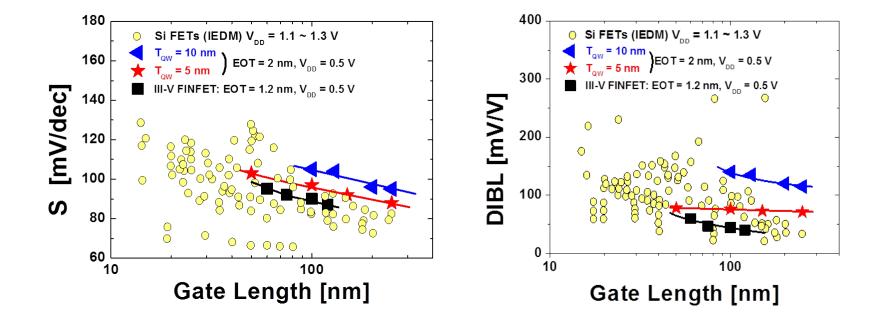

### Fundamental Promise of III-V Gate last process enables SCE control to Lg=50 nm

Low temperature gate-last process flow preserves gate-stack integrity - Replacement gate required at 7nm node

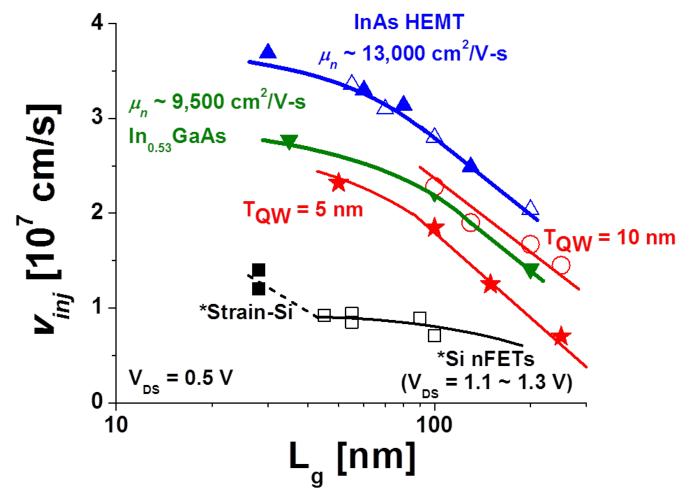

Fundamental Promise of III-V Benchmarking: Injection Velocity (Vinj)

- Excellent scalability was observed with ETB InAs MOSFET down to  $L_q = 50$  nm.

- 2X higher injection velocity vs. s-Si device at  $\frac{1}{2}$  V<sub>CC</sub>

- High mobility channel materials expected at 10/7nm technology node.

- Replacement fin, elegant integration, but epi and CMP challenges to overcome.

- Initial Ge and III-V CMP results promising, more work to do....

- III-V gate-stack, thermal budget critical: gate last flow likely, CMP critical.