# The History & Future of CMP

CMPUG July 2008 Karey Holland, Ph.D. kholland@nexplanar.com

Ken Cadien, Ph.D. University of Alberta kcadien@ualberta.ca

# Outline

- History 1984-2008

- Challenges and solutions: slurries and pads

- Next 10 years

- Very long Term

- Conclusions

# History circa 1984

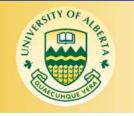

The semiconductor industry thought that scaling was done at the 1.0 mm dimension due to topography

# History 1984

Boy, did <u>I</u> get it wrong ...

"Karey Holland remembers her reaction one day in 1984 when a colleague, Bill Cote, at IBM recommended that she use what seemed for all the world like a scrub pad and a scouring liquid for one of the critical steps in processing the silicon wafers that contained the next-generation memory chips

"The idea of exposing the wafer surface to billions of abrasive particles did not sit well with her. 'You're not going to put that dirt on my wafer', she protested".

So my "punishment": spend my career make this process better and better.

February 1998 Scientific American Magazine008CMPUG 2008

July 16, 2008

## Interconnect Technology

Process, Application, Equipment, & Sum Evolve, but not as much on Pads 4-11 Cu Layers 90 nm 3-9 Cu Layers, PMD, W, STI OrganoSilicate Glass (OSG) 130 nm 3-6 Cu Layers, PMD, W, STI STI, 6 Al Metal layers

STI, Five Al metal layers, SiOF

Four Al metal layers, W polish, PSG

500 nm ILD planarization, W plugs w etch back

1000 nm Two Al Metal layers, BPSG

**CMPUG 2008**

CMP **Applications**

65 nm

PMD, W, STI, OSG

**Oxide Polish Pre-Metal Dielectric** Interlevel Dielectric STI Polish **Poly Polish Tungsten Polish Copper Polish Barrier Polish** High k Gate 5

# **CMP's Attributes**

- CMP improved product yields

- Removes defects

- CMP improved wiring integrity and resistivity

- CMP reduced electromigration (e.g., versus post W etchback surface roughness)

- CMP enabled high NA optical lithography

- CMP enabled novel integration schemes

- Cu damascene technology

- Enabled upstream modules

- CVD

- EP

# The Future The next 10 years

More fab-supplier collaborations ? More slurry-pad-equipment supplier collaborations? Can the industry support > 25 slurry suppliers and > 20 pad suppliers?

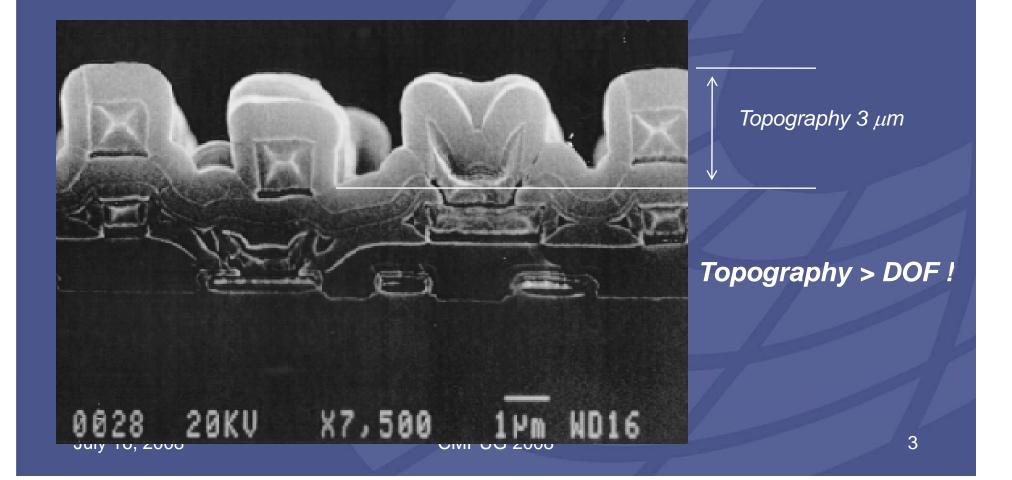

## Challenges for the IC Industry The next 10 years

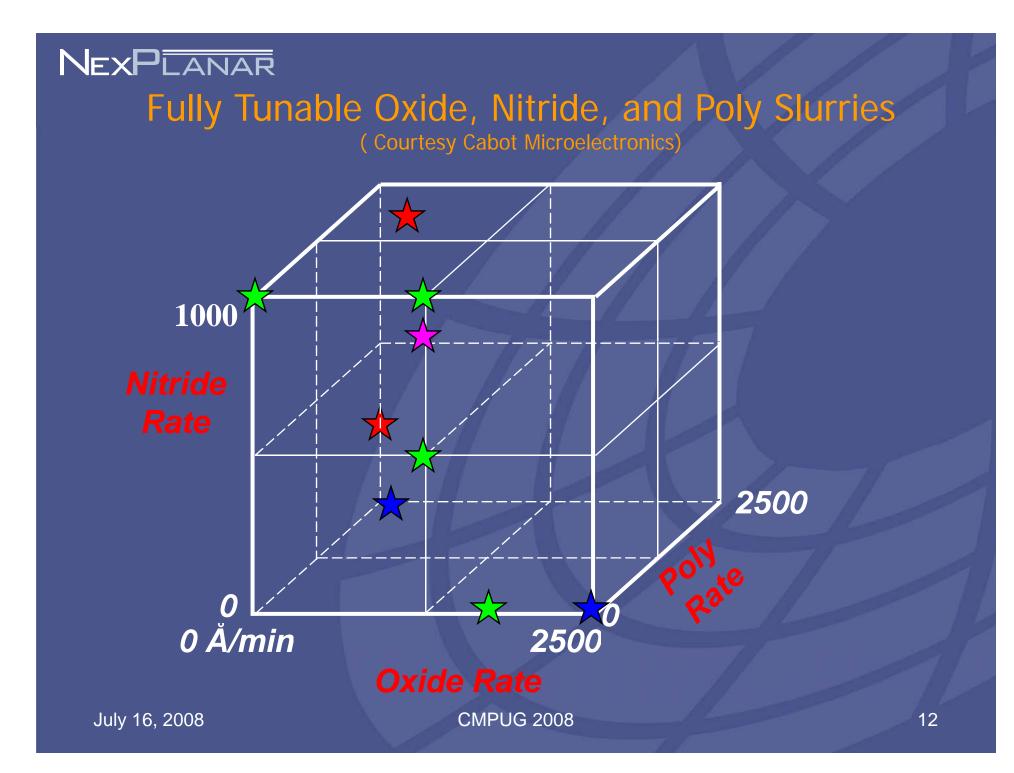

- More tunability for STI, W, copper barrier

- Improving copper dishing, erosion, defects ... multiplied by many more metal layers

- Low Stress Polish ... Integrating ultra low k dielectrics

- Polishing novel materials (high k gates, new barriers)

- Reduced edge exclusion (1.5 mm?)

- Cost for each wafer pass

- Slurry use per wafer

- Wafers per pad

- Tool utilization

## NexPLANAR

# Slurries

## NexPlanar Semicond

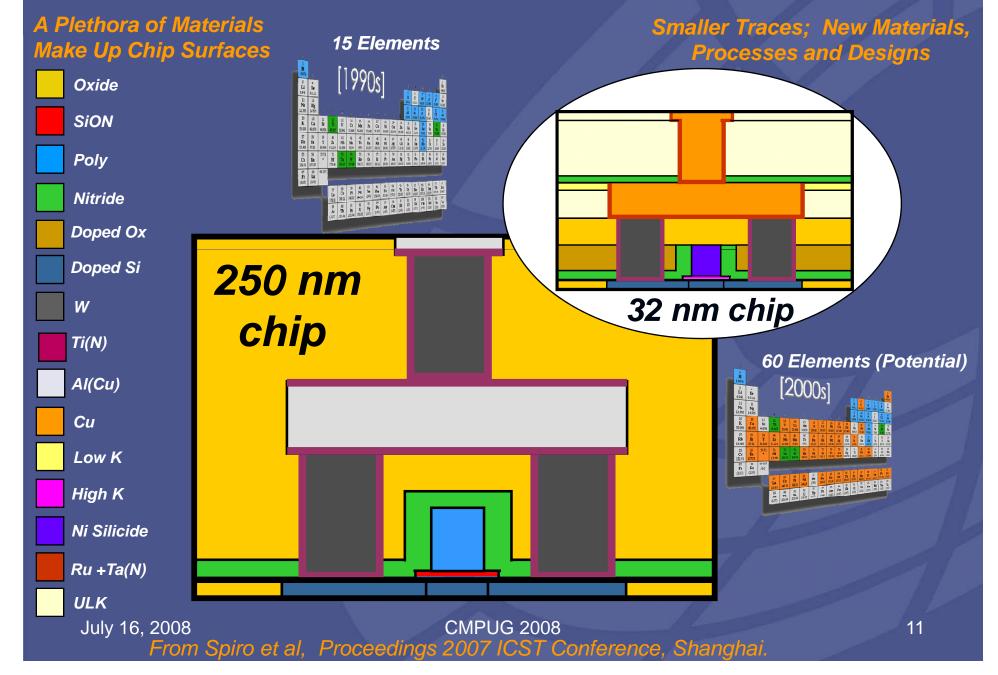

## Semiconductors Have Changed

# Pads

# CMP Pad Challenges

- Most New Suppliers Focus on Alternative Ways to Make Equivalent to Industry Standard Planarization Pads

- "Match" with Some Improvement Over Industry Standard

- Me too RR and NU, 20% longer pad life

- Next Level Planarization Technology is Needed

- Tuned for the CMP Process Application Performance Needs

- Much Lower Defects

- Low Stress CMP

- 1.5mm Edge Exclusion

## NexPLANAR

# Innovative Pad Design Leading Next Level Planarization

- Solo pad technology w/ soft & hard segments in the polymer matrix:

- Improved planarity within die and within wafer

- Improved non-uniformity and low edge exclusion

- 7 to 10x microscratches and lower defects

- Competitive material polish rates

- Pad technology designed w/ "tunability" feature for each application:

- Provides a novel key process parameter to improve CMP process performance for current and advanced technologies

- Differentiated Pad Manufacturing Concept: Compression molded

- In-situ pad grooves ensure uniform, high integrity profiles and provide better slurry distribution and efficiency

- Enables significant batch-to-batch process control

- Lower CoO:

- Material cross-linking: lower wear rates and >2X extended pad life

- Reduced slurry usage (20-30% reduction)

- Better tool utilization

July 16, 2008

**CMPUG 2008**

NexPlanar, Ra ~ 2.35um

Grooves

## **Defects & Microscratches**

| Wafer | Process, all cells<br>NexPlanar Pad | Defect<br>Counts |

|-------|-------------------------------------|------------------|

| 1     | A5 3300A/min                        | 24               |

| 2     | A5 3300 A/min                       | 21               |

| 3     | A7 4400 A/min                       | 33               |

| 4     | A7 4400 A/min                       | 15               |

| 5     | Low Slurry Flow<br>3300Amin         | 7                |

| 6     | Low Slurry Flow<br>3300Amin         | 6                |

| 7     | Low Slurry Flow<br>3300Amin         | 11               |

| 8     | Low Slurry Flow<br>3300Amin         | 13               |

Combination of formulary lubricant and grooving reduces microscratching and post-clean defectivity

Average particle count is

< 35 particles for a series of four different processes after BOE Etch

Compared to ~200-800

for Standard Pad and

another competitor ...

Extraordinarily Good

Pad Performance

Post Polish, Post BOE Particle Data CMPUG 2008

July 16, 2008

# Very long term circa 2030

July 16, 2008

**CMPUG 2008**

# There is definitely an inflection point occurring in the next 20 years

# Both transistors and interconnects face fundamental change

# Si Technology: Complexity Increasing Rapidly for transistors & interconnects

**11 Elements**

#### +4 Elements

1 H 1.0079

3 Li 6941 Be 9.0122

11 Na 22.990

19

39.098

57 Rb

85.468 55 Cs 131.91 56 Ba

Fr (223) Mg 24305

Čà K

St

88 Ra (116) \$7

21 Sc 44956

39 Y

89-103

Ac

21

71 H

ő

Ci Ma RRA

45 Te (H)

H Ra -

前 Np (印) 死 U 151.05 91 Pa 25114 90 Th 252.04 89 AC (117)

0

ĉ

94 X X 8 Pi An Ca Bi (24) (40) (40) (10)

## +45 Elements (Potential) [2000s]

a

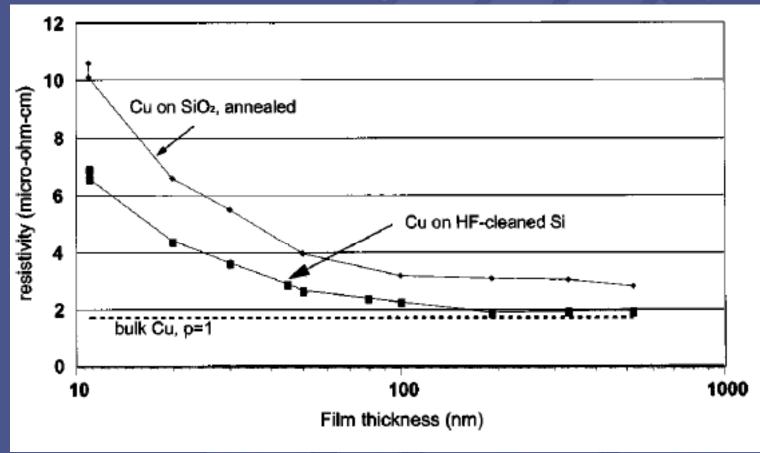

# NexPLANAR Cu interconnect scaling is an issue long term

S. M. Rossnagel and T. S. Kuan, "Alteration of Cu conductivity in the size effect regime", J. Vac. Sci. Technol. B 22.1., Jan-Feb 2004

July 16, 2008

**CMPUG 2008**

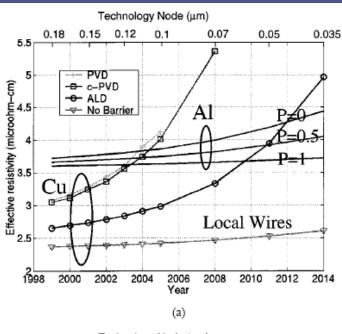

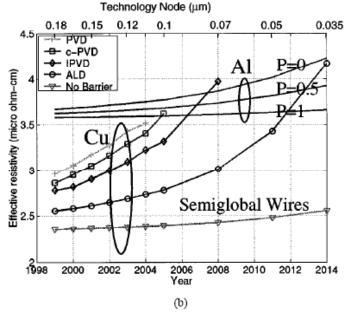

Future Cu and A1 resistivity trend for different barrier technologies. For Cu, P = 0.5, BT = 10 nm, temp. = 100 °C. (a) Local wires and (b) semiglobal wires.

# Could AI replace Cu?

# *Timing depends on barrier thickness, resistivity*

P. Kapur, J. P. McVittie, and K. C. Saraswat, "Technology and Reliability Constrained Future Copper Interconnects—Part I: Resistance Modeling", IEEE Trans. On Electron Devices, <u>49</u>, (2002) 590-597

**CMPUG 2008**

## NexPLANAR Interconnect Scaling & Future Options

1000 nm Two Al Metal layers, BPSG

500 nm ILD planarization, W plugs w etch back

350 nm Four Al metal layers, W polish, PSG?

250 nm Five Al metal layers, SiOF

180 nm Six Al Metal layers

130 nm Six Cu Layer CMPUG 2008 -----

CNT

## Options Optical,

After several generations of scaling

65 nm Eight Cu Layer

90 nm Seven Cu Layer

July 16, 2008

# What does all of this mean for CMP?

## • Hard to predict

- Depends on integration scheme

- CMP's attributes will be relevant

- CMP does improve yield so whatever the scheme this may be useful

- Scattering in interconnects is due partially to the roughness of the interconnect...CMP does smooth...Cu and optical

- There is some hope that CMP will be around in 2030

# Summary

#### Continuous improvement Pad & slurry tunability New materials

Next 10+ years

Depends on design, <u>architecture,</u> etc

Transition/paradigm Shift in 10-20 years What's next? 3D then optical?

2030 and beyond

July 16, 2008

**CMPUG 2008**

# Conclusions

- For the next decade or more

CMP will need to do continuous improvement

Improved defects, dishing, erosion, and cost

Novel pads with more tunability to enable the above

Increased tunability for slurries

New slurries and pads for new materials

Looking out to the long term

CMP will have a role to play

- Thank You!