## **TSV-3D Integration**

Ismail Emesh, Dir. of R&D ASM CIS

Thursday, January 03, 2008

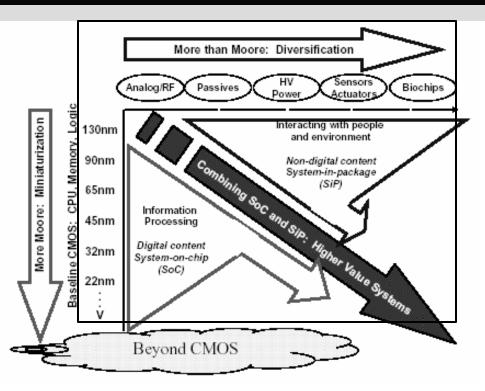

#### Three Technology Domains

- More Moore: Moore's law –Devices may reach physical limitations

- Beyond CMOS Disruptive technologies such as Carbon nanotubes, molecular electronics

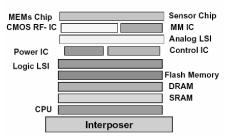

- More than Moore Integration of technologies that do not Scale

- SoC offers low cost per function

- SiP offers single package modular platform

- Total System Solutions by Heterogeneous 3D Integration

After ITRS 2005

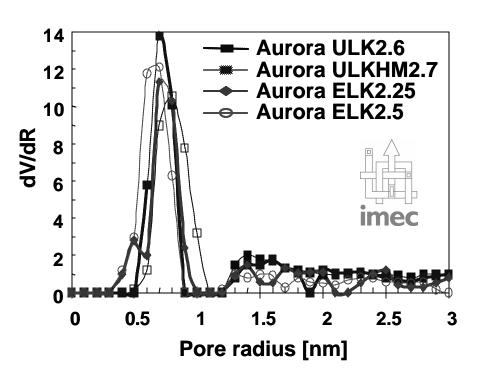

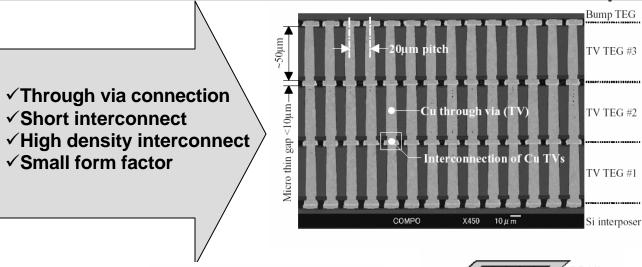

Interconnect: 3D Integration or several

- Porous low-k or airgaps

- 10-15% lower k<sub>eff</sub>/generation

- > More Copper

- Thinner barriers

- Specular e<sup>-</sup> reflection at Cu/barrier interface

- Shorter global interconnect by 3D die or wafer stacking

- Equivalent to several generations of Low-k

- Replace global interconnect by optical, wireless links

- Hetero-integration

- Long loop wires

- Overhang

- Limited # of Wires

- Interposer

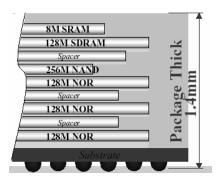

**Heterogeneous Integrated System**

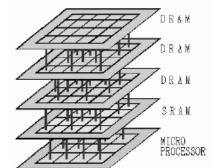

3D computer Chip

- Higher density

- Higher speed

- Lower power

- Lower cost?

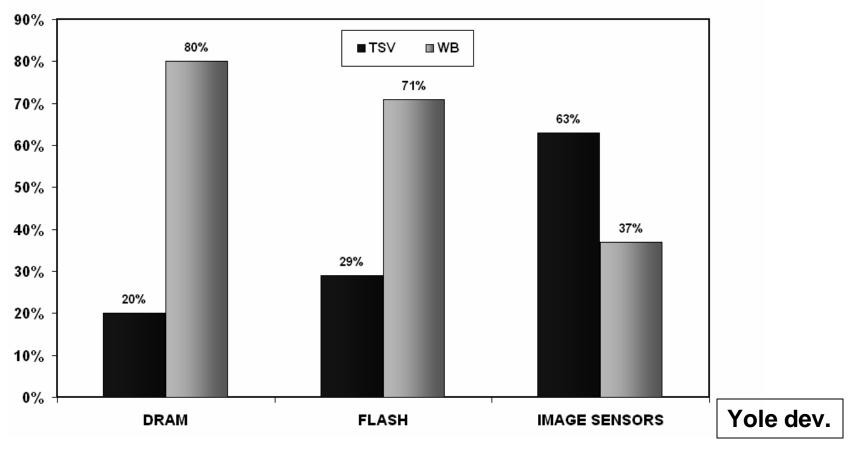

- ➤ 3D integration will be used for products that require high performance until cost parity with the incumbent technology (WB) is achieved

- Many factors need to be used in any cost model which makes calculation and prediction are biased by the source

- Handheld/consumer electronics will certainly drive the technology

- Data market will utilize the technology for the DDRx products

- > 3D will have little penetration into the embedded market

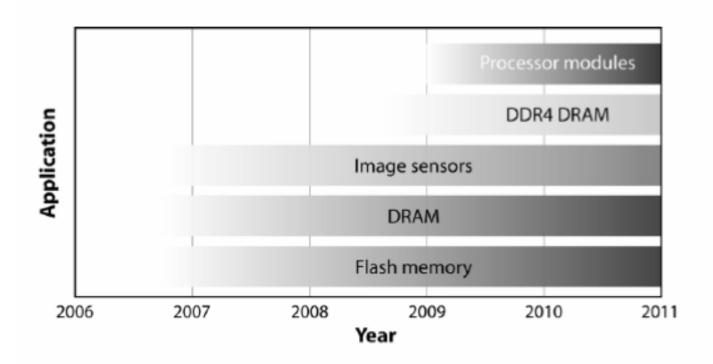

# 3D TSV Roadmap-Memory and Image Sensors are

Front-End Op

Source: TechSearch International, Inc.

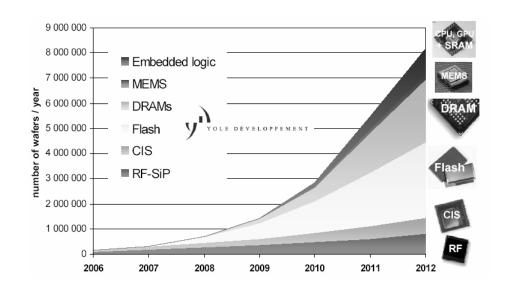

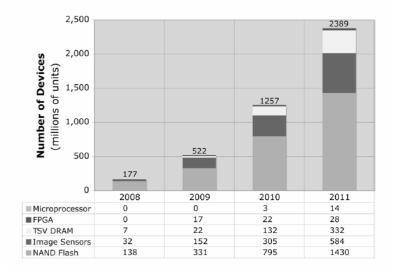

#### 3D TSV Market Forecast (millions of units)

- **➤ Discrepancy in market forecasts:**

- TechSearch International forecast is 2.5X larger than Yole Development's forecast

- > Equipment sector needs accurate forecast for strategic fund allocation

> Packaging technologies will coexist-will be applications driven

- > Via formation

- >Insulator liner

- > Barrier

- > Conductor

- ➤ Wafer thinning

- > Bonding

- > Dicing

D2W approach

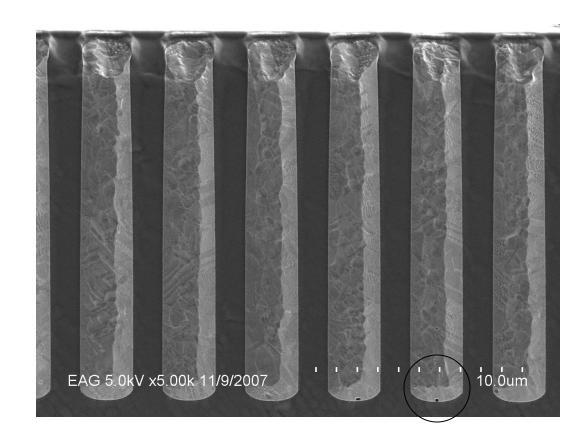

- Plasma etch

- SF<sub>6</sub> and C<sub>4</sub>F<sub>8</sub> for passivation

- Anisotropic etch

- Must eliminate scalloping

- Laser ablation

- > Liner

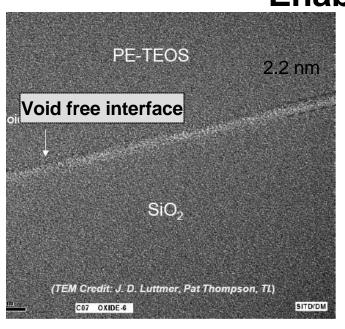

- PECVD of TEOS based SiO<sub>2</sub> film

- ALD SiO<sub>2</sub>

- Barrier conductor

- PVD Ta/TaN, TiN

- ALD Ru, WNC

- > Seed

- PVD Cu, CVD Cu, ALD Ru

- Metal conductor

- CVD tungsten

- Polysilicon (heavy doped)

- ECD copper

Lam Research

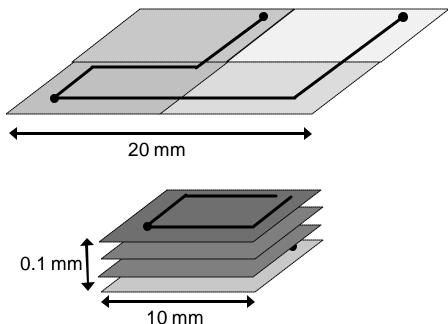

- > Primary thinning: Lapping or grinding to 50 mm thick

- > Secondary thinning: plasma etch, wet etch, and CMP to thin the wafer to 20-30 mm

- Dicing

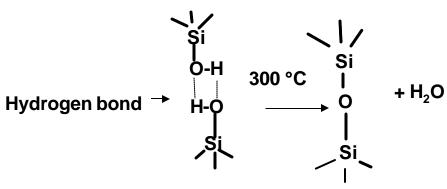

# Enabling Process: Randing - Low Tamp.

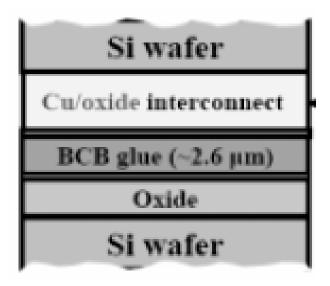

- Condition Enabling process: Polymer Bonding-BCB

Spin-on at room temp.

- Pre-cured at 125°C

- Align

- Final cure at> 250°C for 1 hour in vacuum

### **Enabling process: Polymer Bonding-BCB**

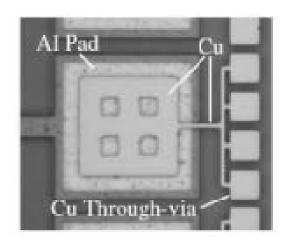

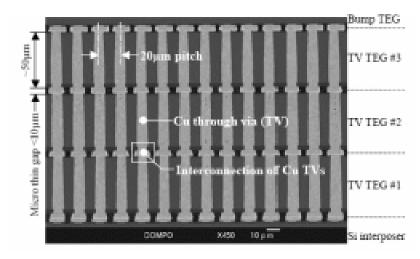

- Cu-Cu bonding of thin die (Cu nails) to landing Cu wafer

- Improve mechanical properties by introducing dielectric (BCB)

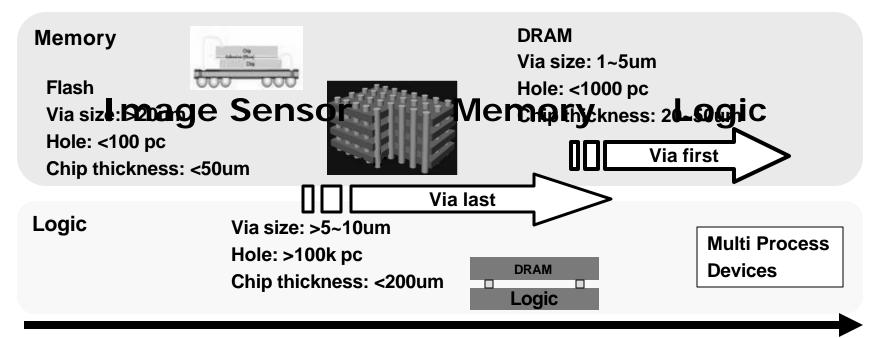

# Different Integration Scheme

# Various schemes involving TSV and interconnect fabrications

- Wafer Designed for 3D

- Post front-end of line (transistor formation)

- Vias fabricated before interconnect

- Post backend of line

- Vias fabricated after interconnect

- Via first (prior to thinning)

- Via last (after thinning and after attachment to holder)

- Wafer not designed for 3D

- Vias are formed next to pads and in the dicing streets

### Post Front-end Approach

Vias are fabricated after <u>transistors fabrication-</u> <u>ZyCube integration</u>

(a) Si deep trench etching

(b) Filling with Poly-Si

- 2.5 mmx55 mm vias filled with doped poly silicon

- 5 mm In/Au micro-bumps

# Post Backend Integration-Via Last

Front-End Operations

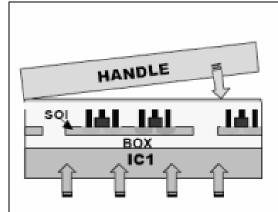

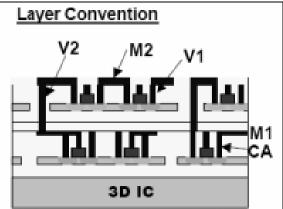

➤ Fabrication of interconnect is similar to those shown in the previous slides. Vias are fabricated after thinning and attachment- <a href="#">IBM integration</a>

- Process IC1 up to contact via level

- Secure IC1 to handle wafer

- Remove some/all of original substrate

- Process IC2 up to first metal + planarized ILD

- Align & bond IC1 to IC2 (fusion, polymer bond)

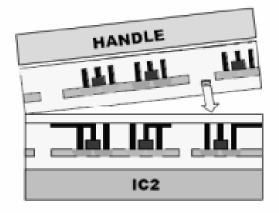

- Remove handle wafer & adhesives

- RIE interlayer via (V2)

& M2

- Cu plate to fill vias & metal, CMP

- Commercially available wafers

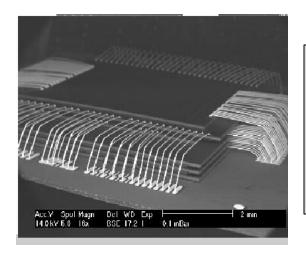

- Vias fabricated at the periphery of the chip

- Chip to chip bonding using gold bumps or Cu-Sn eutectic

#### **CMOS Image Sensor (CIS)**

Via size: 200um Hole: <100 pc

Chip thickness: 200um

#### Size Shrink for mobile

2005 2006 2007 2008 2009 2010 2011 2012 2013 2014

Image Sensor Memory Logic

Yole dev.

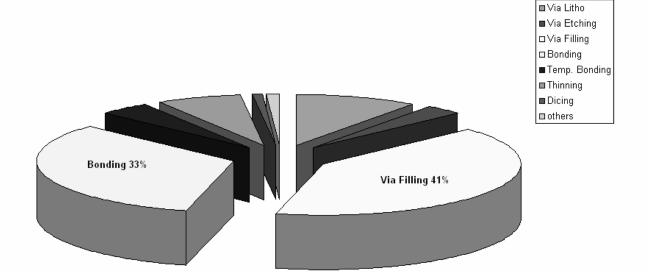

➤ Via filling and Bonding are the most expensive processes steps

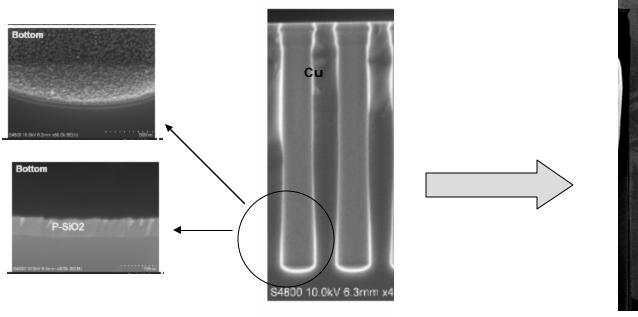

- >PECVD SiO<sub>2</sub>(40nm) -ASM

- >ALD TaNC (5nm)-ASM

- >ALD Ru (5nm) (Adhesion layer)-ASM

- >CVD Cu seed (50nm)-ASM

- >ECD Cu-ASM

➤ Vertical furnace, Pulsed CVD TiN (excellent SC- high dep. Temp.)-

>ALD TaCN (excellent SC & low dep. temp.)-

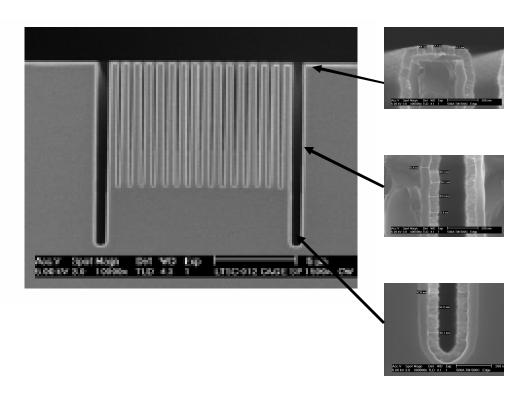

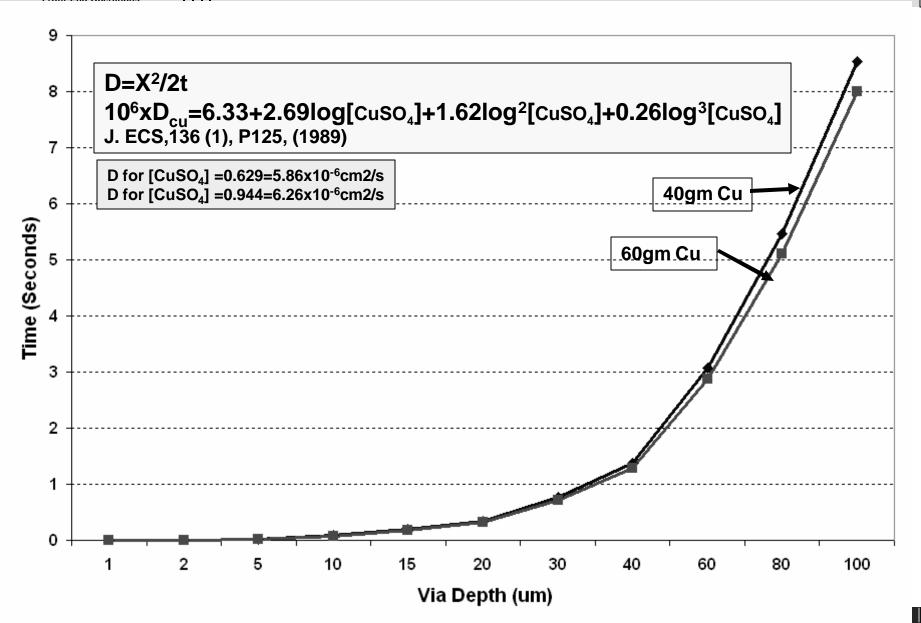

- > Larger vias are slower to fill than small vias

- ➤ Elimination of mass transport of Cu ions into vias is a must for void free filling –fundamental limitation

- Low current density (low rate and low throughput)

- Increase bath temp. (destroy the additive in the bath)-AE=4.6 kCal/mol

- Increase Cu ion conc. (solubility limited 60 g/l in acids)

### Impact of Via Depth on Diffusion of Cu ions int

## > Polish sample with various diamond lapping film

- Simple and affordable

- Fast

- Cu smear-unable to identify small voids

- > FIB/SEM is slow and costly

- Need different technique to characterize the plating of deep vias

- XRD (used for metallurgical research-packaging)

- Insensitive to small voids

- > Faster than FIB-less costly

- > Promising technique

### Thanks For Your Attention

INNOVATION

WILL BE DEFINED

BY

THE LIMITS

OF

OUR IMAGANATION

<u>Acknowledgment</u>: Many thanks to Hessel Sprey, Ivo Raaijmakers, Ayse Durmus and Brent Basham for their contribution