# Gas/Vapor Phase Epi (VPE), Liquid Phase Epi (LPE) & Solid Phase Epi (SPE) Doping Methods In Si, SiGe & Ge: A Historical Review

John Ogawa Borland J.O.B. Technologies, Aiea, Hawaii, USA 25th Anniversary of IWJT June 4, 2025

With IEDM-2025 Updates

Evolution of CMOS S/D Stressor Technology from Planar to 3-D Stacked Devices

John Ogawa Borland J.O.B. Technologies, Aiea, Hawaii, USA E-mail: JohnOBorland@aol.com

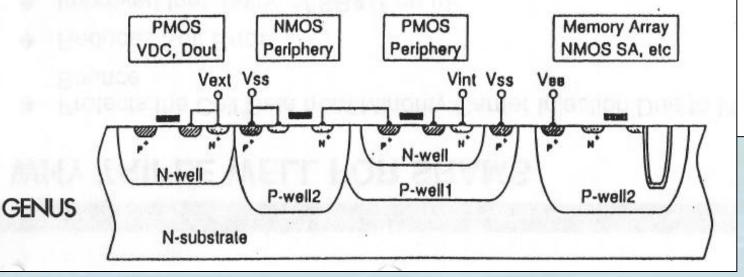

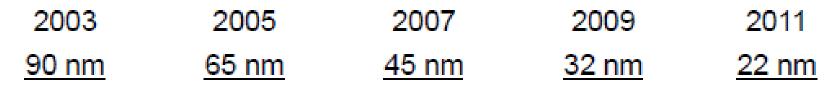

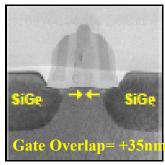

Today, use of Selective Epitaxial Growth (SEG) for CMOS Source Drain (S/D) stressor and Wrap Around Contacts (WAC) is standard FEOL processing for 3nm node FinFET and 2nm node Nanosheet devices. With improved contact resistance engineering, the SEG S/D structure is expected to continue to be used for 3-D stacked C-FET through at least the A3 technology node in 2034 as illustrated in Fig.1 [1]. This all started back in the 1980s when US and Japanese researchers investigated the use of SEG for elevated S/D and S/D contact filling. This talk will review the evolution of SEG S/D technology including the key recess etch p+ SiGe S/D structure for ultra shallow junction reported in the 1990s. This led to the production introduction of recess etched embedded-SiGe (eSiGe) PMOS S/D stressor to boost p-channel mobility by Intel at the 90nm node. However, the NMOS S/D stressor evolved from amorphous implantation at the 65nm node to eSiC SEG S/D stressor at 14/16nm 3-D FinFET. For one generation, the 32nm node, IBM/AMD/Samsung used PMOS channel-SiGe and NMOS eSiC S/D was used for IBM 22nm PD-SOI.

#### A Historical Review of **Selective Epitaxial Growth**

From 1962 to Present

By John Ogawa Borland

elective epitaxial growth (SEG) is one of the key front end-of-line (FEOL) process technologies today that has been used in CMOS device manufacturing for 20 years. Intel introduced

Digital Object Identifier 10.1109/MED 2023 3330741 Date of current version: 1 February 2024

the use of SEG in the 90-nm node planar CMOS for the pMOS sources/drain (S/D) stressor back in 2003. It combined elevated S/D technology with recess etching S/D junction formation and silicon germanium (SiGe) for local channel strain. However, the first reported publication on SEG goes back 61 years to an article

reported by Joyce and Baldrey of Texas Instruments in Nature in 1962 [1].

In the 1980s there were over 120 publications on various research and develcalled selective silicon growth (SSG

(19) United States

JSAP Sep 19, 2024

IEEE Brings Energy Equity and Safety (Proactive "Loss of Life" Prevention) to Molokai Native Hawaiian Homesteaders

Helping Those Without Access to Grid Electricity and Low-Income Renters With Island Nano-Grid/Clusters

By John Borland, Takahiro Tanaka, Todd Yamashita, Lilliana Napoleon, and Bruce Yamashita

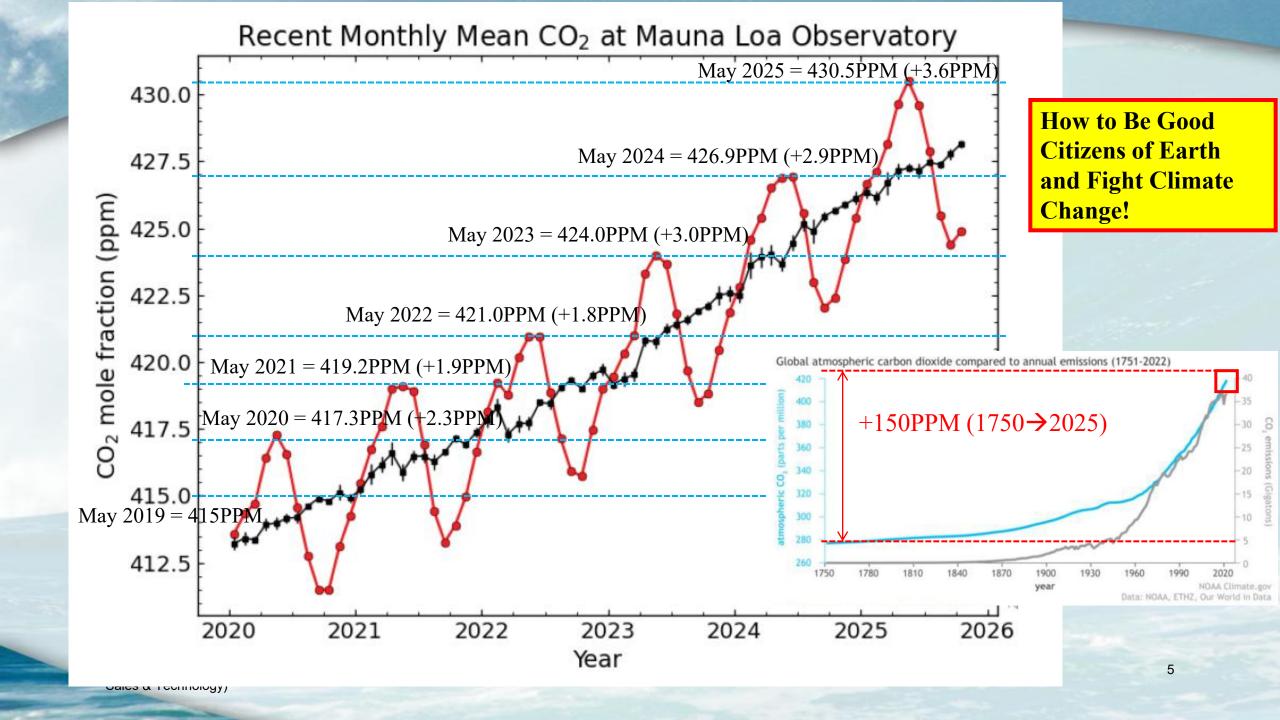

e atmospheric CO, levels on top of Mauna Loa observatory reached a record high of 426.9 ppm in May

requirements of a nuclear power plan

#### **How to Be Good Citizens of Earth and Fight Climate Change!**

uner data centers with the nower

Renewable Clean Energy Today" [4]. Using Hawaii as a case study example, lies benefiting from the 80-909

energy cost savings and energy but

IEEE EDS Magazine Dec 2023

IEEE EDS Magazine Sep 2024

# Photonic Interconnect for Next-Generation AI Systems

Benjamin G. Lee

NVIDIA, Santa Clara, CA, USA, email: benjlee@nvidia.com

Abstract—AI systems employ tightly integrated GPU clusters using low-cost high-reliability intra-cluster electrical signaling. Reach ultimately limits cluster size and aggravates thermal density. Efficient, low-cost, distance-insensitive off-chip communication can alleviate thermal challenges, increase cluster size, and simplify packaging. Photonics can help, but it must meet stringent efficiency, cost, and density targets.

interconnects, which offer extended reach, can release the pressure on localization, but they do not yet fit within the cost and power targets of today's scale-up networks.

At GTC 2025 [6], Jensen Huang announced plans for the next few generations of NVIDIA GPU systems. The Rubin Ultra NVL576 system, contained within a single 600-kW Kyber rack, is planned to comprise 576 Rubin Ultra GPU die

IEDM-2025 Paper 41.1

Elon's TN Data Center: 200K GPU = 250MWatts

$\rightarrow$  1M GPU = 1.2GW power

Blackwall = 1000Watts

72 GPUs per Rack = 120-130kWatts

Next Gen Rubin Rack = 600kW!

Nvidia A100 (400W)

Nvidia H100 (700W)

AMD MI100 (300W)

AMD MI200 (500W)

Intel Gaudi (300W)

Intel Gaudi 2 (400W)

fabrication partner. Historically, Nvidia's high-end AI chips like the H100 have sold for \$25,000 per unit, and Blackwell chips are expected to be priced even higher, potentially exceeding \$30,000 per unit, due to their superior performance and constrained supply.

#### Al Infrastructure:

The demand for AI infrastructure has been growing exponentially, with the global AI hardware market projected to reach \$400 billion by 2030. Nvidia is expected to maintain a 95% market share in AI GPUs, significantly contributing to this growth.

| Table 1 - Blackwell Chip Revenue and Al Hardware Market Forecast |        |        |        |  |  |

|------------------------------------------------------------------|--------|--------|--------|--|--|

|                                                                  | 2024   | 2025   | 2026   |  |  |

| Blackwell Units Shipped (in 1000s)                               | 100    | 400    | 500    |  |  |

| Average Price per Chip (\$)                                      | 30,000 | 32,000 | 33,000 |  |  |

| Projected Revenue (\$ Million)                                   | 3,000  | 12,800 | 16,500 |  |  |

| Source: The Information Network (www.theinformationnet.com)      |        |        |        |  |  |

J.O.B. Technologies (Strategic Marketing, Sales & Technology)

#### Nvidia Blackwell platform

- •1.4exaflops in a single rack

- •Over 1.5 miles of cable in the NVLink cable cartridge. Complete rack weighs 3000lbs

### Inside the small town where Elon Musk's supercomputers have left residents struggling to breathe

By LAUREN ACTON-TAYLOR FOR DAILYMAIL.COM

PUBLISHED: 01:19 EDT, 7 May 2025 | UPDATED: 03:47 EDT, 7 May 2025

Residents in Tennessee have been left struggling to breathe over Elon Musk's supercomputers as pollution is believed to have caused a surge in asthma.

Musk's artificial intelligence company set up shop in South Memphis last year but the supercomputer's pollution control measures don't meet federal guidance.

The area now leads the state in the most emergency room visits for asthma.

The company has no Clean Air Act permits, Politico reported, and none of the 35 methane gas turbines that help power xAl's supercomputer are equipped with federally-required pollution controls.

Musk's plant turbines spew an estimated 1,200 to 2,000 tons of nitrogen oxides, or NOx, further contributing to the smog issue in the area.

At the time, he said: 'We have generators on one side of the building, just trailer after trailer of generators until we can get the utility power to come back in.'

The turbines Musk has implemented are only temporary, but the damage they can do is immense, as xAI's environmental consultant Shannon Lynn said during a webinar that they don't require federal permits for hazardous emissions.

As residential pressure built in January, xAI applied for permits for 15 of its turbines that will allegedly be permanent.

Lynn said, however, that the company will wait until the application process is approved before pollution control is installed on those turbines.

How to Be Good Citizens of Earth and **Not Pollute** the Air?

Multiple cases of asthma and cancer in local families are attributed to the air pollution, and many residents are calling the xAI's permits to be denied and the plant shut down.

But Musk's history with environmental disregard has been equally problematic.

Now, xAI has also been accused of being deceptive regarding the number of turbines running.

Memphis Light, Gas and Water and chamber officials suggested in the summer of 2024 that Musk's company had 18 turbines of varying sizes - xAl filed for permits for 15 turbines at 16MW each.

At the end of March, environmental groups flew over the facility and took photographs of the turbines. The aerial photos pictured 35 turbines onsite, Politico reported.

At the end of March, environmental groups flew over the facility and took photographs of the turbines. The aerial photos pictured 35 turbines onsite, Politico reported

However, Memphis Mayor Paul Young said only 15 were actually running and the remainder were backups.

Yet, in late April, the groups flew over the site again with thermal cameras and found 33 turbines were giving off significant heat signals which signify the generation of electricity and pollution.

In a webinar in April, Lynn said xAI did not need air permits for 35 turbines onsite because 'there's rules that say temporary sources can be in place for up to 364 days

a year. They are not subject to permitting requirements.'

<sup>&#</sup>x27;There needs to be a permit beforehand. You don't just get that first year for free,' he told Politico.

# **Outline**

- Epitaxial Doping: Solid Phase Epitaxy (SPE), Liquid Phase Epitaxy (LPE) and Gas/Vapor Phase Epitaxy (VPE) or Chemical Vapor Deposition (CVD)

- 1979: Liquid Phase Epi (LPE) of InP at Hughes Malibu Research Labs (Summer 1979 BS Thesis)

- 1980: Molecular Beam Epitaxy (MBE) of InP at NTT Musashino Labs (Jun-Dec 1980 MS Thesis)

- 1981-1983: CMOS Latchup (MeV implantation and p/p+ Epi + Intrinsic Gettering) at National Semiconductor.

- 1983-1992: Blanket and Selective Si-Epi/Poly CVD at Applied Materials

- 1992-1997: High Energy (MeV) Ion Implantation for Epi replacement at Genus

- 1997-2016: Ultra Shallow Junction and Dopant Activation by Diffusionless Anneal (SPE or LPE) at Varian and JOB Technologies

- 2012-Present: Mobility Enhancement and Contact Resistance with Ge + Sn implant with SPE/LPE

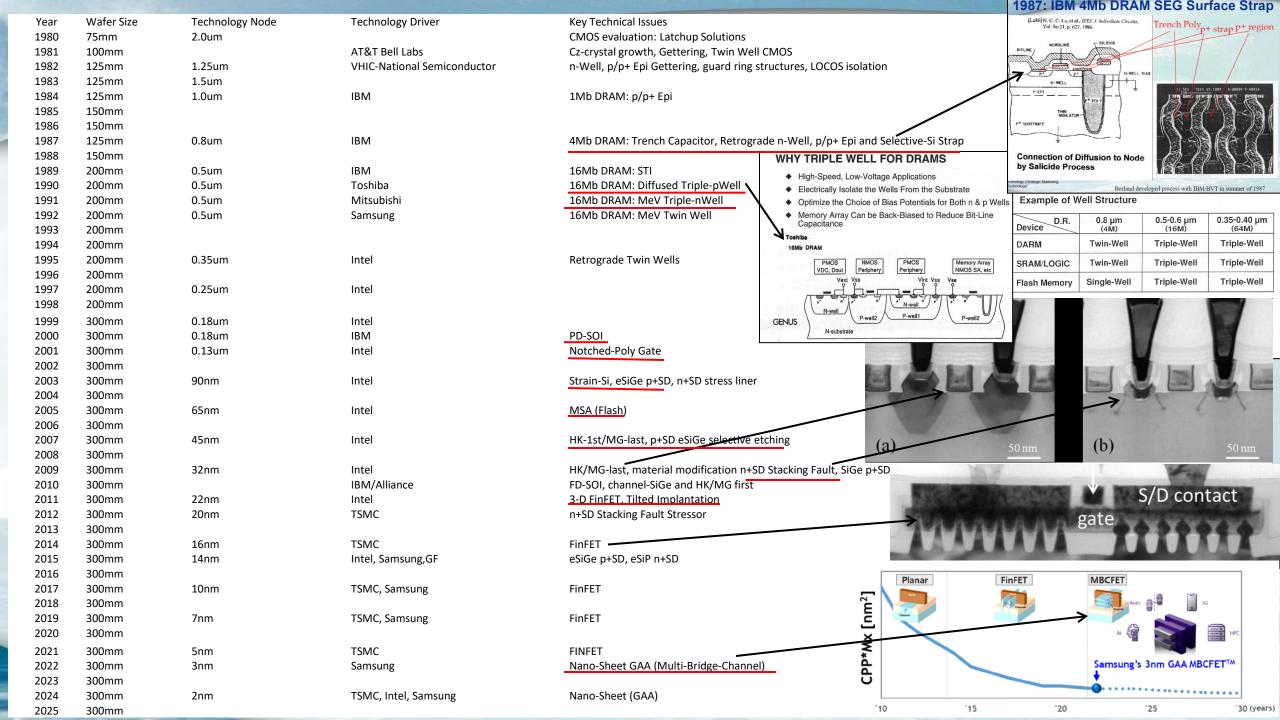

- 1980s (2um to 0.5um Node):

- 1990s → Ultra Shallow Junction (USJ) Formation for S/D Extension.

- 2000s (130nm to 20nm Node)

- 2010s→ 3-D FinFET (22nm to 7nm Node)

- 2020s. (5nm. to 10A. Node)

- Summary:

# **Outline**

- Epitaxial Doping: Solid Phase Epitaxy (SPE), Liquid Phase Epitaxy (LPE) and Gas/Vapor Phase Epitaxy (VPE) or Chemical Vapor Deposition (CVD)

- 1980s (2um to 0.5um Node):

- Blanket Doped Epi for Bipolar, BiCMOS and CMOS Technology.

- Selective Epi Growth (SEG), Selective Silicon Growth (SSG)and Selective Poly/Amorphous Deposition (SPD) Undoped or In-Situ Doped.

- 1990s → Ultra Shallow Junction (USJ) Formation for S/D Extension.

- Recess Etched SEG for Single S/D

- 2000s (130nm to 20nm Node)

- USJ For S/D Extension (SDE) and Lightly Doped Drain (LDD)

- N+ S/D Stressor and SiGe-channel

- 2010s→ 3-D FinFET (22nm to 7nm Node)

- Selective Epi for FinFET S/D Technology

- 2020s (5nm to 10A Node)

- Selective Epi for SiGe-Fin Formation

- Si/SiGe/Si/SiGe Stacked Multilayer Epi for Gate All Around (GAA) Nano-Sheet

- Contact Resistance with Elevated S/D and Merged Wrap Around Contacts

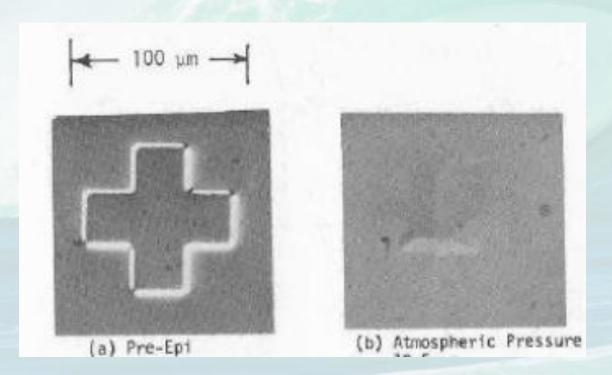

# Bipolar Epi Technology: In the Late 1970s, Reduced Pressure Epi Systems Developed To Reduce Buried Layer Pattern Shift Lithography Effects and n+ Arsenic BL Autodoping Control

J.O.B. Technologies (Strategic Marketing, Sales & Technology)

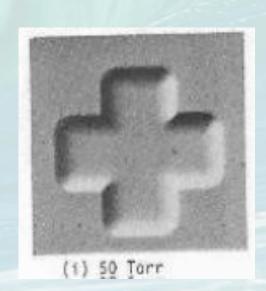

### WHY TRIPLE WELL FOR DRAMS

- High-Speed, Low-Voltage Applications

- Electrically Isolate the Wells From the Substrate

- Optimize the Choice of Bias Potentials for Both n & p Wells

- Memory Array Can be Back-Biased to Reduce Bit-Line Capacitance

Toshiba

16Mb DRAM

# Toshiba 4Mb to 64Mb DRAM Technology

#### Introduciton

#### **Example of Well Structure**

| Device D.R.  | 0.8 μm<br>(4M) | 0.5-0.6 µm<br>(16M) | 0.35-0.40 µm<br>(64M) |

|--------------|----------------|---------------------|-----------------------|

| DARM         | Twin-Well      | Triple-Well         | Triple-Well           |

| SRAM/LOGIC   | Twin-Well      | Triple-Well         | Triple-Well           |

| Flash Memory | Single-Well    | Triple-Well         | Triple-Well           |

- Reduction of Power Consumption

- Relax of Electric Field for High Reliability

- ∀Various types of Device Structure

S. Mori and K. Hashimoto, Toshiba Corporation presentation material at the Genus Seminar, July 19, 1993

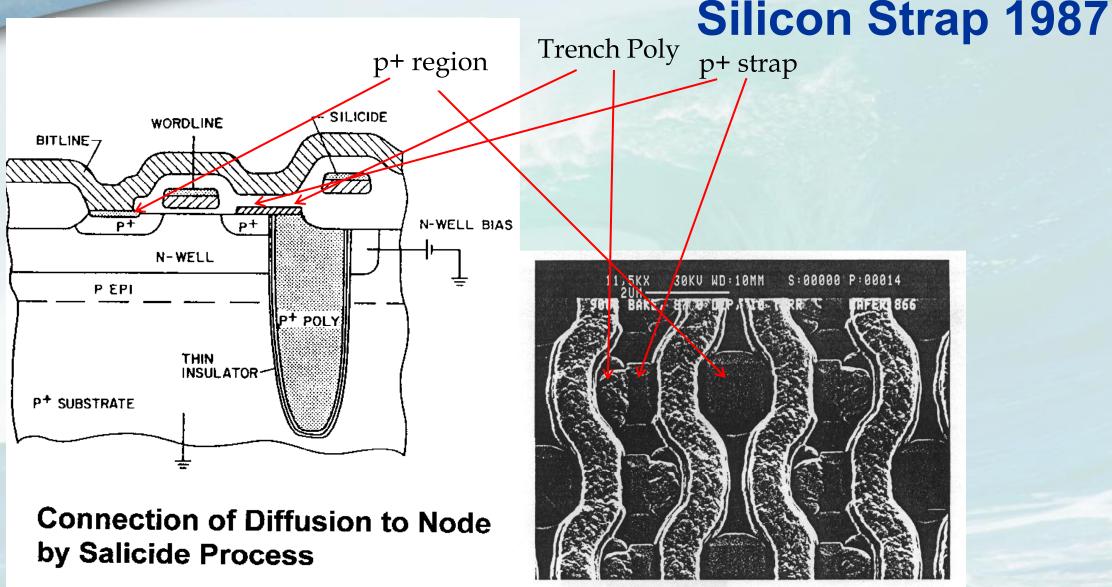

# 1st SEG Production: IBM 4MbDRAM Silicided Selective

# **Borland IEDM 1987 Invited** Talk Paper 2.1 p.12

Siemens 4Mb DRAM Development Siemens/Toshiba Joint DRAM Team

> 25) H. Binder, H. Geiger, R. Kakoschke, H. Muhlhuff and S. Rohl, Extended Abstracts of the 18th (1986 International) Conference on Solid State Devices and Materials, Tokyo,

Japan, p. 299, Aug., 1986.

$5.1 \mu$

4 Mega Bit DRAM trench capacitor sidewall doping by SEG (25).

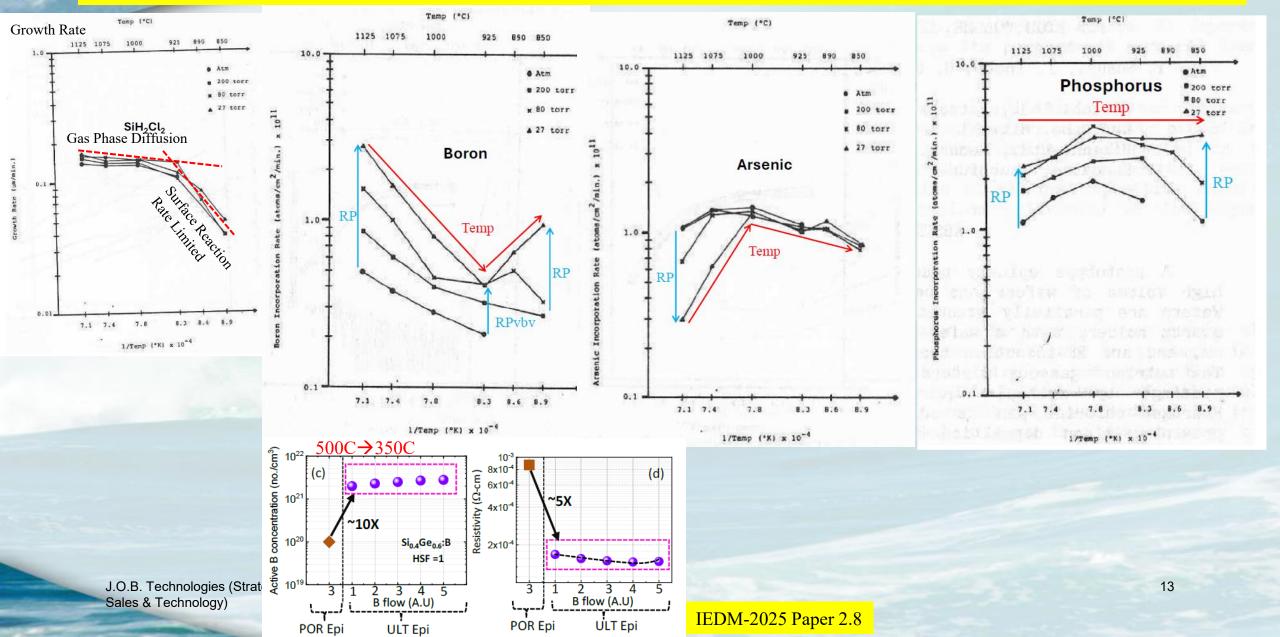

# Si-Epi Growth Rate and Dopant Incorporation

J. Borland, T. Thompson, V. Tagle and W. Benzing, Proceedings of the 10th International Conference on CVD 1984, the Electrochemical Society, p.275.

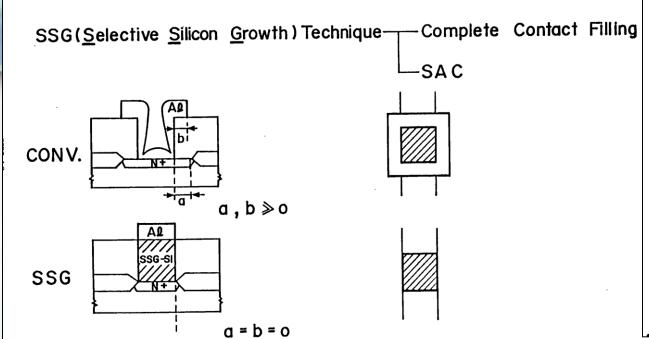

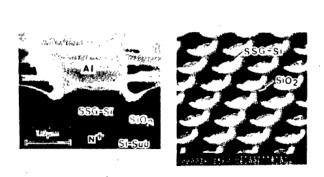

#### SAC (Self-Aligned Contact) Technology

# TOSHIBA'S 1 MBIT SRAM WITH SEG SELF-ALIGNED CONTACT HOLE FILLER

H. Shibata, S. Samata, M. Saitoh, T. Matsuno, H. Sasaki, Y. Matsushita, k. Hashimoto and J. Matsunaga, 1987 Symposium on VLSI Technology, IEEE Cat. No. 87 TH 0189-1, P. 75, May 1987

H. Shibata, S. Samata, M. Saitoh, T. Matsuno, H. Sasaki, Y. Matsushita, K. Hashimoto and J. Matsunaga, **Toshiba**, "Low-Resistive and Selective Silicon Growth as a Self-Aligned Contact Hole Filler and its Application to 1M bit Static RAM", 1987 Symposium on VLSI Technology, paper VIII-4, p. 75.

J.O.B. Technologies (Strategic Marketing, Sales & Technology)

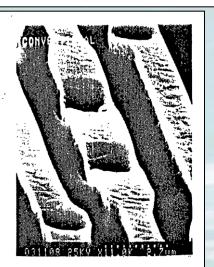

SSG

CONV.

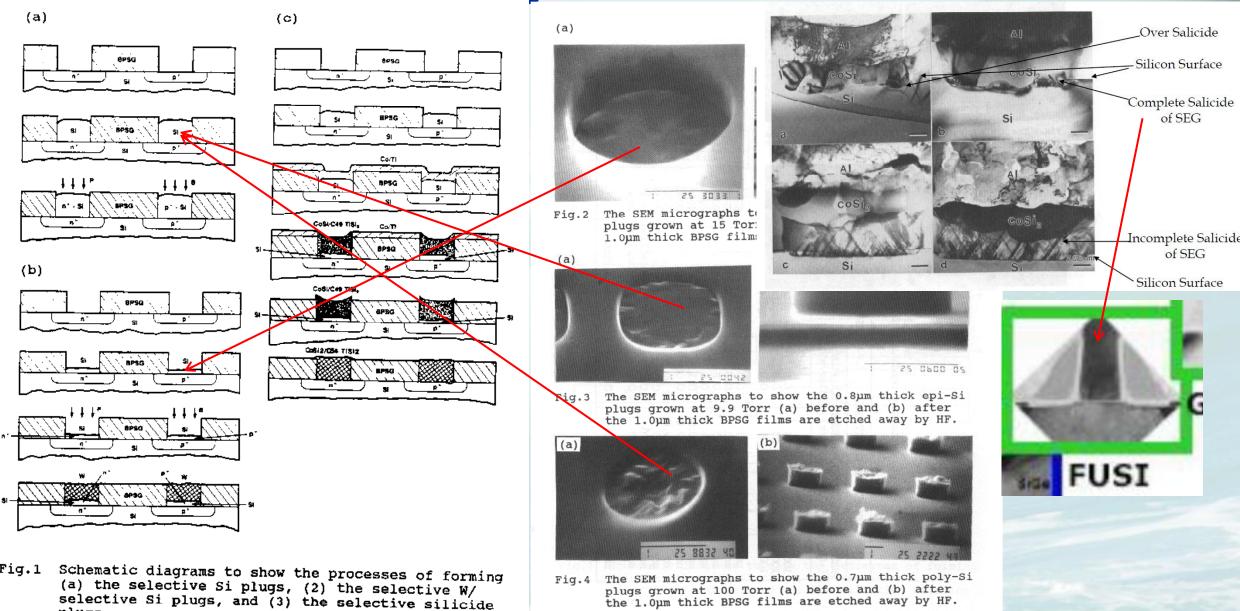

# Selective Epi or Poly Contact Fill With Salicide

CS Wei, V Murali, D. Fraser and **J. Borland**, **Intel and Applied Materials**, "The Use of Selective Silicon or Silicide Plugs For Submicron Contact Fill", ECS Symposium on ULSI Science & Technology 1989, p. 637, PV89-9 and VMIC, June 1989.

pluas.

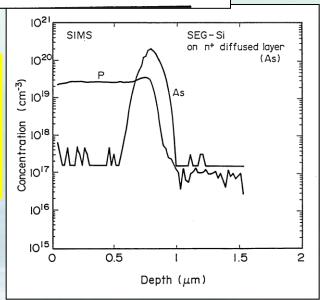

# Samsung DRAM SEG Elevated Contacts

J.W. Park, ULSI Process Integration II, the Electrochemical Society, 2001, p.50.

### **Outline**

- Epitaxial Doping: Solid Phase Epitaxy (SPE), Liquid Phase Epitaxy (LPE) and Gas/Vapor Phase Epitaxy (VPE) or Chemical Vapor Deposition (CVD)

- 1980s (2um to 0.5um Node):

- Blanket Doped Epi for Bipolar, BiCMOS and CMOS Technology.

- Selective Epi Growth (SEG), Selective Silicon Growth (SSG)and Selective Poly/Amorphous Deposition (SPD) Undoped or In-Situ Doped.

- 1990s → Ultra Shallow Junction (USJ) Formation for S/D Extension.

- Recess Etched SEG for Single S/D

- 2000s (130nm to 20nm Node)

- USJ For S/D Extension (SDE) and Lightly Doped Drain (LDD)

- N+ S/D Stressor and SiGe-channel

- 2010s→ 3-D FinFET (22nm to 7nm Node)

- Selective Epi for FinFET S/D Technology

- 2020s (5nm to 10A Node)

- Selective Epi for SiGe-Fin Formation

- Si/SiGe/Si/SiGe Stacked Multilayer Epi for Gate All Around (GAA) Nano-Sheet

- Contact Resistance with Elevated S/D and Merged Wrap Around Contacts

# Toshiba Selective Silicon Buried S/D for USJ (VLSI Sym 1996)

#### Abstract

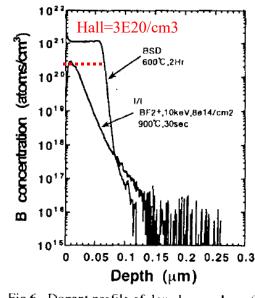

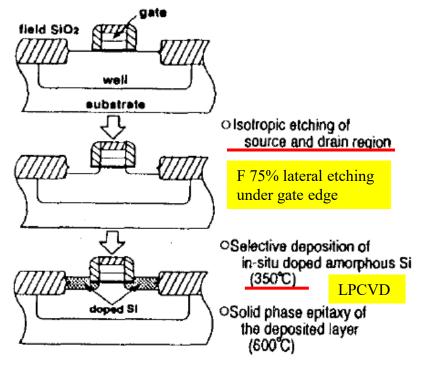

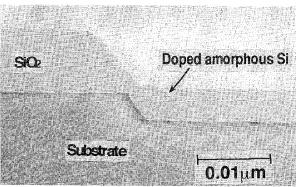

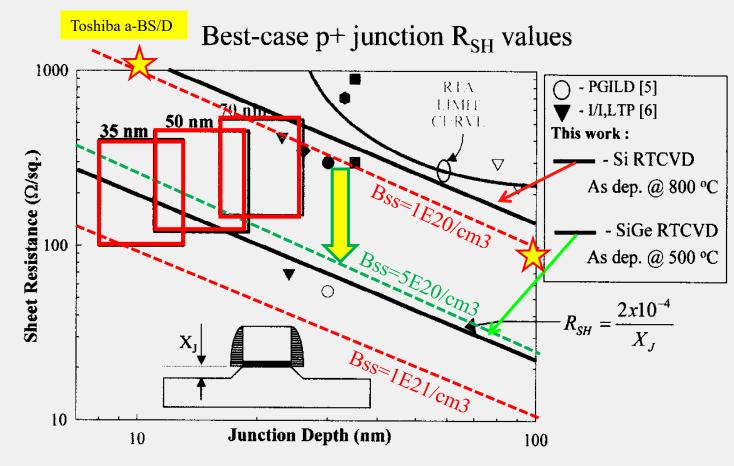

Buried source and drain (BSD) structure, that realize ultrashallow junction, is proposed. Regions for source and drain are etched off. In-situ highly doped amorphous silicon layer is selectively deposited on the etched region and is crystallized by solid phase epitaxy. Junction depth can be shallowed up to 10 nm without lowering the dopant concentration, because the doped layer can be used as source and drain. Thus, the sheet-resistance was lowered to 300  $\Omega$ / for a junction with the depth of 30 nm. Junction leakage current for BSD structure was equal to or lower than that fabricated by ion-implantation process.

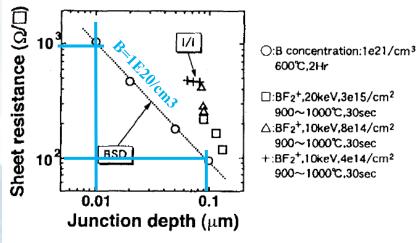

Fig. 5 Sheet resistance dependence on the junction depth. The annealing temperature for BSD was 600°C. Ion-implanted samples were fabricated with RTA.

Fig.6 Dopant profile of doped amorphous Si and ion-implanted samples.

Fig.2 Process sequence for BSD structure.

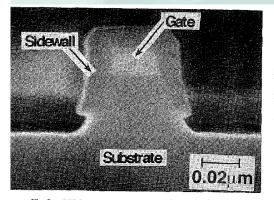

Fig.3 SEM photograph around the etched region.

Fig.4 TEM photograph of selectively deposited amorphous silicon.

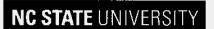

# NCSU Research on SEG Single S/D for p+ USJ

A group of researchers at North Caroline State University (NCSU) lead by **Prof Ozturk** with funding support from SRC-SEMATECH researched these issues and published their research results starting in 1999 showing how SEG for S/D engineering can extend the NTRS roadmap to sub-30nm nodes.

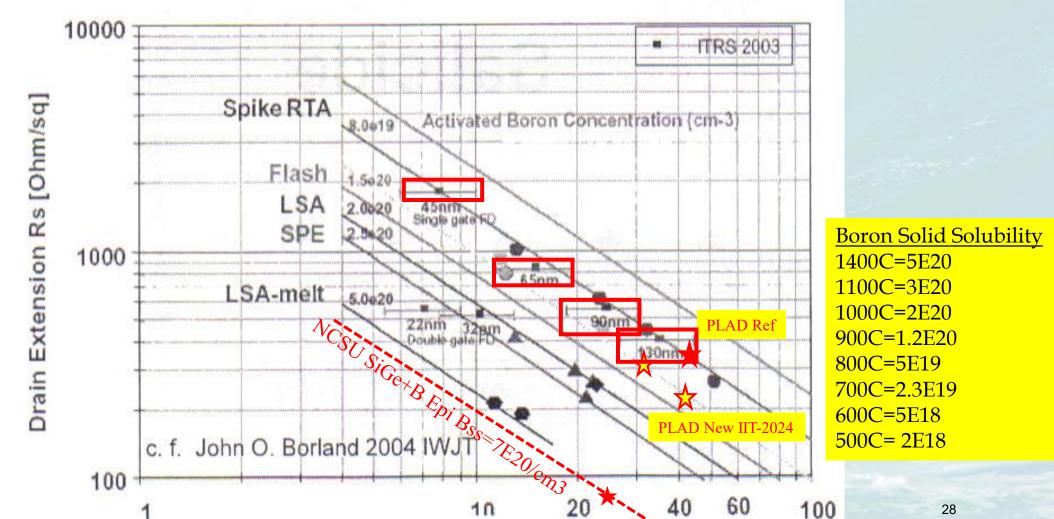

ECS May 1999 Symposium on Advances in Rapid Thermal Process titled "Ultra-Shallow P+-N Junctions For 50-70nm CMOS Using Selectively Grown In-Situ Boron Doped Silicon Films" achieved SEG S/D B levels up to 3E21/cm<sup>3</sup>, an order of magnitude above Bss (Boron solid solubility) limit in silicon.

- » As-deposited Si junctions are insufficient for future nodes.

- » SiGe junctions satisfy 35-70 nm R<sub>SH</sub>-X<sub>J</sub> specifications.

- » Laser annealing processes show promise.

- → Preclusion of replacement-gate scheme?

70nm CMOS", **IEDM-2000**, section 18.3, p. 437.

# **Outline**

- Epitaxial Doping: Solid Phase Epitaxy (SPE), Liquid Phase Epitaxy (LPE) and Gas/Vapor Phase Epitaxy (VPE) or Chemical Vapor Deposition (CVD)

- 1980s (2um to 0.5um Node):

- Blanket Doped Epi for Bipolar, BiCMOS and CMOS Technology.

- Selective Epi Growth (SEG), Selective Silicon Growth (SSG)and Selective Poly/Amorphous Deposition (SPD) Undoped or In-Situ Doped.

- 1990s → Ultra Shallow Junction (USJ) Formation for S/D Extension.

- Recess Etched SEG for Single S/D

- 2000s (130nm to 20nm Node)

- USJ For S/D Extension (SDE) and Lightly Doped Drain (LDD)

- N+ S/D Stressor and SiGe-channel

- 2010s→ 3-D FinFET (22nm to 7nm Node)

- Selective Epi for FinFET S/D Technology

- 2020s (5nm to 10A Node)

- Selective Epi for SiGe-Fin Formation

- Si/SiGe/Si/SiGe Stacked Multilayer Epi for Gate All Around (GAA) Nano-Sheet

- Contact Resistance with Elevated S/D and Merged Wrap Around Contacts

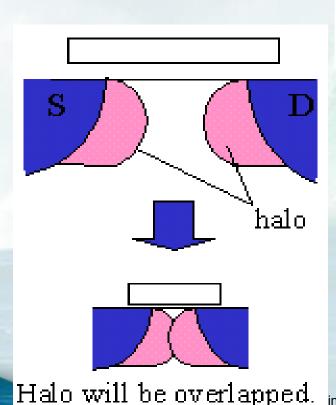

# Lateral Channel And Source Drain Engineering For HALO & SDE (45nm Node Lg=22nm, Xj=9.5nm, Yj=5.0nm)

H. Iwai, TIT, vTech 2002, July 02

SDE Gate

Overlap

Depth

Source

Metallurgical

Spacing

Drain

Figure 9: Terminology used in this discussion

Gate

| Source | Sour

Fig. 1. Source, drain, and super-halo doping contours in a 25 nm nMOSFET design. The channel length is defined by the points where the source-drain doping concentration falls to  $2\times10^{19}~\rm cm^{-3}$ . The dashed lines show the potential contours for zero gate voltage and a drain bias of 1.0 V.  $\psi$  = 0 references to the midgap energy level of the substrate.

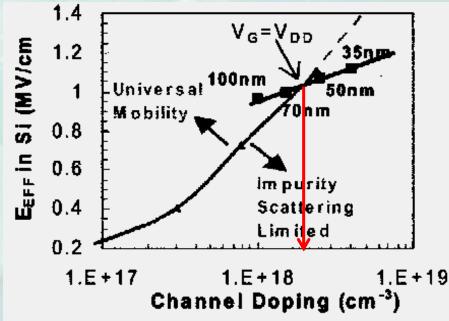

Fig. 5 Universal mobility vs. channel impurity scattering dominated regimes. Device falls off the universal mobility controlled regime for 35nm L<sub>GATE</sub>.

T. Ghani et al., Intel, VLSI Sym. 2000, p. 174

Y. Taur et al, IBM, IEDM-98

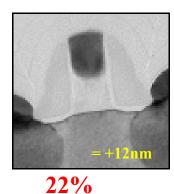

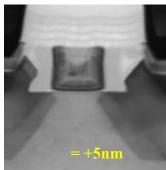

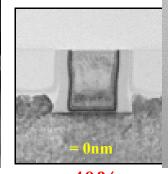

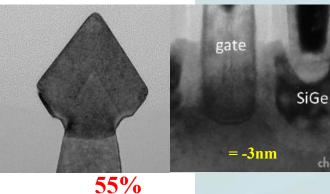

# Intel Transistor Leadership

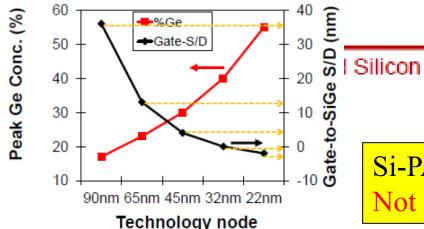

Ge=17% Invented SiGe Strained Silicon

2<sup>nd</sup> Gen. SiGe Strained Silicon

30% Invented Gate-Last High-k Metal Gate

40% 2<sup>nd</sup> Gen. Gate-Last High-k Metal Gate

First to Implement Tri-Gate

Tri-Gate

High-k Metal Gate

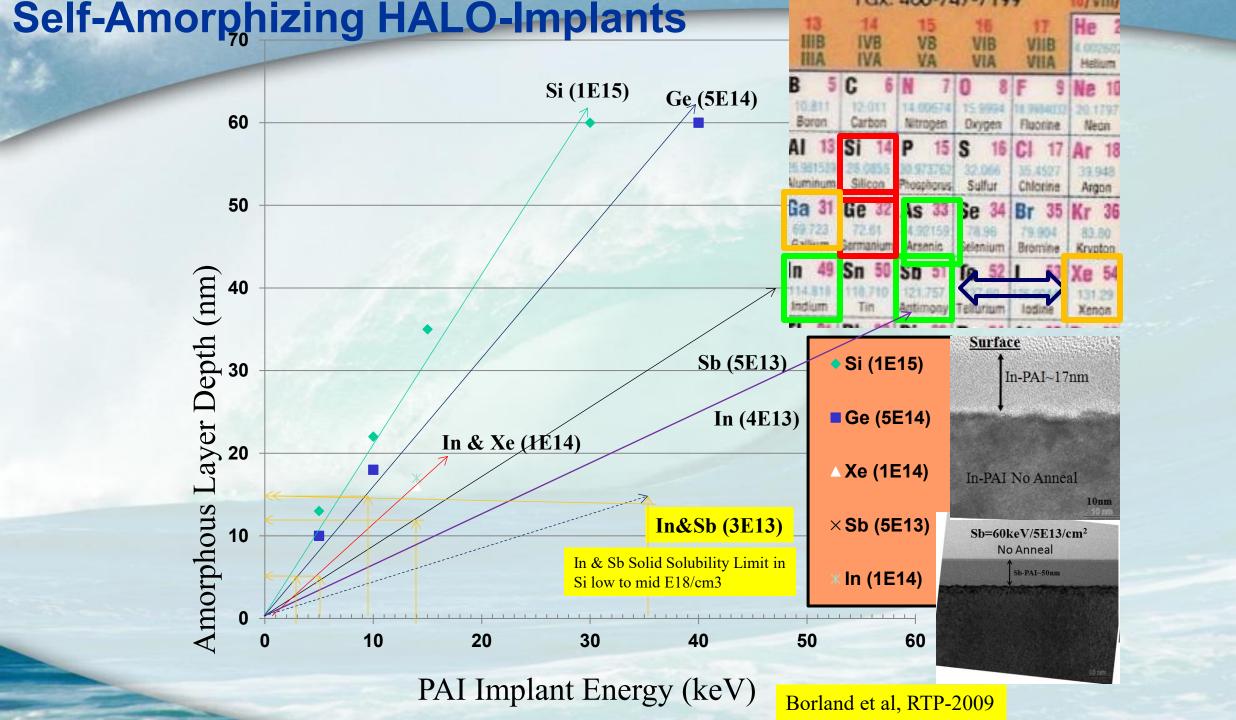

Si-PAI to improve cavity recess etch control and uniformity!

Not Using Doped Epi Diffusion For SDE nor In-situ Doped p+eSiGe S/D

#### Low Temperature Activation Of Ion Implanted Dopants: A Review

(Invited Paper)

IWJT 2002

#### John O. Borland

Varian Semiconductor Equipment Associates

4 Stanley Tucker Drive, Newburyport, MA 01950

Tel: (+1) 978-463-5070, Fax: (+1) 978-462-0210, e-mail: john.borland@vsea.com

#### Abstract

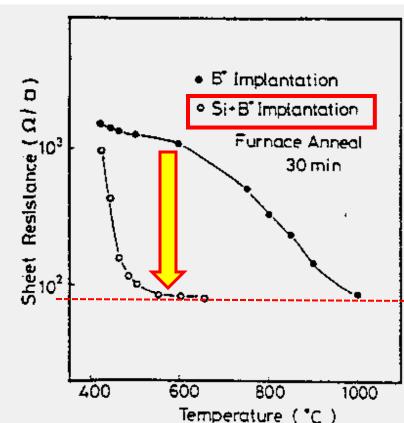

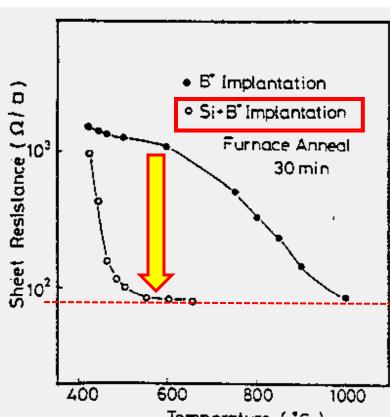

Ion implanted dopants can be electrically activated through low temperature annealing in the 450°C to 800°C as reported in literature over the past 25 years. However, researchers in the last few years have applied this technique to realize ultra shallow junctions (USJ) for source drain extensions to satisfy the device junction roadmap requirements for the 65nm node and beyond. Therefore this paper will review the current status of low temperature annealing for USJ formation.

#### 3. Summary

In summary, ion implanted dopants can be electrically activated by low temperature SPE the 450-750°C range resulting in shallow junctions of <13.5nm satisfying the 65nm node and beyond. To increase dopant activation Si or Ge-PAI are used to achieve 2.5E20/cm<sup>3</sup> boron electrically active levels. Additional research to improve junction leakage still needs to be done.

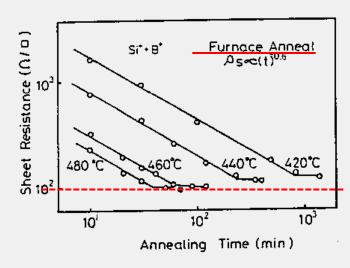

Fig.3 Annealing time dependence of the sheet resistance at various annealing temperature.

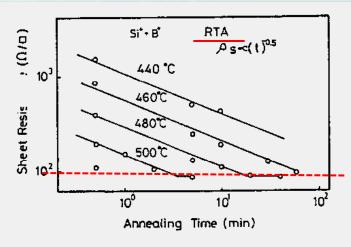

Fig.7 Annealing time dependence of the sheet resistance after RTA.

Onishi et al., Sharp, SPIE vol. 1189 Rapid Isothermal Processing (1989)

Any deposition doping requires lateral diffusion which will be limited by dopant solid solubility activation unless amorphous SPE or LPE as shown by Intel.

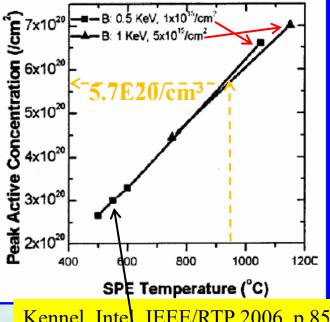

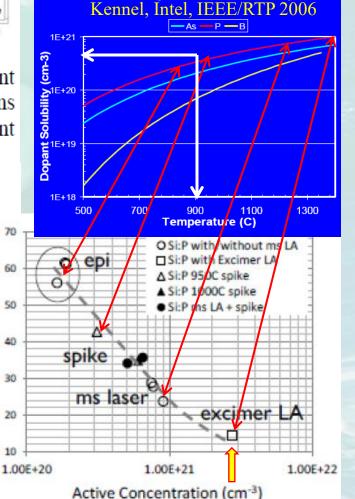

Kennel, Intel, IEEE/RTP 2006, p.85

With SPE Non-Equilibrium **Activation of Boron >> Bss But Requires Amorphization!**

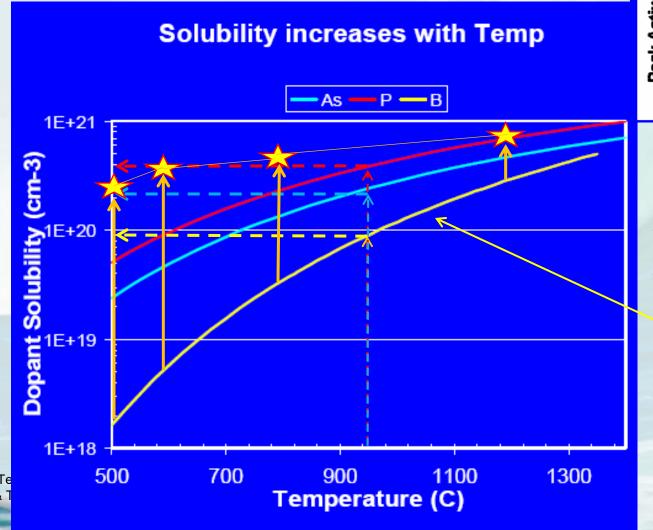

**Boron activation limited** by low Bss (Boron solid solubility) and not by implanted dose

**Boron Solid Solubility** 1400C=5E20 1100C=3E20 1000C=2E20 900C=1.2E20 800C=5E19 700C=2.3E19 600C=5E18 500C= 2E18

J.O.B. Te Sales &

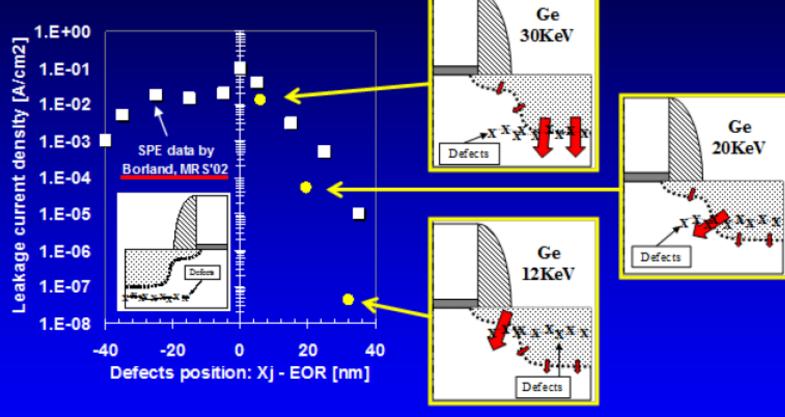

# **Defects position**

Defect position as function of junction depth is very important to contain the leakage

Honolulu VLSI Technology June 19th 2008 : 19-1 C. Ortolland IMEC

# Reduced thermal budgets (e.g. flash and/or laser anneal) are instrumental to continued junction depth scaling while containing R<sub>sh</sub>

Extension Xj [nm]

J.O.B. Technol Sales & Techn

Y.J. Mii, TSMC, short course, VLSI Sym 2005

# Intel 32nm NMOS Stacking Fault Stressor

- (19) United States

- (12) Patent Application Publication (10) Pub. No.: US 2010/0038685 A1 Weber et al.

- Feb. 18, 2010 (43) Pub. Date:

#### (54) ENHANCED DISLOCATION STRESS TRANSISTOR

Cory Weber, Hillsboro, OR (US); (76) Inventors: Mark Liu, West Linn, OR (US); Anand Murthy, Portland, OR

(US); Hemant Deshpande, Beaverton, OR (US); Daniel B. Aubertine, North Plains, OR (US)

Correspondence Address: INTEL CORPORATION c/o CPA Global P.O. BOX 52050 MINNEAPOLIS, MN 55402 (US)

(21) Appl. No.: 12/191,814

(22) Filed: Aug. 14, 2008

#### **Publication Classification**

(51) Int. Cl. H01L 29/78 (2006.01)H01L 21/336 (2006.01)

(52) U.S. Cl. ..... 257/288: 438/300: 257/E29.255: 257/E21.409

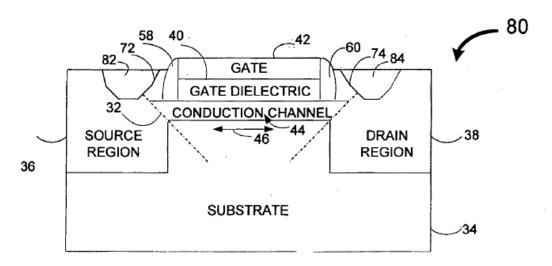

#### ABSTRACT

A device is provided. The device includes a transistor formed on a semiconductor substrate, the transistor having a conduction channel. The device includes at least one edge dislocation formed adjacent to the conduction channel on the semiconductor substrate. The device also includes at least one free surface introduced above the conduction channel and the at least one edge dislocation.

by amorphizing the substrate 34 by implanting high dose silicon after gate patterning and before tip implantation using

A. Ogura, Meiji University, Private Communication and SSDM-2011 paper E-7-3, p. 933.

# Apple A5 APL2498 (Samsung 32 nm HKMG gate-first LP process)

| Apple SoC Evolution |             |             |          |                 |         |  |  |

|---------------------|-------------|-------------|----------|-----------------|---------|--|--|

|                     | CPU<br>Perf | GPU<br>Perf | Die Size | Transisto<br>rs | Process |  |  |

| A5                  | ~13x        | ~20x        | 122m2    | <1B             | 45nm    |  |  |

| A6                  | ~26x        | ~34x        | 97mm2    | <1B             | 32nm    |  |  |

| A7                  | 40x         | 56x         | 102mm2   | >1B             | 28nm    |  |  |

| A8                  | 50x         | 84x         | 89mm2    | ~2B             | 20nm    |  |  |

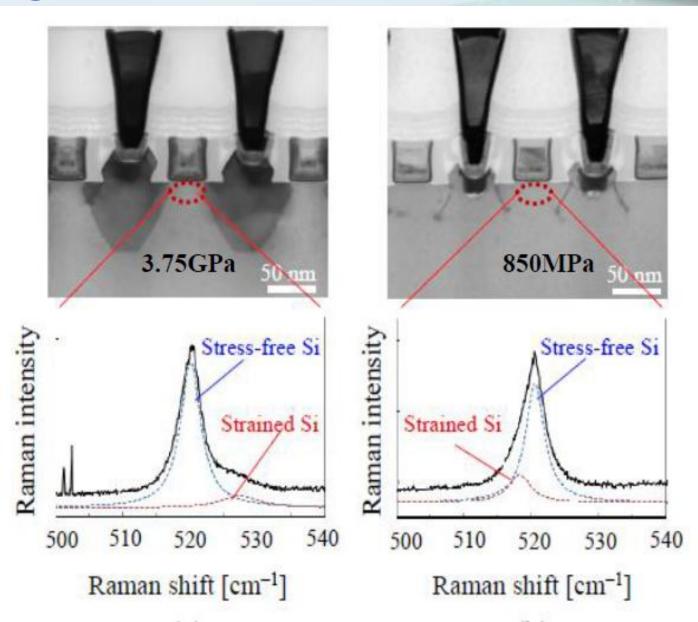

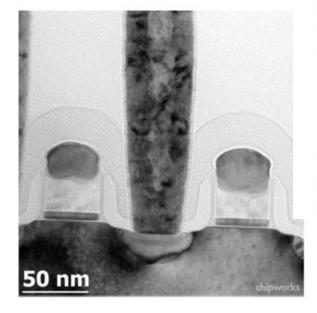

#### Apple/Samsung APL2498 NMOS Transistor

- Minimum gate length observed ~38 nm

- Gate-silicide ~17 nm

- Differential oxide spacer

- Stress memorization & tensile CESL?

- Normal silicidation, Ptdoped NiSi (GF was almost fully silicided)

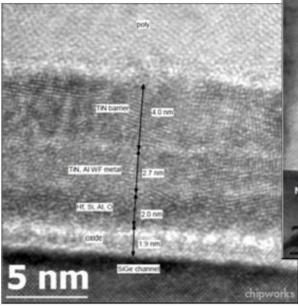

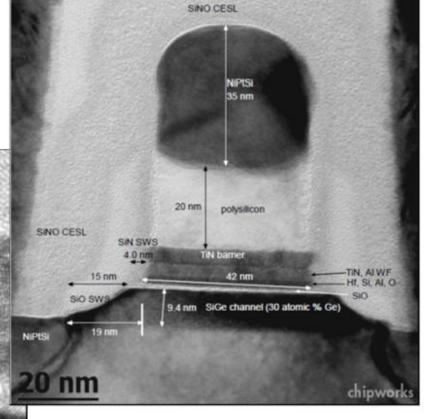

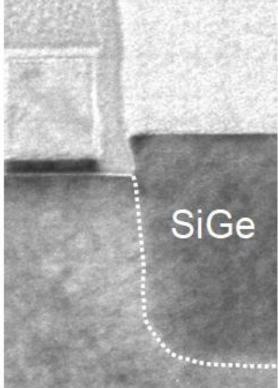

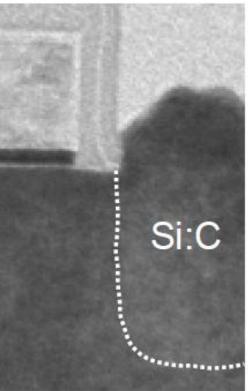

### Apple/Samsung APL2498 PMOS Transistor

- SiGe channel ~30% Ge

- TiN, Al WF source layer

- 2nd TiN layer is NMOS WF layer deposited on PMOS WF layer

11

chipworks

chipworks Inside technology

30%-SiGe Channel!

Dick James, Chipworks, Semicon/West 2015

AVS-WCJUG Meeting

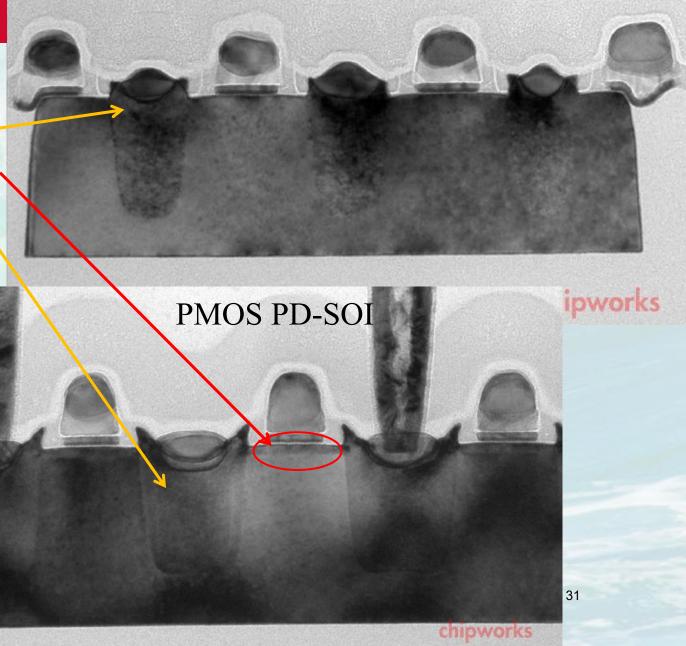

IBM POWER 8 Server Processor (22 nm SOI Gate-First HKMG Process)

S. Narasimha et. al., "22nm High-Performance SOI Technology Featuring Dual-Embedded Stressors, Epi-Plate High-K Deep-Trench Embedded DRAM and Self-Aligned Via 15LM BEOL", IEDM-2012, paper 3.3, p. 52.

eSiC c-SiGe eSiGe

**NMOS PD-SOI**

# **Outline**

- Epitaxial Doping: Solid Phase Epitaxy (SPE), Liquid Phase Epitaxy (LPE) and Gas/Vapor Phase Epitaxy (VPE) or Chemical Vapor Deposition (CVD)

- 1980s (2um to 0.5um Node):

- Blanket Doped Epi for Bipolar, BiCMOS and CMOS Technology.

- Selective Epi Growth (SEG), Selective Silicon Growth (SSG)and Selective Poly/Amorphous Deposition (SPD) Undoped or In-Situ Doped.

- 1990s → Ultra Shallow Junction (USJ) Formation for S/D Extension.

- Recess Etched SEG for Single S/D

- 2000s (130nm to 20nm Node)

- USJ For S/D Extension (SDE) and Lightly Doped Drain (LDD)

- N+ S/D Stressor and SiGe-channel

- 2010s→ 3-D FinFET (22nm to 7nm Node)

- Selective Epi for FinFET S/D Technology

- 2020s (5nm to 10A Node)

- Selective Epi for SiGe-Fin Formation

- Si/SiGe/Si/SiGe Stacked Multilayer Epi for Gate All Around (GAA) Nano-Sheet

- Contact Resistance with Elevated S/D and Merged Wrap Around Contacts

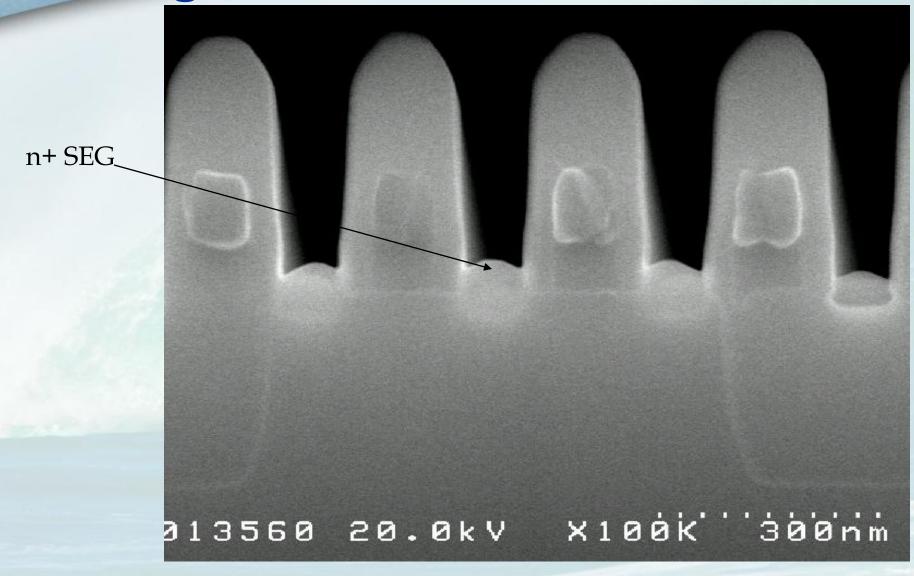

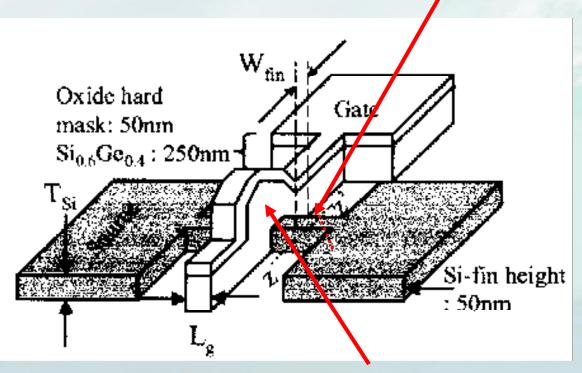

# Single & Multi-FINFET Double-Gate Devices

**High Tilt Implant For LG-SS/D**

**Asymmetric n+/p+ Poly/Gate**

Borland, Moroz, Iwai, Maszara & Wang, Varian/Synopsys/TIT/AMD/TSMC, Solid State Technology, June 2003

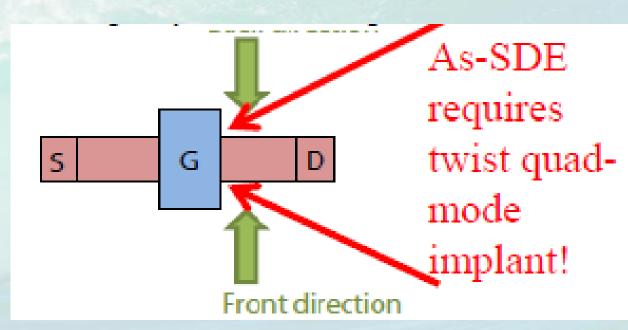

# Tri-Gate Transistor Architecture with High-k Gate Dielectrics, Metal Gates and Strain Engineering

Jack Kavalieros, Brian Doyle, Suman Datta, Gilbert Dewey, Mark Doczy, Ben Jin, Dan Lionberger, Matthew Metz, Willy Rachmady, Marko Radosavljevic, Uday Shah, Nancy Zelick and Robert Chau

Components Research, Technology and Manufacturing Group, Intel Corporation, Mail Stop RA3-252, 5200 NE Elam Young Parkway, Hillsboro, OR 97124, USA Email: Robert.S.Chau@Intel.com

TriGate FIN patterning is achieved using a reactive ion etching process, optimized to achieve highly vertical sidewall profiles for

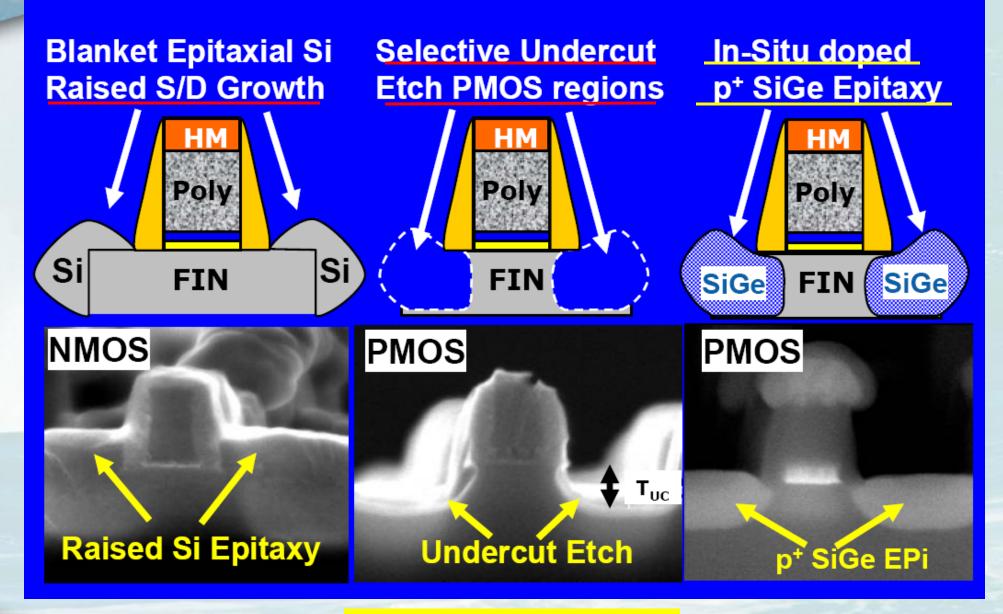

FIN. Following tip-extension implant and spacer formation we introduce selective silicon (NMOS) and embedded SiGe (PMOS) epitaxy for raised source/drains. Tensile strained nitride layers patterned over NMOS transistors are also investigated to enhance electron mobility [5].

The near mid-gap workfunction allows us to set the V<sub>T</sub> of the TriGate devices with a significantly lower dopant concentration (10<sup>17</sup>cm<sup>-3</sup>) in the channel as compared to the planar bulk Si technology. This in turn enables stronger gate coupling, improved channel mobility and volume

For PMOS Trigates we introduce in-situ boron doped SiGe raised source/drains as illustrated in x and y direction cross-sections of Figs.

# **Dual Epitaxial Raised S/D**

# Intel IEDM-2012 paper 3.1 on 22nm Tri-gate SoC Technology

device and reliability targets, and is fabricated with an overall process sequence similar to the 32nm planar SoC technology, with the exception of the addition of fin-related diffusion fabrication [3].

Does this mean Tip/SDE Implantation?

transistor pitch scaling. High Ge-embedded epitaxial SiGe technology is used for PMOS, raised S/D technology is used in NMOS, and fifth-generation strained silicon technology is used to provide compressive and tensile stress on P-ch and N-

Like for 32nm planar

planar transistors require high channel doping and V<sub>T</sub> to control subthreshold leakages; such processes are not scalable and result in severe mobility and drive current degradation, and high junction leakages. The Tri-Gate architecture alleviates these challenges with superb short channel control at minimal channel doping levels, reducing subthreshold J.O.B. Te currents and resulting in significant mobility and drive

current gains over an equivalent planar architecture. Further

No Mention of In-situ Doped p+SiGe

Sales & T

# Comparison of Junctionless and Conventional Trigate Transistors With $L_g$ Down to 26 nm

R. Rios, A. Cappellani, M. Armstrong, A. Budrevich, H. Gomez, R. Pai, N. Rahhal-orabi, and K. Kuhn

Two JAM channel dopings were fabricated, low doped (LD JAM) and high doped (HD JAM), with P doses of  $1.5 \times 10^{13}$  and  $6 \times 10^{13}$  cm<sup>-2</sup>, respectively. IM received a B dose of  $2.5 \times 10^{13}$  cm<sup>-2</sup>. Dopants were activated using 950 °C/spike anneal before gate formation. The S/D areas were formed by Si etch and EPI Si deposition, reaching a P concentration of  $3 \times 10^{21}$  cm<sup>-3</sup>. S/D extensions were done with 45° As implants at 3.5 keV and  $1.6 \times 10^{15}$  cm<sup>-2</sup> for all cases. For JAM, the

But Pss~1.8E21/cm3 so this must be chemical and not electrical!

# Intel **22nm** node 3-D **FinFET CMOS Transi** stor

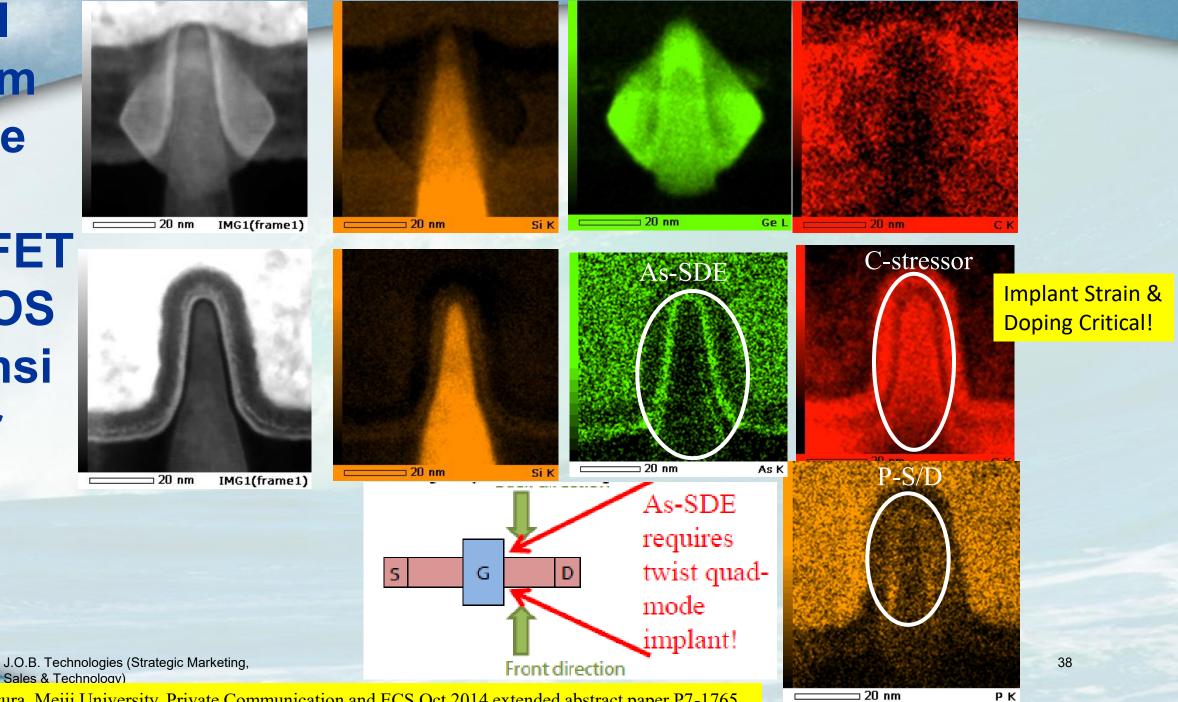

A. Ogura, Meiji University, Private Communication and ECS Oct 2014 extended abstract paper P7-1765.

**Outline**

- Epitaxial Doping: Solid Phase Epitaxy (SPE), Liquid Phase Epitaxy (LPE) and Gas/Vapor Phase Epitaxy (VPE) or Chemical Vapor Deposition (CVD)

- 1980s (2um to 0.5um Node):

- 1990s → Ultra Shallow Junction (USJ) Formation for S/D Extension.

- 2000s (130nm to 20nm Node)

- 2010s→ 3-D FinFET (22nm to 7nm Node)

- 2020s (5nm to 10A Node)

- Selective Epi for SiGe-Fin Formation

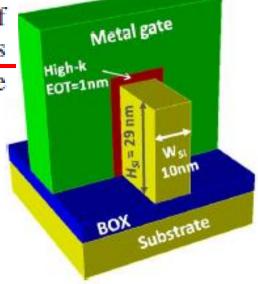

- Si/SiGe/Si/SiGe Stacked Multilayer Epi for Gate All Around (GAA) Nano-Sheet

- Contact Resistance with Elevated S/D and Merged Wrap Around Contacts

- Summary:

#### TSMC N5 SiGe Fins + S/D **Epi/Fin-Frist STI-Etch Last** $\downarrow\downarrow\downarrow\downarrow\downarrow\downarrow\downarrow\downarrow\downarrow\downarrow\downarrow\downarrow\downarrow$ SiGe Si Channel nMOS pMOS Channel Si Implant Si surface Channel SiGe (Selective) SiN HM SiGeB pMOS S/D (selective) SiP nMOS S/D (selective) Pattern Fins | 34 **Tech** Insights All content @ 2023 Techinsights, Inc. All rights reserved.

Si:P NMOS NMOS **PMOS** N3 Apple A17 NMOS

50 nm

PMOS

N5 Apple A14

Co

SiGe:B

James, Tech Insights, presentation material on TSMC N5 and N3, June 2024.

J.O.B. Technologies (Strategic Marketing, Sales & Technology)

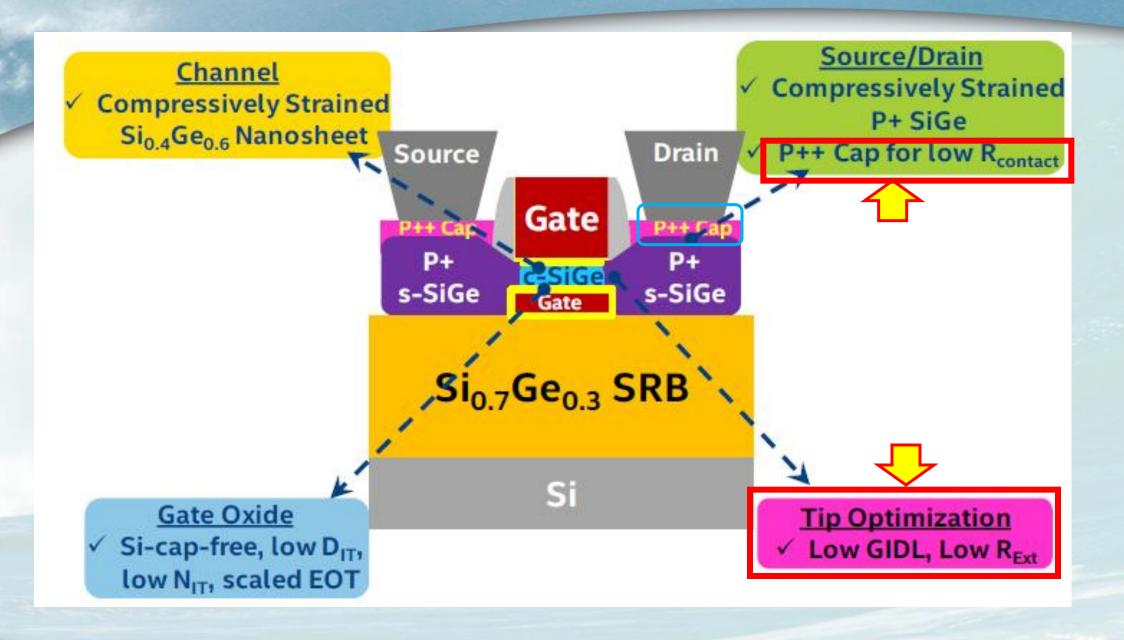

A. Agrawal et al., "Gate-All-Around Strained Si<sub>0.4</sub>Ge<sub>0.6</sub> Nanosheet PMOS on Strain Relaxed Buffer for High Performance Low Power Logic Application", IEDM-2020, paper 2.2, p.15.

# <u>Junction-engineered Scaled High-performance GAA Nanosheet FETs</u> with Ultra-low Temperature (< 350 °C) SiGe:B Source/Drain

R. Sarkar<sup>1</sup>, D. Casey<sup>2\*</sup>, A. Dutta<sup>1\*</sup>, P. Eyben<sup>1</sup>, A. Pondini<sup>1,3</sup>, H. Mertens<sup>1</sup>, T. Dursap<sup>1</sup>, C. Porret<sup>1</sup>, A. Veloso<sup>1</sup>, J. Ganguly<sup>1</sup>

R. Duflou<sup>1</sup>, C. Cullen<sup>2</sup>, P.A. Rathi<sup>1</sup>, M-S. Kim<sup>1</sup>, R. Khazaka<sup>2</sup>, J. Mitard<sup>1</sup>, L. PB. Lima<sup>1</sup>, S. Biesemans<sup>1</sup> and N. Horiguchi

limec, Kapeldreef 75, B-3001, Leuven, Belgium, <sup>2</sup>ASM, Kapeldreef 75, 3001, Leuven, Poleium,

3KU Leuven, Leuven, Belgium email: ritam.sarkar@imec.be \*equal co IEDM-2025 Paper 2.8

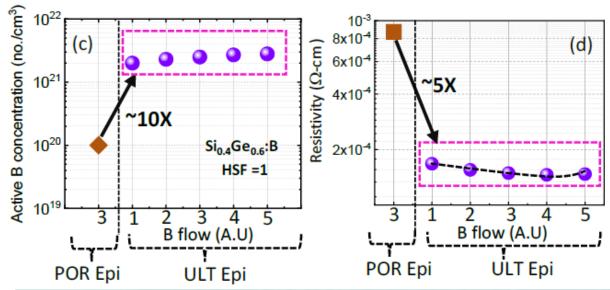

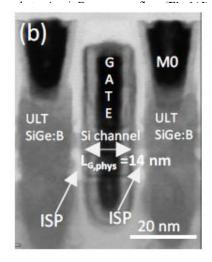

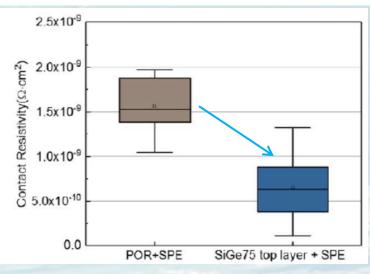

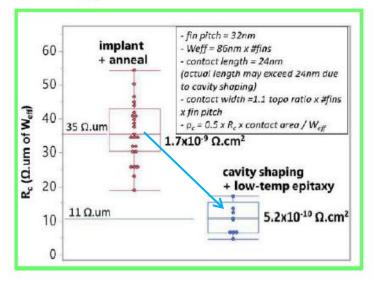

**Abstract**— We present an ultra-low-temperature (ULT) borondoped SiGe (SiGe:B) epitaxial (epi) layer as PMOS junction in a gate-all-around (GAA) Si nanosheet (NS) transistor at 48 nm contacted poly-pitch (CPP) and 14 nm gate length (L<sub>G</sub>). We investigate the impact of dopant concentration and diffusion on NS performance at different RTA conditions. We find that the ULT junction (with S/D epi growth temperature <350 °C) with controlled RTA (at 800°C) delivers over 100% improvement in performance (I<sub>D,LIN</sub> and g<sub>m,LIN</sub>) over our reference process of record (POR) epitaxy process (at 500°C) by significantly increasing the active dopant concentration and carefully position the junction under the inner spacer without degrading the short-channel effects (SCE). Moreover, contact resistivity (ρ<sub>c</sub>) reduces by ~3.5x compared to reference POR epi process.

layers with varying B precursor flow were grown epitaxially below 350 °C and subsequently characterized by HR-XRD and hall-measurement. All growth conditions were kept constant except B precursor flow. The XRD  $\omega$ -2 $\theta$  scan shown in Fig. 1(b) reveal a right shift of the SiGe peak positions with increasing boron flow, indicating enhanced substitutional incorporation of boron atoms within the crystal lattice. Finally, the hall measurement is carried out to extract the active carrier concentration sheet resistivity. Fig. 1(c) & 1(d) compared the active B concentration and sheet resistivity between POR epitaxy film at 500°C and ULT epi (<350°C) process. The results demonstrate approximately a ~10x increase in active carrier concentration and a ~5x reduction in sheet resistivity for the ULT SiGe:B process. Notably, the minimum sheet

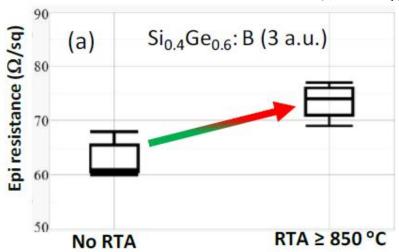

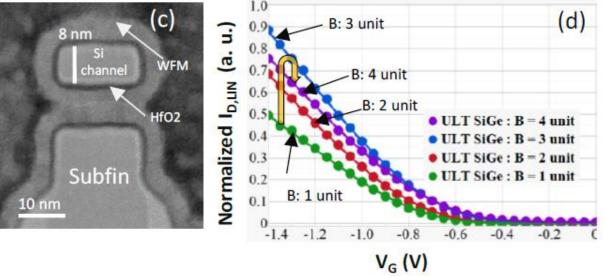

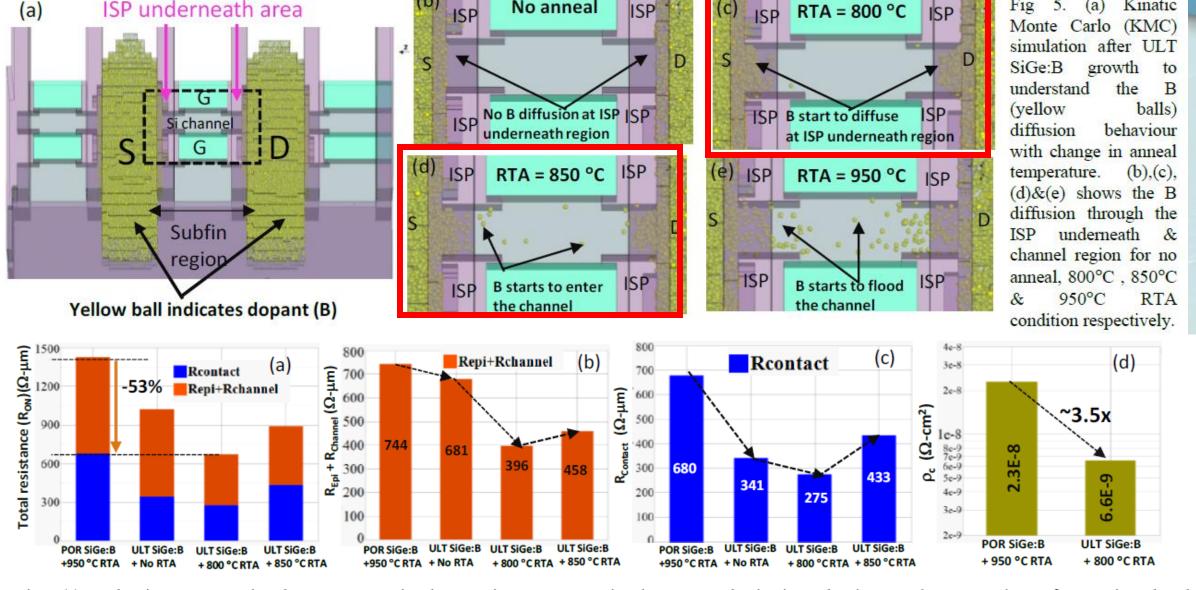

Fig 6. (a) Epi resistance comparison for no RTA and RTA  $\geq$  850 °C condition. (b), (c) & (e) shows the B diffusion through the ISP underneath region for no anneal, 800 °C and 850 °C RTA condition respectively. (b) End of the process TEM at along the nanosheet. (c) End of the process TEM at along the gate. (d) Normalized  $I_{D,LIN}$  Vs  $V_G$  curve for different B flow, suggesting that with the increase in B flow, drive current ( $I_{D,LIN}$ ) starts to increase till 3-units of B flow, thereafter, drive current drops for 4 units of B flow.

No anneal

(c)

ISP underneath area

Fig

Kinatic

(a)

Fig 8. (a) Total resistance comparison between POR epi and ULT epi process suggesting that ~53% reduction in total resistance when POR epi +950 °C RTA is replaced with ULT epi +800°C RTA (best condition). (b) Shows R<sub>Epi</sub>+R<sub>Channel</sub> resistance reduces when POR epi is replaced by ULT epi. For ULT epi process, with the increase of RTA temp. epi+channel resistance decreases suggesting more carrier diffusion at the ISP underneath & channel region. (c) Shows R<sub>Contact</sub> reduces significantly when POR epi is replaced by ULT epi +800 °C RTA. For ULT epi process, Rcontact starts to increase at 850 °C suggesting dopant de-activation. (d) pc comparison shows that best ULT condition (ULT epi +800 °C RTA) shows ~3.5x reduction in pc compared to POR condition (POR epi +950 °C RTA). IEDM-2025 Paper 2.8

# SiGe Channel for Scaled Gate-All-Around Nanosheet pFET Transistor for Advanced Logic Applications

S. Mochizuki, S. Kumar, A. Greene, K. Killic, X. Wang, H. Zhou, A. Bryant, J. Li, J. Demai <sup>1</sup>IBM Research, 257 Fuller Road, Suite 3100, Albany, NY 12203, email: smochiz@u

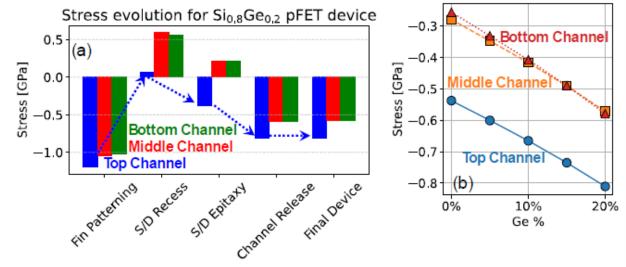

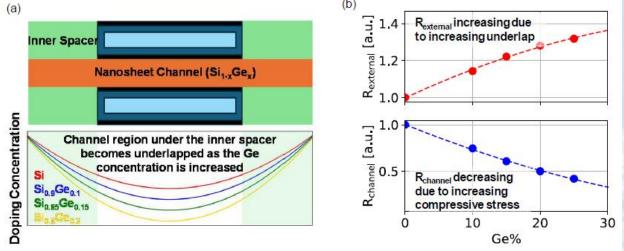

Abstract— Stacked Gate-All-Around (GAA) nanosheet p-type Field Effect Transistors (FETs) incorporating Si1-xGex channel have been successfully fabricated on scaled devices to investigate their electrical performance for next-generation logic applications. The Si<sub>1-x</sub>Ge<sub>x</sub> NS channels demonstrate high crystalline quality and substantial compressive stress (0.6-0.9 Gpa), enabling enhanced carrier transport in the scaled pFET device with 15 nm gate length and 54 nm Contacted Poly Pitch (CPP). The influence of Ge fraction and junction overlap on the device characteristics of Si<sub>1-x</sub>Ge<sub>x</sub> NS channel pFETs has been systematically analyzed to assess their impact on device scalability and transport characteristics. It is found that the Si<sub>1-x</sub>Ge<sub>x</sub> NS channel provides a 17% uplift in I<sub>EFF</sub> due to a corresponding channel resistance reduction of 34% while maintaining an excellent subthreshold slope of below 75 mV/dec. This is the first demonstration of SiGe benefit on Stacked Nanosheet GAA structures in mainstream advanced CMOS technology and corresponding gate pitch, enabling insertion of high mobility SiGe channel in future Nanosheet GAA technology.

IEDM-2025 Paper 2.7

shows the SiGe NS device integration p study. NS stack epitaxy, sacrificial layer formation, and selective removal of the channel NS release processes are highlis SiGe NS channel device formation. T epitaxial SiGe layers in the NS stack were 0% to 20%. Fig. 2 contains cross-sec crystalline defect free epitaxially grov stack. As confirmed by XRD Reciproc corresponding 113 reflections for the layer stack in Fig. 2, the epitaxial Sio.80 fully strained since the Qx value of the S: diffraction peak is aligned to that of the shows SiGe NS device structure after inn observed that the sacrificial layer has spacer formation using a deposition/e demonstrated successfully without dama Fig. 4. contains cross-sectional TEM im after SiGe channel formation with char 15 nm W. - 25 nm davice and CDD

Fig. 7. (a) TCAD-predicted stress in the three NS channels of a Si<sub>0.8</sub>Ge<sub>0.2</sub> pFET device. The plot shows the stress condition in each channel at the end of each of the key modules. (b) Stress in the final device as a function of Ge% for the three channels.

Fig

Ge

Fig. 13. (a) Schematic illustrating how higher Ge concentration in the NS channel reduces boron diffusivity, leading to increased junction underlap. (b) TCAD simulation of external and internal/channel resistances for varying Ge%.

J.O.B. Technologies (Strategic Marketing, Sales & Technology)

#### IIT-2022, TU3.03 paper

#### Time Resolved Reflectometry with Pulsed Laser Melting of Implant Amorphized Si<sub>1.x</sub>Ge<sub>x</sub>

Jesse A. Johnson II<sup>4</sup>, Xuebin Li<sup>2</sup>, Chris Hatem<sup>3</sup>, David Brown<sup>1</sup>, Bruce Adams<sup>2</sup>, Kevin S. Jones 1:

<sup>1</sup> University of Florida, Gainesville, Florida, <sup>2</sup> Applied Materials, Santa Clara, California; <sup>3</sup> Applied Materials – Varian Semiconductor Equipment, Gloucester, Massachusetts, <sup>4</sup> Mainstream Engineering, Rockledge FL

University of Florid

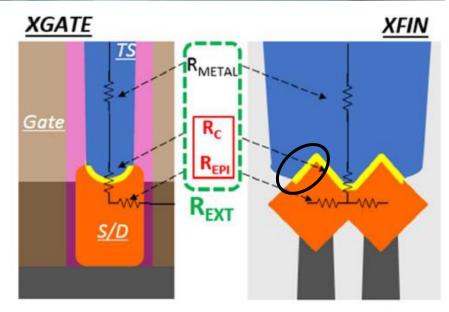

# Reducing $\rho_c$ for pMOS

#### At S/D metal interface need:

- High Active Dopant Concentration (N<sub>A</sub>)

- Minimal Defects / Lateral Uniformity (Φ<sub>R</sub>)

- Biaxial-strained SiGe S/D (Φ<sub>B</sub>, m\*)

- Increased [Ge] at S/D-contact interface (Φ<sub>R</sub>)

How do we accomplish this?

#### p-FinFET

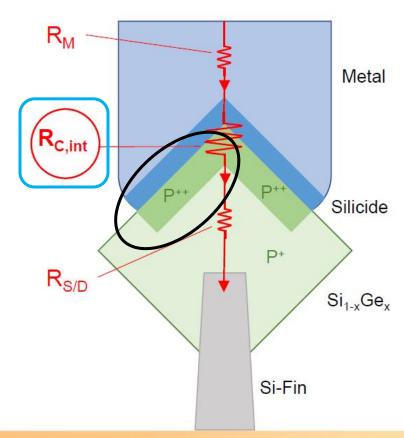

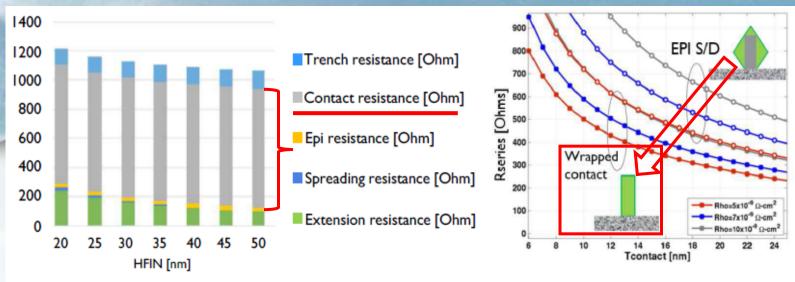

Figure 1. From (1). Left: N7 Series resistance simulations for a 4 fin PMOS for different parts of the device as function of the fin height. Right: N7 Series resistance simulations versus contact width for standard epi S/D contacts and wrapped contacts for different contact resistivities.

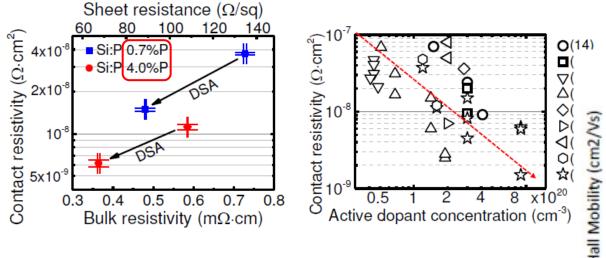

Figure 7. From (22). Left: MR-CTLM based contact resistivity versus sheet resis J.O.B. Telayers with different P concentrations (3·10<sup>20</sup> cm<sup>-3</sup> or 0.7% vs 2·10<sup>21</sup> cm<sup>-3</sup> or 4%). Sales & Tcontact metal. Right: Contact resistivity benchmark plot on n-Si indicating the importance of the active dopant concentration.

Rosseel et al., IMEC/ASM, ECS Oct 2016

**Solubility increases with Temp**

46

60

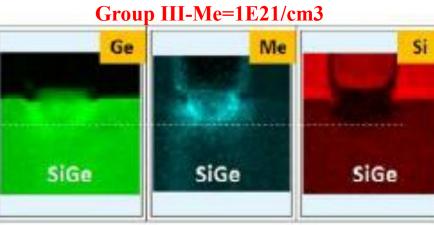

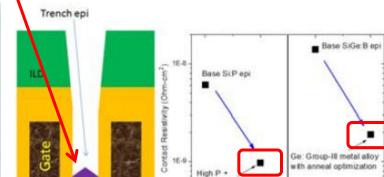

FinFET performance with Si:P and Ge:Group-III-Metal Metastable Contact Trench Alloys

O. Gluschenkov<sup>1</sup>, Z. Liu<sup>1</sup>, H. Niimi<sup>2</sup>, S. Mochizuki<sup>1</sup>, J. Fronheiser<sup>2</sup>, X. Miao<sup>1</sup>, J. Li<sup>1</sup>, J. Demarest<sup>1</sup>, C. Zhang<sup>1</sup>, C. Niu<sup>2</sup>, B. Liu<sup>2</sup>, A. Petrescu<sup>1</sup>, P. Adusumilli<sup>1</sup>, J. Yang<sup>1</sup>, H. Jagannathan<sup>1</sup>, H. Bu<sup>1</sup>, and T. Yamashita<sup>1</sup>

IEDM-2016 paper 2.7

IEDM-2016 paper 17.2

<sup>1</sup>IBM Research at Albany NanoTech, 257 Fuller Road, Albany NY 1220: <sup>2</sup>GLOBALFOUNDRIES Inc., 257 Fuller Road, Albany

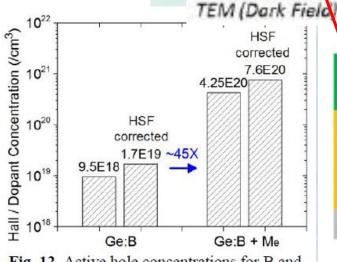

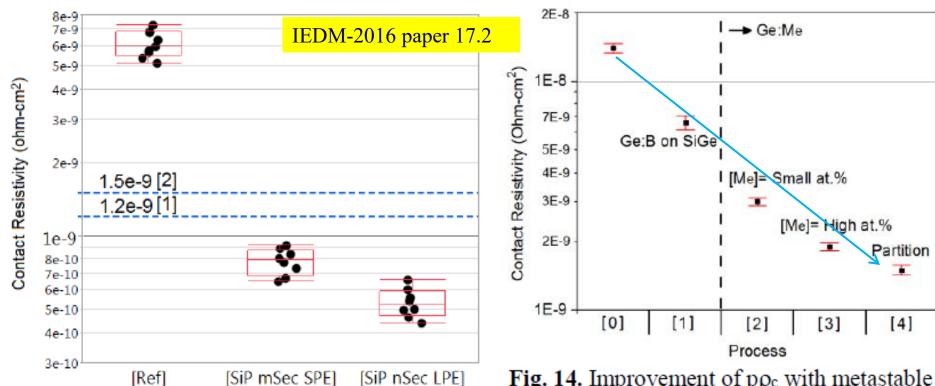

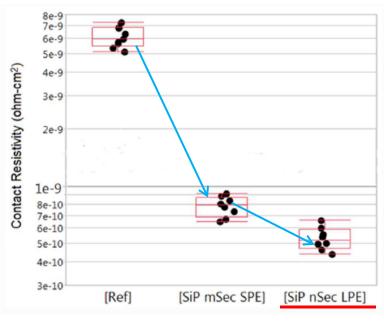

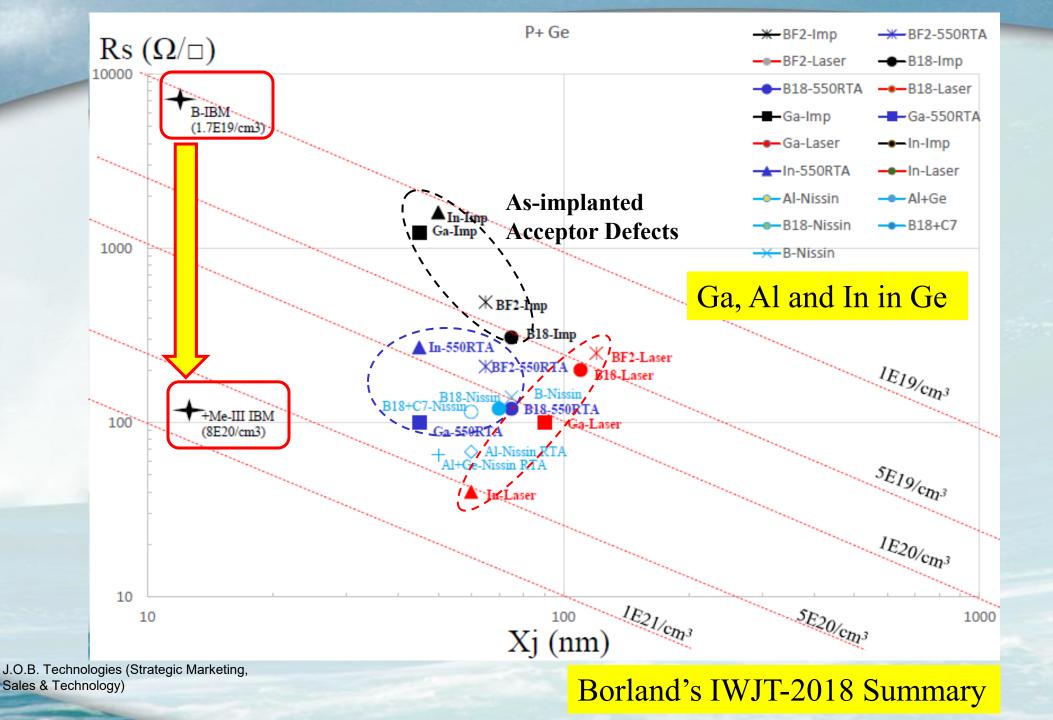

Abstract— We achieved mid-10<sup>-10</sup> Ω-cm<sup>2</sup> n-type S/D contact resistivity (nρ<sub>c</sub>) and 1.9x10<sup>-9</sup> Ω-cm<sup>2</sup> p-type S/D contact resistivity (pρ<sub>c</sub>) by employing laser-induced liquid or solid phase epitaxy (LPE/SPE) of Si:P and Ge:Group-III-Metal metastable alloys inside nano-scale contact trenches. The Ge:Group-III-Metal alloy allows for a metal-Ge Fermi level pinning effect to lower Schottky barrier height (SBH) while reducing both bulk and unipolar heterojunction resistances. Correspondingly, large R<sub>on</sub> reduction and I<sub>d</sub> gain have been realized in scaled n- and p-FinFETs with the contact length of less than 20nm.

SiGe

**Fig. 12.** Active hole concentrations for B and Group-III-Metal in Ge by Hall measurements. Group-III-Metal chemical concentration [Me] is ~1x10<sup>21</sup> cm<sup>-3</sup> while [B] is ~2x10<sup>19</sup> cm<sup>-3</sup>. Hall scattering factor (HSF) is 1.8.

B=2E19/cm3

Group III-Me=1E21/cm3

EDX (Elemental Mapping)

Fig. 23. Trench epi process simultaneously meets the ground ruleand  $\rho_c$  reduction upon implant and anneal optimization [16,17].

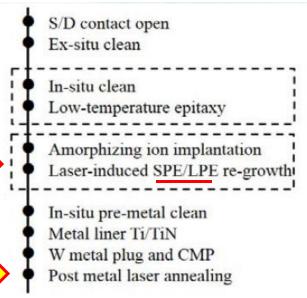

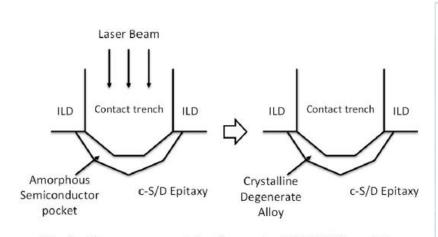

**Fig. 2.** Process flow for metastable alloy formation.

J.O.B. Te

Sales &

Fig. 5. Distribution of nρc extracted from nFinFET Kelvin probing, as shown in Fig. 3. Cases [Ref], [SiP mSec SPE], and [SiP nSec LPE] correspond to cases [a], [c], and [d] of Fig. 4, respectively. Data from references<sup>[1],[2]</sup> are shown by dotted lines.

Fig. 14. Improvement of pρc with metastable Ge: Group-III alloys. Case [0] is the SiGe:B reference. Case [1] is the Ge:B trench epitaxial layer. Cases [2]-[3] are Ge:B:Group-III-Metal metastable alloys where [Me] is above chemical solubility in Ge and [Me]case[3] is twice of [Me]case[2]. Case [4] is an upper bound estimate for metal-to-semiconductoralloy contact resistance of case [3].

They state that B has a low solid solubility of mid-E18/cm<sup>3</sup> in pure Ge which is opposite to what most in the industry believe! B Hall/Dopant activation level of only 1.7E19/cm<sup>3</sup> in Ge while a Group-III-Metal achieved 45x higher active hole concentration level of 8E20/cm<sup>3</sup> for an implanted chemical level of 1E21/cm<sup>3</sup>. Said there may be a mixing of the metal alloy or something,

#### **IBM Alliance IWJT-23**

#### 4. Conclusions

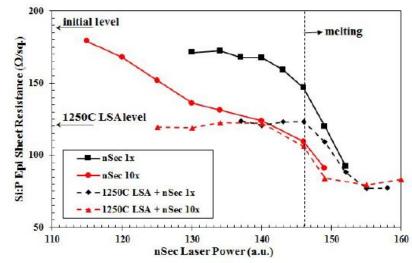

Millisecond and nanosecond laser annealing techniques have been explored for reducing FinFET external parasitic resistance. Millisecond high-temperature LSA has been effective in reducing n-type S/D bulk resistance. Low-temperature LSA SPE applied after an amorphizing contact ion implantation has results in a 6-fold reduction of  $nR_C$  and a 9-fold reduction of  $pR_C$  with corresponding transistor-level specific contact resistivities in sub  $10^{-9} \Omega$ -cm<sup>2</sup> range. Contact NLA LPE applied in place of LSA SPE provides an additional reduction for specific contact resistivities and can also be employed for melting and crystallizing the entire PFET SiGe S/D with a ~40% reduction of its resistance.

Fig. 3 Sheet resistance Rs of Si:P epitaxial film. "Initial" and "1250C LSA" levels indicate film Rs for as-grown and LSA-annealed at 1250°C. NLA "10x" is 10 consecutive "1x" anneals.

Fig. 4 Process concept for the contact SPE/LPE module.

Fig. 7 Transistor-level n-type specific contact resistivity.

#### Low Temp (Contact) Epi

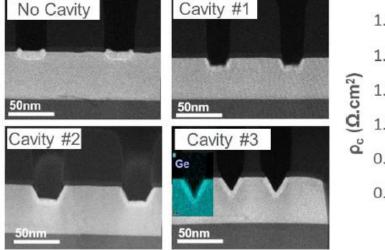

#### Contact area engineering / Cavity Shaping

| REQUIREMENTS        | LT p-Epi Status                                                                                                 | LT n-Epi Status                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Contact resistivity | <ul> <li>0.14 mΩ.cm at 400C</li> <li>Active [B] &gt;1.5E21 at./cm<sup>3</sup>;</li> <li>Ge% = 50-70%</li> </ul> | <ul> <li>0.22 mΩ.cm at 400C</li> <li>1.1E21 at./cc record Phos activation (~50% active)</li> <li>Contact resistivity (under testing)</li> </ul> |

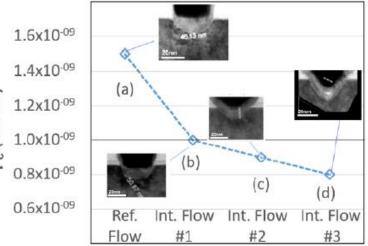

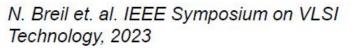

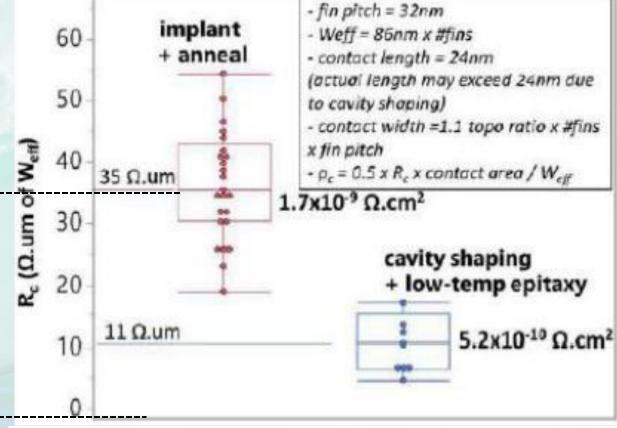

- Increase in the contact area  $\rightarrow$  reduces the contact resistivity

- Various cavity shapes from a "U" to a "V are tested

- A deeper cavity (#3) increases the contact area, thus reducing the contact resistance and brings the contact closer to the channel

- ρ<sub>c</sub> as low as 5.2x10<sup>-10</sup> Ω.cm<sup>2</sup> demonstrated on FinFET structures using cavity shaping with LT Epi (3x improvement from traditional implant techniques)

# Epi + Implant + SPE/LPE Versus Lt-Epi With Cavity

# Etch

High 75% SiGe p+S/D cap gives lowest contact resistance after SPE of **5E-10**  $\Omega$ -cm<sup>2</sup>

LT Epi with cavity active  $B = 1.5E21/cm^3$  and  $P = 1.1E21/cm^3$  for **5E-10**  $\Omega$ -cm<sup>2</sup> contact resistance

H. Arora et al., Applied Materials presentation at Northern California **AVS-WCJUG meeting, Dec 2024**.

O. Gluschenkov, Y. Sulehria, S. Mochizuki and K. Brew, **IWJT-2023**, paper S6-1, p. 150.

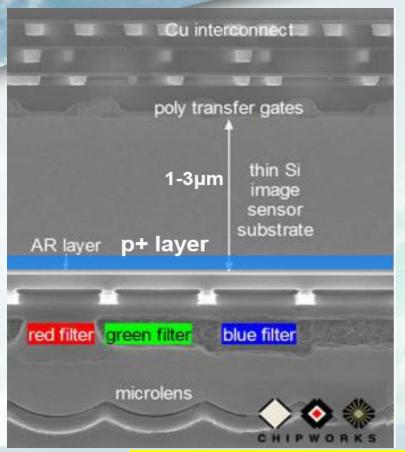

# Backside B Laser Melt Annealing For Image Sensor

K. Huet et al., IEEE/RTP-2009, paper #14

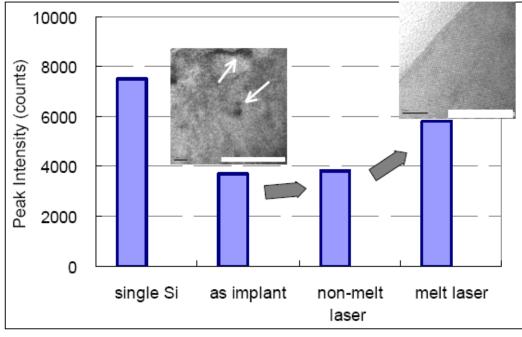

# 0.9um Pixel CMOS Imager Sensor Technology with Backside Illumination

Figure 4. Photoluminescence and TEM study of laser anneal (higher peak intensity means better Si crystal quality)

TSMC, IEDM-2010, paper 14.1

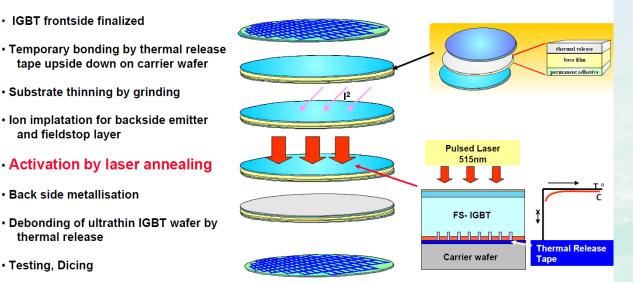

#### **Power Devices IGBT**

IGBT frontside finalized

Laser Annealing of Power Devices IEEE-RTP 2007

Substrate thinning by grinding

Ion implatation for backside emitter and fieldstop layer

tape upside down on carrier wafer

Activation by laser annealing

- Back side metallisation

- Debonding of ultrathin IGBT wafer by thermal release

- · Testing, Dicing

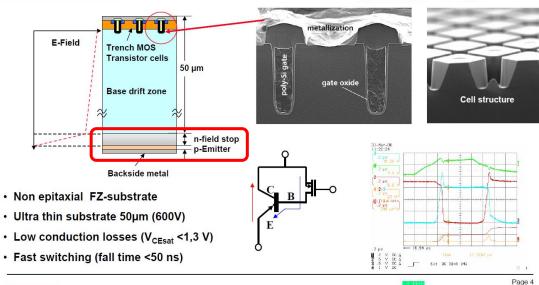

**Power Devices IGBT**

Laser Annealing of Power Devices IEEE-RTP 2007

**SEM** cross sections Trench IGBT

JENOPTIK

ININIOVAVENT CMALL

Fraunhofer

Laser Annealing of Power Devices IEEE-RTP 2007

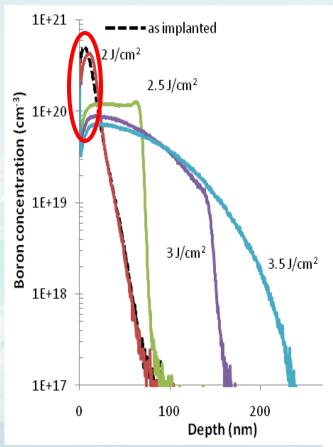

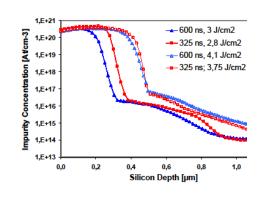

#### Results

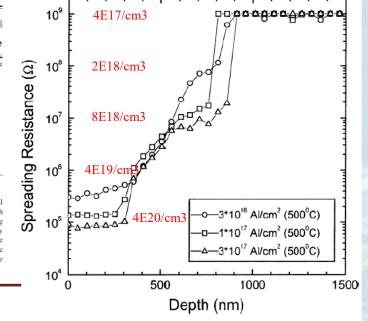

**B-Profiles: SIMS and SRP**

- SIMS profiles "as implanted" and laser annealed (3 J/cm<sup>-2</sup>) show similar characteristics

- Slight diffusion is observed in the tail region for laser annealed samples

- SRP profiles indicate high degree of dopant activation > 80% laser annealed: 3 J/cm<sup>-2</sup>, 3,2 J/cm<sup>-2</sup>

- Pulse length: 600ns

#### 1,E+22 Bor 30keV, 5 x 1015cm-2 1,E+21 1,E+20 1,E+19 SRP B 3,0J/cm2 . . . SRP B 3,2J/cm2 1,E+18 SIMS B as implanted 1,E+17 - SIMS B 3,0J/cm2 0,05 0,10 0,15 0,25 0,35 0,20

Silicon Depth [µm]

Laser Annealing of Power Devices IEEE-RTP 2007

#### Annealing of Power Devices IEEE-RTP 2007

Page 5

Melting front propagates up to 0,5µm

#### Results

**B-dose variation**

- Boron SRP depth profiles for different ion implantation dose values

- · Increased absorption due to amorphisation of Si for Boron dose values > 1 1015 cm-3

- Activation of Phosphorous decreased for high Boron doses

Fraunhofer Institut Siliziumtechnologie Page 17

Fraunhofer Institut Siliziumtechnologie

Fraunhofer Institut Siliziumtechnologie Page 21

#### Laser Sources Available for Material Processing High - Power Laser Sources ... CO<sub>2</sub>-Laser **Excimer-Laser** 532 1064 266 Nd:YAG-Laser 808, 880, 940,980,1060 1480, 1550 Diode-Laser 1030, 1050, 1080, 1550 Lithography Fiber-Laser Ablation · Inkjet nozzle drilling, · Micromachining of filters, Ablation graves, pores, structures Micromachining Annealing Annealing of solar cells, filters Welding, soldering Annealing · Silicon in TFT-Displays Welding, soldering Annealing Cutting Semiconductor materials Drilling Drilling Cutting Medical Applications Drilling Medical Applications Printing technology ... and its Application in Material Processing

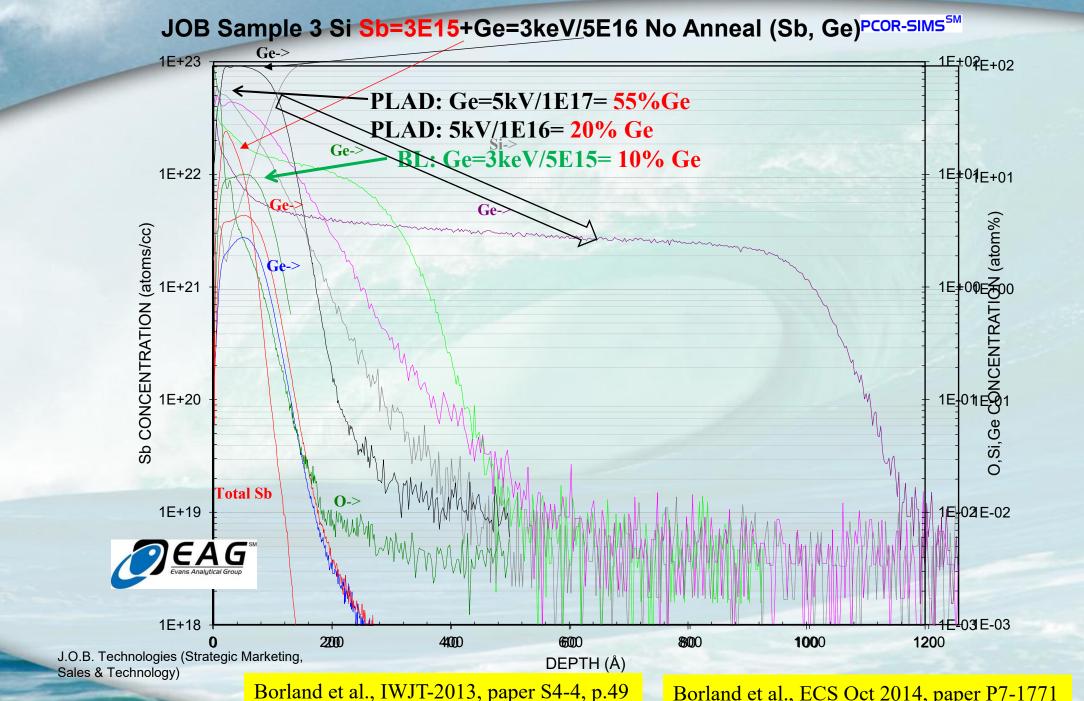

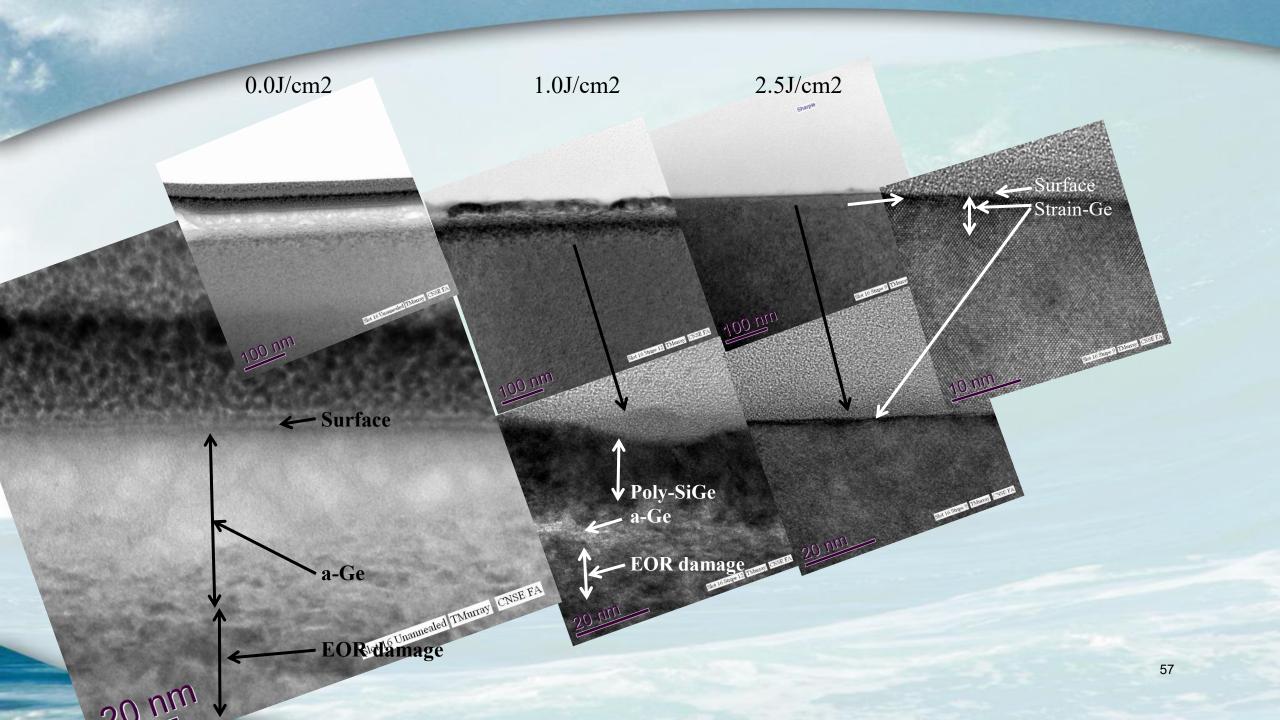

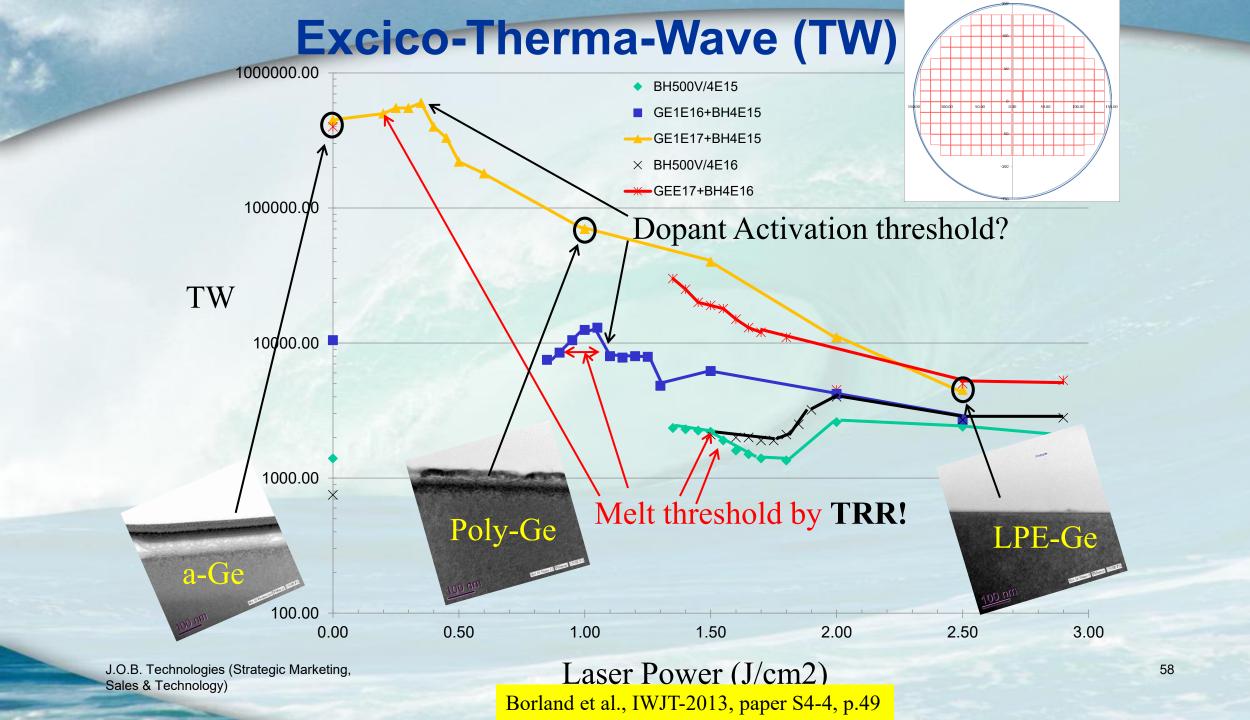

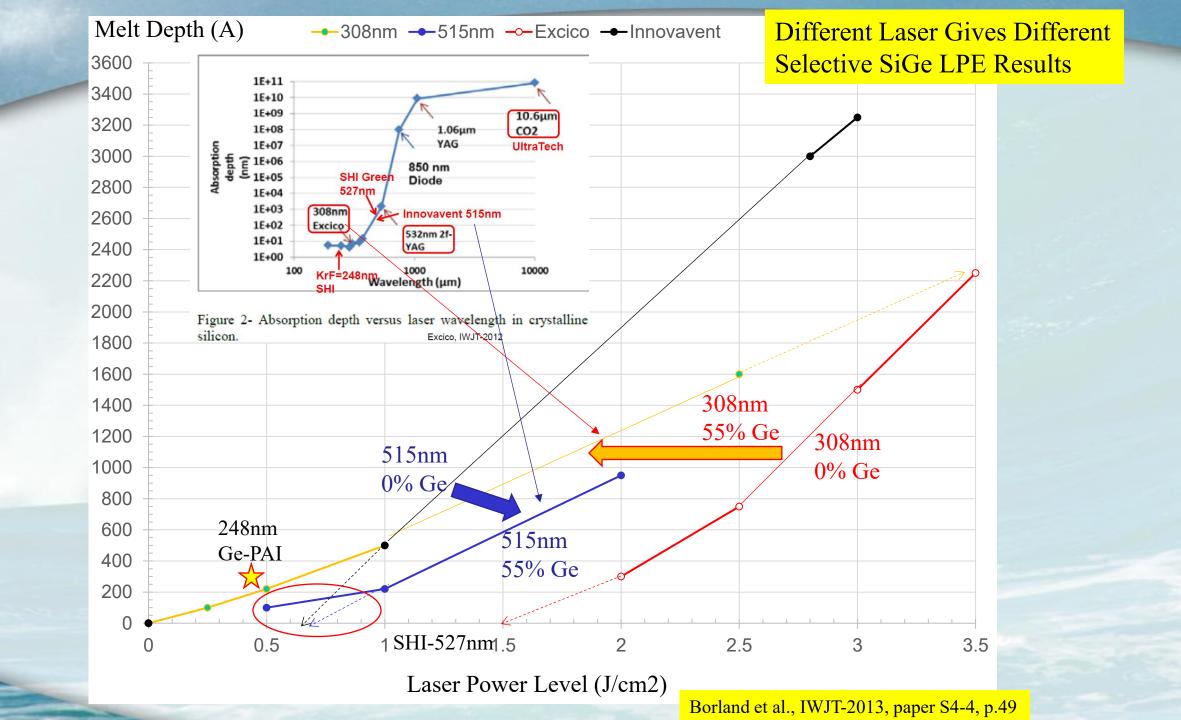

# Formation By Liquid Phase Epitaxy (LPE) Using Ge+B Plasma Ion Implantation And Laser Melt Anealing

**IWJT June 6, 2013**

JOB Technology, Micron, Innovavent, Excico, KLA-Tencor, CNSE, EAG & UCLA

Ge 3keV at 1E16/cm2 (Ge=20%) & 1E17/cm2 (Ge=55%) B2H6 500V at 4E15/cm2 & 4E16/cm2

Ge+B Plasma Implanted Wafers Provided by Micron Laser Melt Annealing Provided by Innovavent & Excico

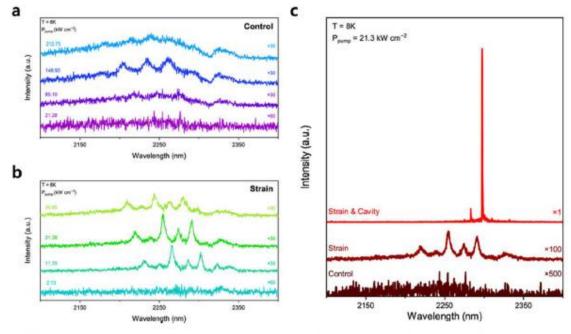

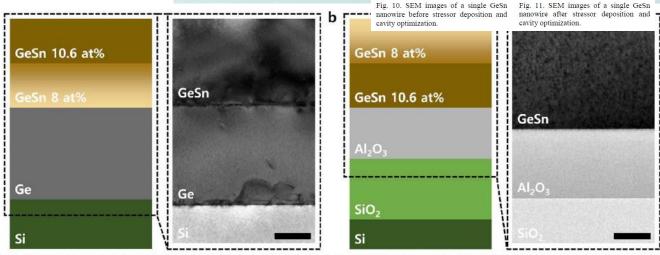

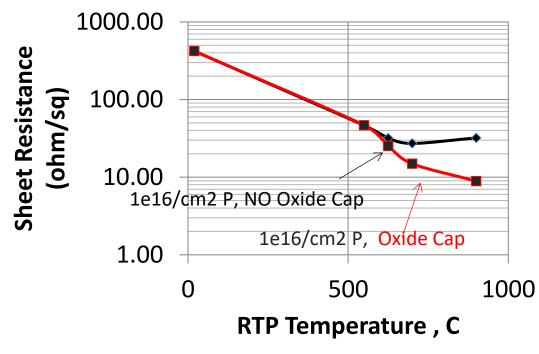

#### GeSnOI Lasers for Laser-Integrated Photonic Chips

IEDM-2025 Paper 41.8

G. Yu<sup>1</sup>, H. Joo<sup>2</sup>, J. Liu<sup>3</sup>, M. Chen<sup>2</sup>, Y. Kim<sup>2</sup>, S. Assali<sup>4</sup>, C. Sirtori<sup>3</sup>, Y. Todorov<sup>3</sup>, O. Moutanabbir<sup>4</sup>, and D. Nam<sup>1\*</sup>

<sup>1</sup>KAIST, Daejeon, Korea, <sup>2</sup>Nanyang Technological University, Singapore,

<sup>3</sup>École Normale Supérieure, France, <sup>4</sup>École Polytechnique de Montréal, Canada, \*E-mail: dwnam@kaist.ac.kr

Abstract—The rapid integration of artificial intelligence into our everyday lives has significantly increased the demand for high-speed and energy-efficient data transmission within data centers. Co-packaged optics has emerged as a promising approach, allowing optical interconnects to surpass the limitations of conventional electrical interconnects. However, the absence of efficient CMOS-compatible on-chip lasers remains a major challenge. In this paper, we review recent advancements in GeSn-based laser technology, highlighting their potential to overcome this critical bottleneck.

Also, critical advancements | a electrically pumped GeSn las wave (CW) electrically pumped SiGeSn/GeSn multiple quantun

Continuous efforts are under performance metrics such as temperature, and efficiency functionalities such as dynam ensuring GeSn lasers continue blocks for next-generation phot

Fig. 12. **a,** Emission spectra for a control nanowire. **b,** Emission spectra for a strained nanowire. **c,** Emission spectra comparison between 3 samples: control, strained, and strained&cavity optimized samples.

Fig. 1. Cross-sectional schematics of the material stack for the **a**, as-grown GeSn and **b**, GeSnOI substrates. Scale bars, 450 nm **a**, 400 nm **b**.

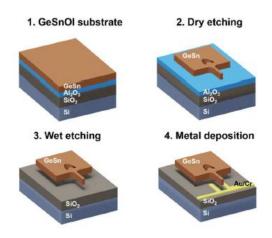

Fig. 2. Fabrication process of a GeSn oscillator.

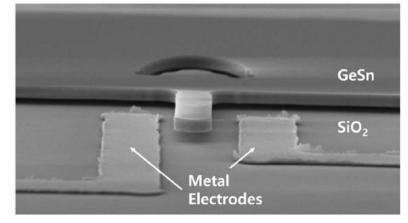

Fig. 3. Scanning electron microscopy (SEM) image of the fabricated GeSn nanomechanical oscillator.

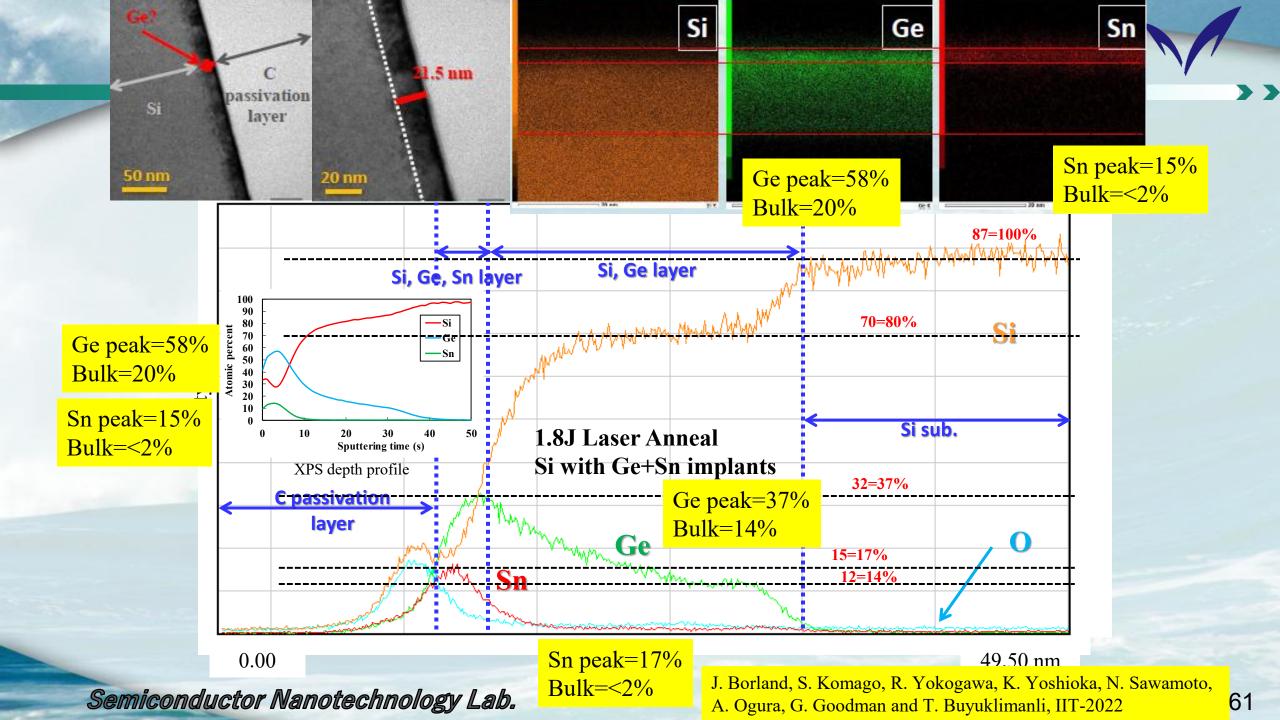

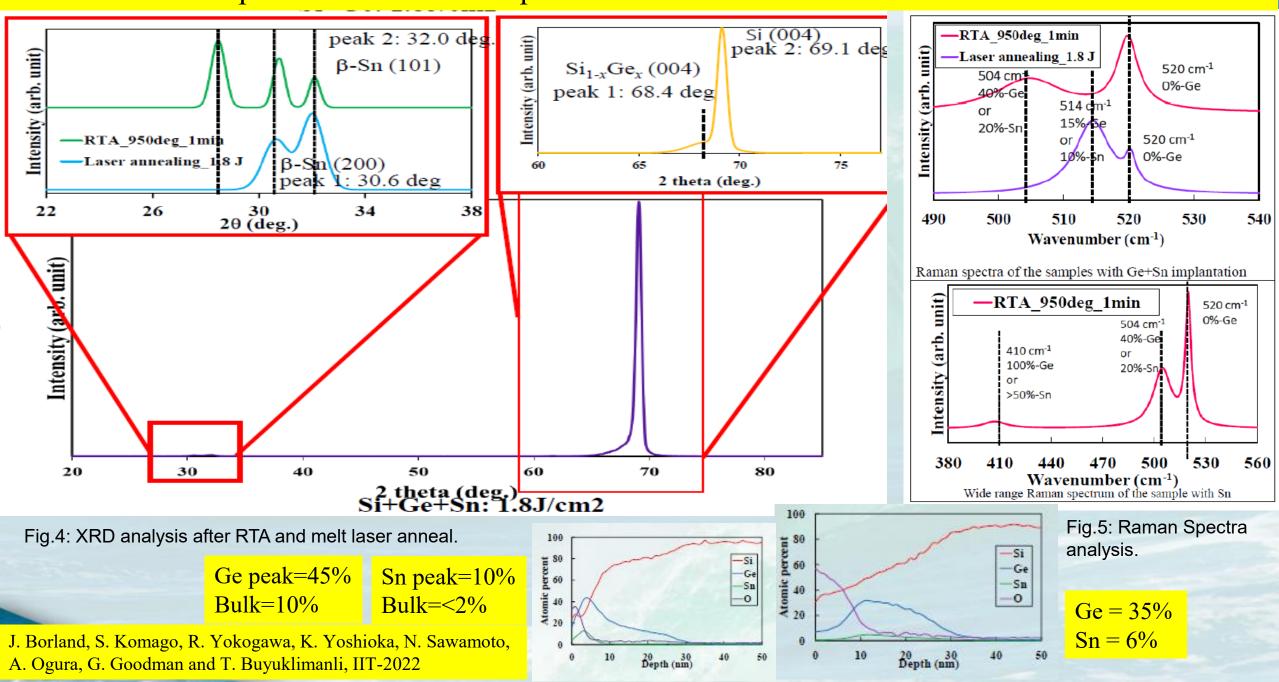

#### Si with Ge+Sn implantation 0.54% compressive strain after 1.8J laser and 1.80% after 950C RTA

# Ultralow-power, High-speed Integrated Si Photonic Switch Enabled by III–V/Si Hybrid MOS Optical Phase Shifters

IEDM-2025 Paper 21.5

T. Akazawa<sup>1</sup>, R. Tang<sup>1</sup>, H. Tang<sup>1</sup>, M. Okano<sup>2</sup>, N. Matsuda<sup>3</sup>, K. Toprasertpong<sup>1</sup>, S. Takagi<sup>1</sup>, and M. Takenaka<sup>1</sup> Department of Electrical Engineering and Information Systems, The University of Tokyo, Japan, email: akazawa@mosfet.t.u-tokyo.ac.jp

<sup>2</sup>National Institute of Advanced Industrial Science and Technology (AIST), Ibaraki, Japan,

<sup>3</sup>Research Institute of Electrical Communication, Tohoku University, Miyagi, Japan

Conventional switch Si photonic switch Input optical signal Input optical signal Electrical signal Si photonic Electrical switch switch Output Optical transmitter optical signal No O-E-O conversion Requires O-E-O conversion Low energy efficiency High energy efficiency Significant signal delay Low latency Switch Switch Switch Switch Switch Switch Switch Switch Optical fiber Servers in data center

Schematic switches for intra-server communication in data centers. In a conventional electrical switch, input optical signals are first converted to electrical signals for switching, and then reconverted back to optical signals. This optical-electrical-optical (O-E-O)conversion results in low energy efficiency and latency. Optical switches eliminate these processes, enabling energy-efficient and fast signal routing and making suitable for them managing the massive data traffic in data centers.

# Silicon Photonics Modulators and Photodetectors for Next-Generation CPO and Optical I/O

IEDM-2025 Paper 41.3

J. Van Campenhout<sup>1\*</sup>, M. Kim<sup>1</sup>, C. Coughlan<sup>1</sup>, A. Shahin<sup>1,2</sup>, Z. Ahmad<sup>1</sup>, C. Bruynsteen<sup>3</sup>, L. da Silva<sup>3</sup>, N. Singh<sup>3</sup>, D. Malik<sup>1</sup>, G. Muliuk<sup>1</sup>, D. Yudistira<sup>1</sup>, J.R. Vaskasi<sup>2</sup>, S. Jakanadan<sup>1</sup>, G. Lepage<sup>1</sup>, C. Marchese<sup>1</sup>, S. Kaushik<sup>1</sup>, R. Loo<sup>1</sup>, Y. Shimura<sup>1</sup>, H. Kobbi<sup>1</sup>, R. Magdziak<sup>1</sup>, H. Sar<sup>1</sup>, D. Bode<sup>1</sup>, S. Bipul<sup>1</sup>, P. Carolan<sup>1</sup>, M. Agati<sup>1</sup>, D. Van Thourhout<sup>1,2</sup>, P. Verheyen<sup>1</sup>, M. Chakrabarti<sup>1</sup>, P. De Heyn<sup>1</sup>, D. Velenis<sup>1</sup>, P. Ossieur<sup>1,3</sup>, F. Ferraro<sup>1</sup>, and Y. Ban<sup>1</sup>

<sup>1</sup>imec, Leuven, Belgium, <sup>2</sup>Photonics Research Group, Ghent University, Ghent, Belgium, <sup>3</sup>IDLab, imec-Ghent University, Ghent, Belgium, \*email: jvcampen@imec.be

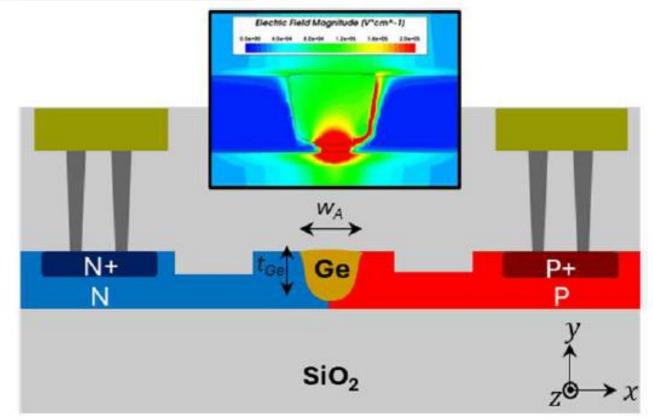

Fig. 14. Ge Photodetector: cross-section schematic and electric field simulation at -2V bias

Fig. 15. Ge Photodetector: cross-section TEM image

# Trumble, Bell Labs, 1959

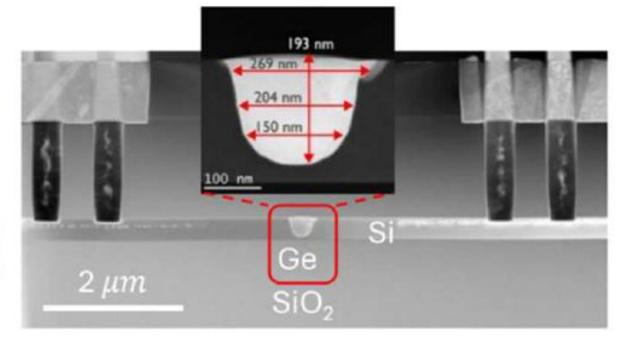

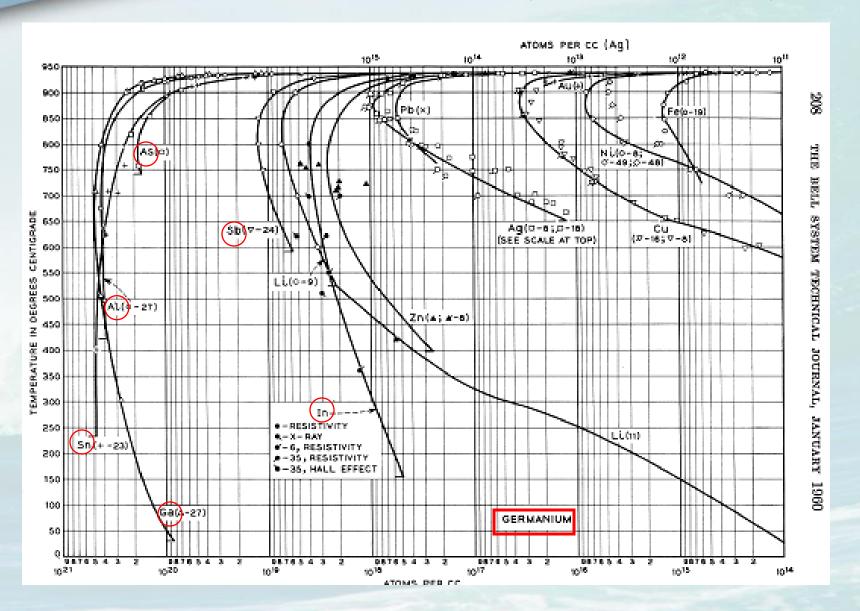

#### Implant Dopant Activation Comparison Between Silicon and Germanium

Paul T. Konkola and John O. Borland. Advanced Integrated Photonics, Honolulu, HI, USA. <a href="mailto:konkola@apichip.com">konkola@apichip.com</a> (808) 380-4038.

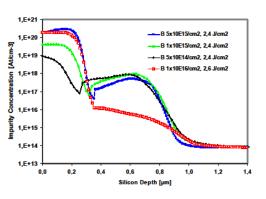

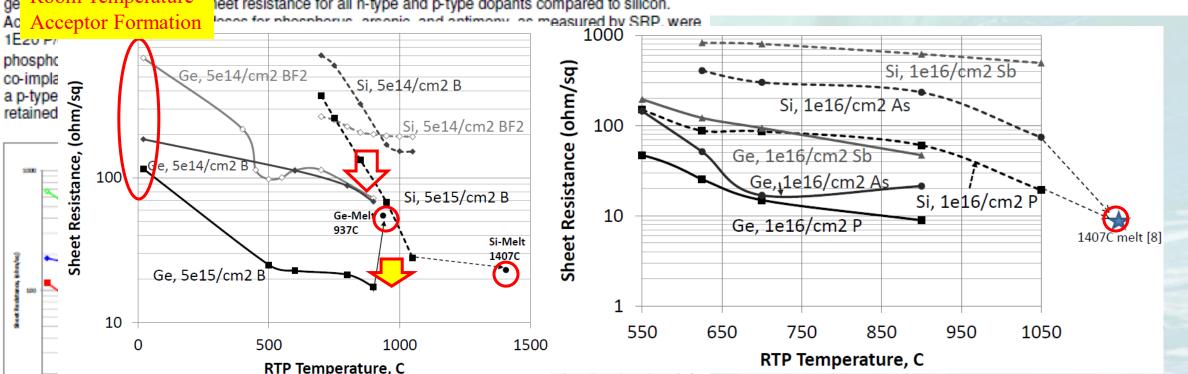

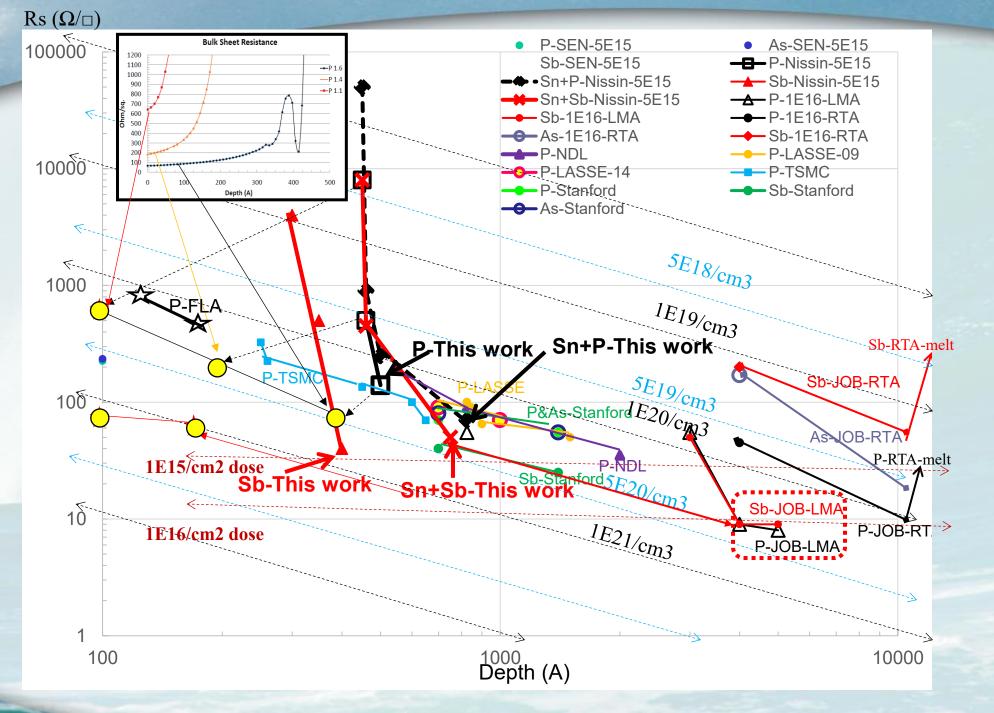

We present experimental results for the activation of various p+ and n+ implanted dopants in germanium and silicon. Germanium samples were rapid thermally annealed from 550 °C to 950 °C and silicon samples were annealed from 700 °C to 1050 °C for 10 seconds. Laser melt annealing was also conducted. P-type doping by Boron and BF<sub>2</sub> and n-type doping by phosphorus, arsenic, antimony, and phosphorus plus co-doping with fluorine, carbon, or Sb are compared. Several observations are made for p-type and n-type activation that are unique to germanium. Room temperature activation (no anneal) shows higher activation levels for boron at higher dose. The amorphization of the germanium by BF<sub>2</sub> leads to higher room temperature sheet resistance. At 5E15 B/cm<sup>2</sup>, Boron is fully active in germanium at RTA temperatures from 600 °C to 900 °C. Meanwhile, the activation of boron in silicon was about 5x less than germanium at 900 °C as a result of silicon's lower solid solubility at this temperature. Laser melt activation of Boron showed deactivation caused by the melt. For phosphorus implanted germanium, we obtain the properature of the second cap when annealing above 625 °C. Additionally, seet resistance for all n-type and p-type dopants compared to silicon.

# **Summary Of Dopant Activation In Si-vs-Ge**

- P-Type Dopant (B & BF2)

- Room temperature activation (acceptor formation)

- Higher dose 5E15 vs 5E14 (acceptor level ~1E14/cm2 or 1E19/cm3)

- Amorphization by BF2 reduces EOR damage and acceptor formation level

- C implant also produces 1E19/cm3 acceptor level

- B Fully active in Ge at 500C

- 5x lower Rs may be related to solid solubility differences of B in Ge versus Si as well as 3x higher hole mobility in Ge

- B deactivation observed with Ge-melt laser annealing

- N-type Dopant (P, As & Sb)

- We observed 3x lower Rs with a surface oxide cap when annealing Ge implanted with P above 625C!

- Contrary to others we observed lower Rs for all n-dopants in Ge compared to Si! P best then As followed by Sb. Could Sb implant damage create more acceptor levels therefore higher Rs due to dopant compensation?

- Lower P-dose (2E15) fully active at 550C, 1E16 P-dose requires >900C.

- Examined C, F and Sb co-implant effects,

- C-defects creates p-type acceptor compensating dopants around 1E19/cm3 and no C-diffusion

- No difference with F, after RTA SIMS shows F all gone with a peak at the Ge/Si interface.

- Sb degrades high dose P activation but improves low dose P activation at the higher RTA temperatures.

- Si-cap improves P activation in Si at 625C and 900C anneal shows minimal P diffusion into Ge and no Ge-epi threading dislocations! This is BEST solution for nMOS as proposed in SST July 2005 for planar HK/MG-last and for FinFET in March 2012

#### N<sup>+</sup> Ge

U3000402001D1

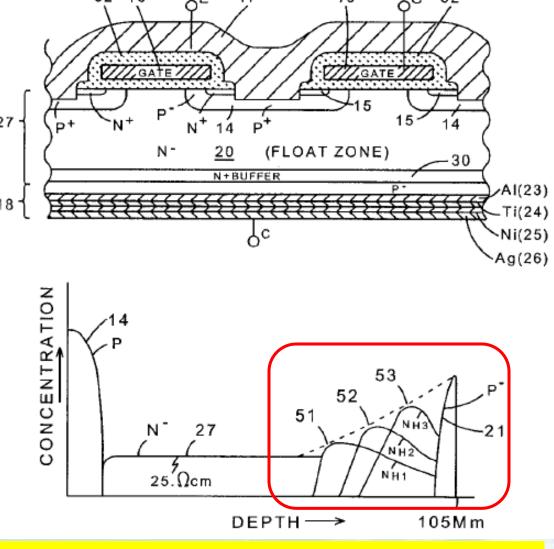

### (12) United States Patent Francis et al.

(10) Patent No.: US 6,482,681 B1

(45) Date of Patent:

Nov. 19, 2002

- (54) HYDROGEN IMPLANT FOR BUFFER ZONE OF PUNCH-THROUGH NON EPI IGBT

- Inventors: Richard Francis, Manhattan Beach; Chiu Ng, El Segundo, both of CA (US)

- (73) Assignee: International Rectifier Corporation, El Segundo, CA (US)

#### FOREIGN PATENT DOCUMENTS

6318706 11/1994

JP

#### (57) ABSTRACT

An IGBT is formed in a thin (less than 250 microns thick) float zone silicon wafer using a hydrogen implant to form an N<sup>+</sup> buffer layer at the bottom of the wafer. A weak anode is formed on the bottom of the wafer. A single hydrogen implant, or a plurality of hydrogen implants of progressively shallower depth and increasing dose can be used to form the implant in a diffused float zone wafer. The process may also be used to form an N<sup>+</sup> contact region in silicon to permit a good ohmic contact to the silicon for any type device.

Infineon Purchased IRC. IGBT Replaced Phos implant with MeV H+ implant in Europe and China pre-COVID! Also, using Laser Melt LPE

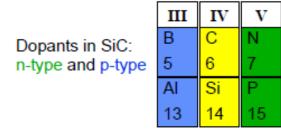

#### SiC doping

B+

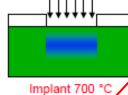

Epitaxy 1400-1600 °C Diffusion > 1800 °C Implant 700 ° Anneal 1200-170

Epitaxy allows uniform doping entire wafer, for selective doping we use diffusion or implantation.

Dopants in SiC: Al and B for p, N and P for n

For silicon diffusion can be performed at temperatures below 1200 C, which allows the successful use of silicon dioxide masks.

Solid state diffusion of dopants into SiC needs temperatures of 1800 C and higher. Graphite masks may be one possibility.

Ion implant causes damage, which is difficult to remove. High T during implant (700 C) and high T anneal (1200-1700 C) is necessary.

One advantage for SiC is the low diffusion. A narrow profile stays narrow, see figure.

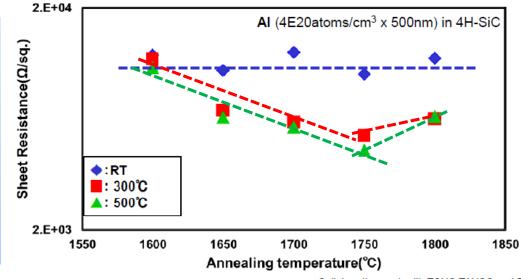

$\hfill \square$  Rs with heated ion implantation after several annealing conditions

Collaboration work with TOYO TANSO and EpiQuest Si-vapor ambient anneal without carbon capping

SRP (High Doping)

4 epi-layer SiC with different levels of doping concentration

SiC epi

4 p-type layers

Depth [um]

We got lower Rs with higher substrate temperature at higher annealing temperature over 1650 °C.

Dopant Concentration [cm<sup>-3</sup>,

1E+16

Applied Surface Science 184 (2001) 209-213

applied surface science

Spreading resistance measurements on nanocrystalline SiC produced by ion beam induced crystallisation

K.N. Madhusoodanan, V. Heera\*, D. Panknin, W. Skorupa

Forschungszentrum Rossendorf, P.O. Box 510119, D-01314 Dresden, Germany

#### Abstrac

Ion beam induced crystallisation (IBIC) of preamorphised surface layers of 6H–SiC has been stimulated by high dose Al implantation  $(0.3-3\times10^{19}~{\rm cm}^{-2})$  at elevated temperatures (300–500 °C). Randomly oriented 32 C–SiC nanocrystals with diameters between 2 and 25 nm are formed depending on the implantation parameters as proved by XRD and XTEM. Spreading resistance measurements have been performed at bevelled as-implanted and annealed (1500 °C, 10 min) samples in order to study the electrical behaviour of the Al acceptors in the nanocrystalline layer. Reference experiments have been carried out on single crystalline 6H–SiC wafers implanted at the similar conditions. It has been found that in the as-implanted state Al doped fine granular SiC has much lower spreading resistance than the corresponding single crystalline SiC. Only minor differences have been observed between the nano- and single crystalline samples after annealing. © 2001 Published by Elsevier Science B.V.

# **CMOS SOS-Epi Using Double Amorphous SPE 1983**

Microelectronics Journal

Volume 14, Issue 6, November-December 1983, Pages 5-12

#### A low-leakage VLSI CMOS/SOS process with thin epi layers

J.Y. Lee, D.C. Mayer, P.K. Vasudev

Hughes Research Laboratories, 3011, Malibu Canyon Road, Malibu, CA 90265, USA

A new VLSI process was successfully developed for short-channel CMOS/SOS circuits on thin 0.3μm epi layers. Two kinds of thin epi material were used. The first was grown by a standard CVD process, while the second was prepared by a double solid phase epitaxial regrowth (DSPE) technique. CMOS/SOS ring oscillators with effective channel lengths ranging from 0.7 to 1.3μm were fabricated. Leakage currents below 3.0pA/μm were achieved on both n-channel and p-channel devices. The DSPE material showed improvement in both mobility and speed.

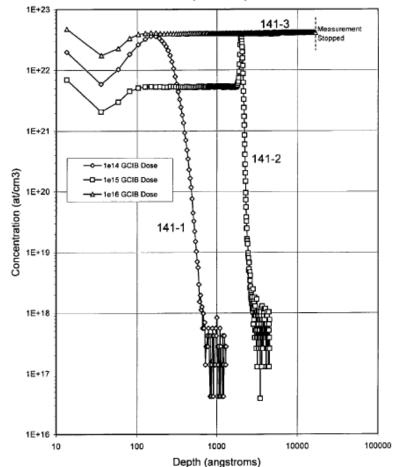

# (12) United States Patent Borland et al.

- (54) METHODS OF FORMING DOPED AND UN-DOPED STRAINED SEMICONDUCTOR MATERIALS AND SEMICONDUCTOR FILMS BY GAS-CLUSTER-ION-BEAM IRRADIATION AND MATERIALS AND FILM PRODUCTS

- (75) Inventors: John O. Borland, South Hami (US); John J. Hautala, Bever (US); Wesley J. Skinner, And (US); Martin D. Tabat, Nashı (US)

- (73) Assignee: TEL Epion Inc., Billerica, M.

US 7,259,036 B2

Aug. 21, 2007

See application file for complete search history.

(56) References Cited

(10) Patent No.:

(45) Date of Patent:

Germanium Film Growth on Silicon Substrate 30kV, 5%  $GeH_4$  in Ar

J.O.B. Technologies (Strategic Marketing, Sales & Technology)

#### **Outline**

- Epitaxial Doping: Solid Phase Epitaxy (SPE), Liquid Phase Epitaxy (LPE) and Gas/Vapor Phase Epitaxy (VPE) or Chemical Vapor Deposition (CVD)

- 1980s (2um to 0.5um Node):

- 1990s → Ultra Shallow Junction (USJ) Formation for S/D Extension.

- 2000s (130nm to 20nm Node)

- 2010s→ 3-D FinFET (22nm to 7nm Node)

- 2020s (5nm to 10A Node)

- Summary:

- VPE/CVD, LPE and SPE doping techniques

- Si, SiGe, Ge and SiGeSn

- LPE for Image Sensors and Power Devices

- SiC-Epi SPE lessons learned form 1980s SOS-Epi?