# Improved CMP processes through architecture & design optimization

Anke Hanisch<sup>1</sup> Sanghamitra Ghosal<sup>1</sup> Jinji Luo-Hofmann<sup>1</sup> Max Weinhold<sup>1</sup> Imme Ellebrecht<sup>2</sup> Knut Gottfried<sup>1,2</sup>

<sup>1)</sup> Fraunhofer ENAS, Technology Campus 3, 09126 Chemnitz, Germany

<sup>2)</sup> ErzM-Technologies UG, Technology Campus 1, 09126 Chemnitz, Germany

Dr. Knut Gottfried

Imme Ellebrecht

AVS Northern California Chapter

Joint User Group Meeting

# Outline

Background

Example IR imager

Hybrid bonding

Reminder ICPT 2024

Fraunhofer ENAS TECHNISCHE UNIVERSITÄT

Seite 2 23.08.24

#### Background

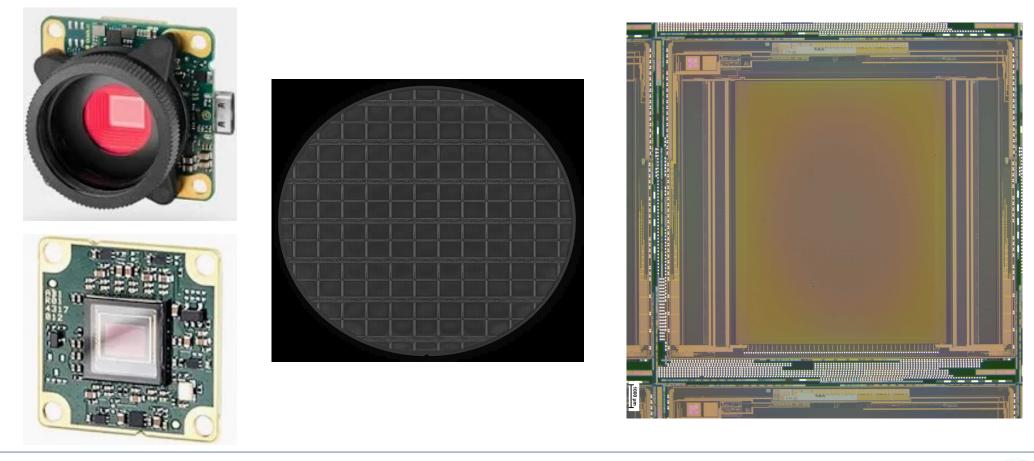

Wafer level integration concepts as needed for:

- CMOS imagers

- IR imagers (bolometer)

- Micro displays for VR / AR applications

- Hybrid ICs (combining devices from different technologies)

Fabrication of such devices may require several CMP steps, depending on specific fabrication technology

- Oxide / insulator CMP

- Metal CMP (Cu/barrier)

- Backside CMP

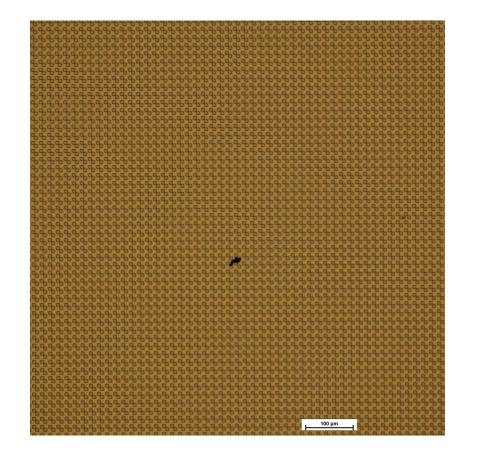

100 µ m

o 1Dot

Sony OLED Displays © Sony

Micro OLED Display © VECTED GmbH

Canon CMOS Image Sensor 13272H x 9176V © Canon

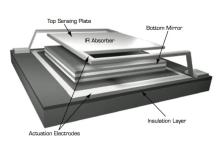

#### **Device characteristics**

- High vertical integration level (wafer level integration)

- Integration on-top-of-CMOS (e.g. IR imagers)

- Hybrid wafer bonding (e.g. micro displays, hybrid ICs)

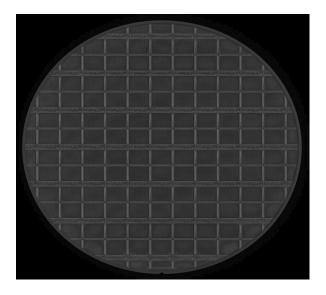

- Rather large dies several mm to inch size

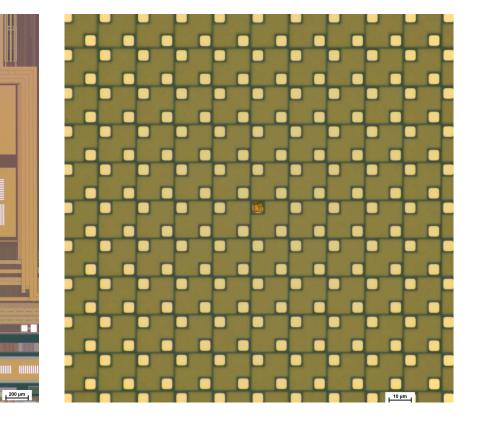

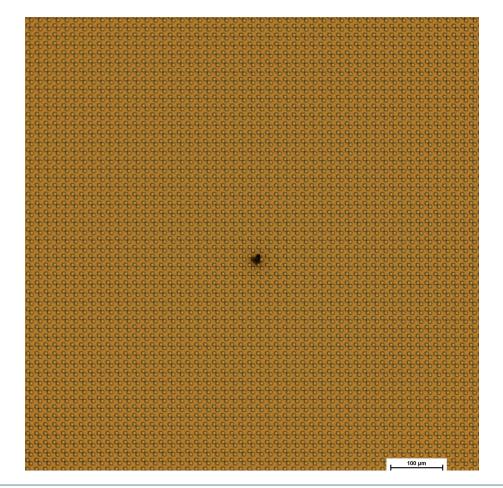

- Pixel arrays / pixel areas

- Pixels size / pitch in lower μm range

- Very uniform pattern density and size Size

- Very uniform pitch ③

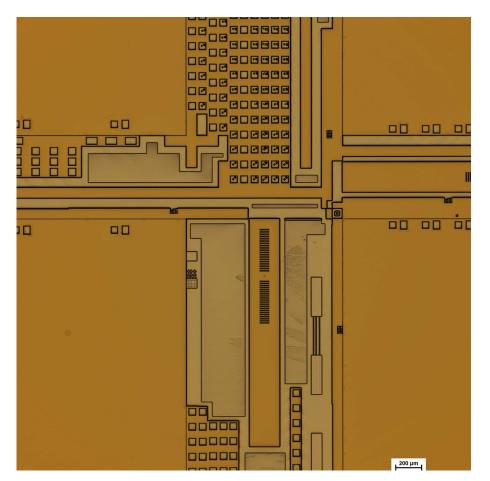

- Surrounding circuitry 😕

- Dicing lanes ☺

IR-imager schematic pixel cross-section

Micro display schematic pixel cross-section

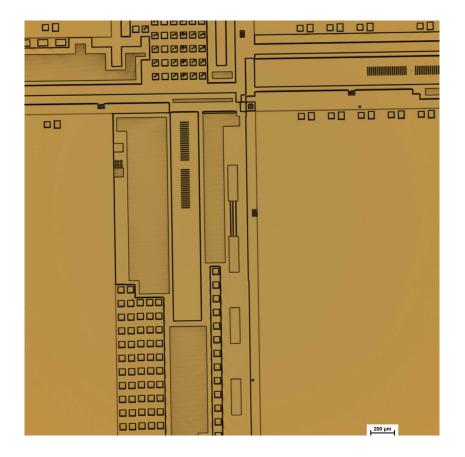

IR-imager - dicing lane and circuitry

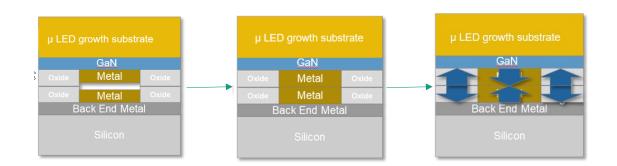

#### LED Substrate

CMOS Wafer

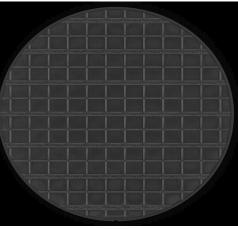

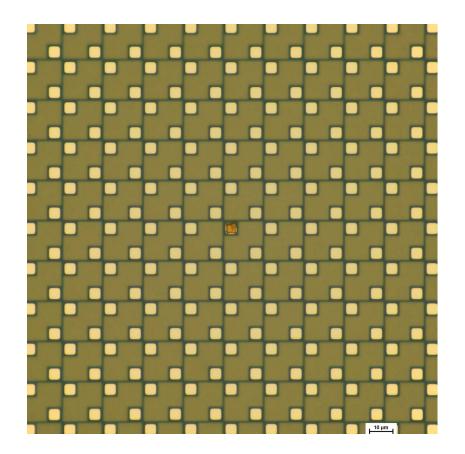

IR-imager – pixel array

#### CMOS backplane for IR-mager

#### **Process requirements**

- Good uniformity: within die, within wafer, wtw

- Low remaining topography

- Low roughness

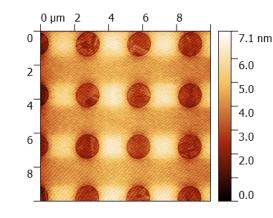

#### Specific to hybrid bonding applications

- Oxide roughness: same as direct bonding < 0.5 nm</p>

- Oxide rounding:  $< 1 \text{ nm} / \mu \text{m}$

- Cu roughness in lower nm range

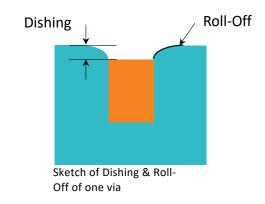

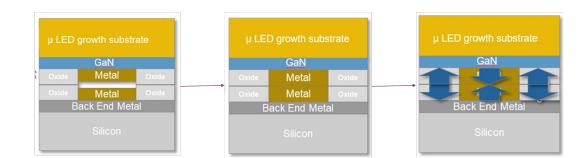

- Dishing: no rule of thumb, depends on via size and temperature budget (typ. 1 nm ... 10 nm)

- Low remaining long-range topography (typ. less than 10 nm)

- Trenching: as low as possible (undesired effect)

#### What's the meaning for CMP?

- Perfect process control

- Process parameters / process window

- Endpoint

- Consumables

- Process strategy

- Over polish

- Selective / non-selective

- Dishing protrusion dishing

- Fast and reliable inline metrology

- Design (layout, architecture) adaption & optimization

- Design for functionality

- Design for fabrication

# Outline

Background

Example IR imager

Hybrid bonding

Reminder ICPT 2024

Fraunhofer ENAS TECHNISCHE UNIVERSITÄT

Seite 7 23.08.24

### Example IR-Imager

Seite 8

23.08.24

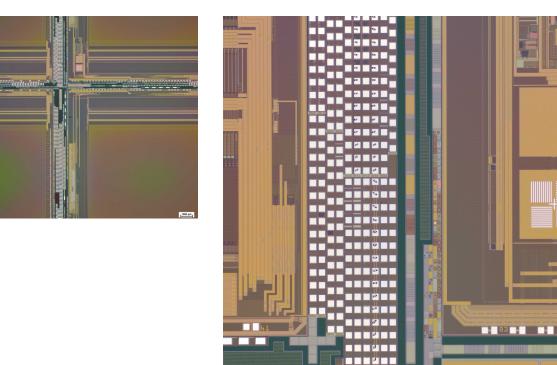

#### Sensor design – different feature sizes and different pattern density

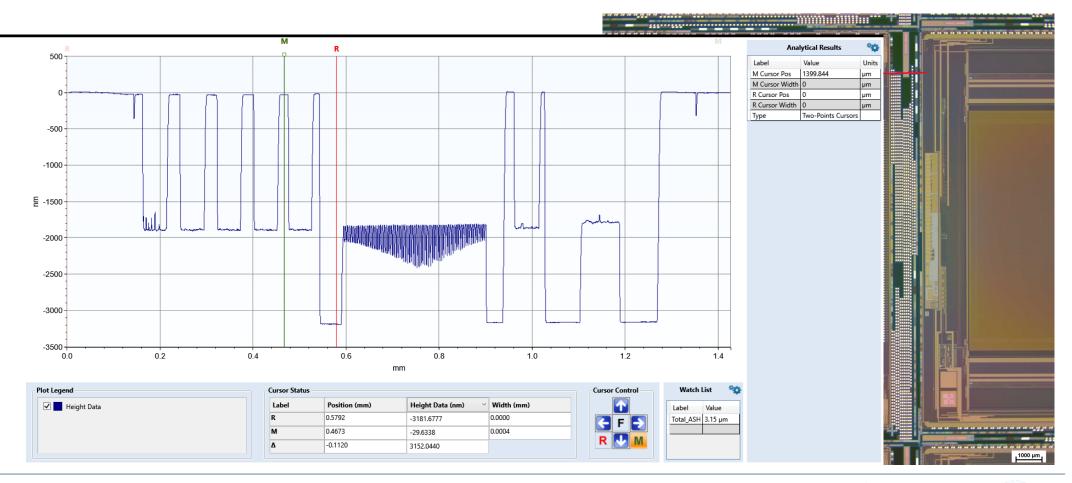

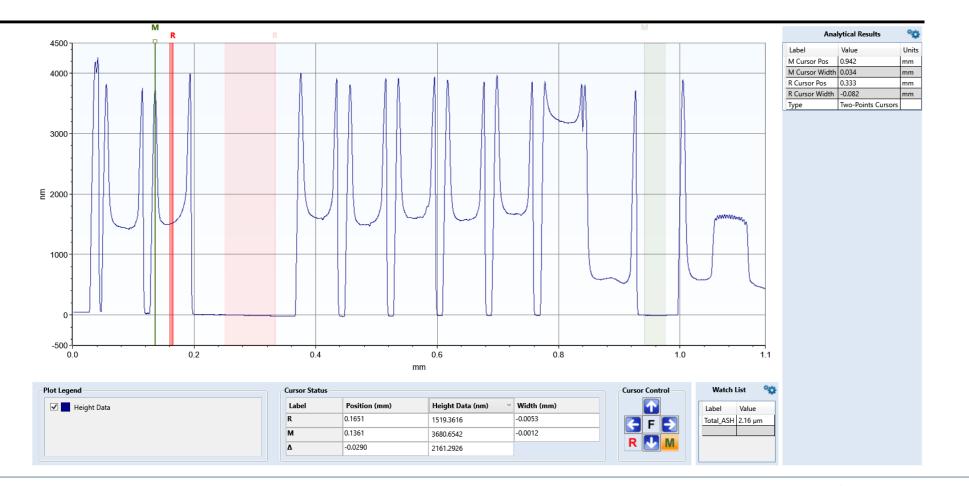

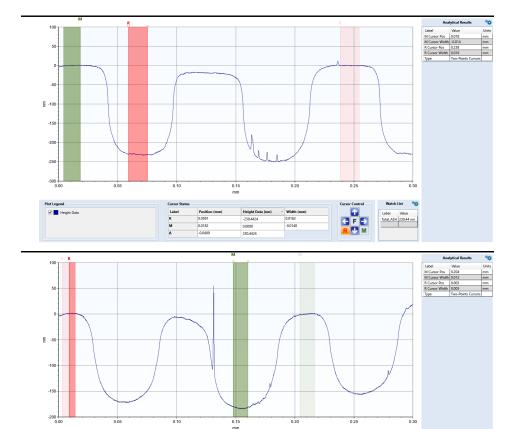

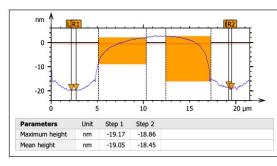

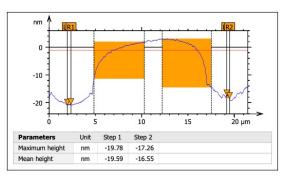

### Profile across IO-pads and dicing lane – starting situation

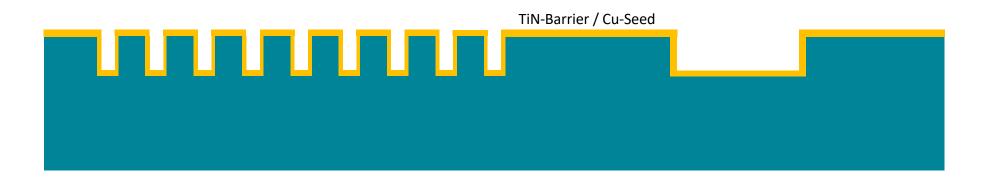

#### Common fabrication approach

- Ti/TiN-Barrier / Cu-Seed deposition by PVD

- Full wafer plating Cu thickness according maximum pattern depth

- Cu / Barrier CMP

#### Disadvantages

- Thick copper

- Long polish time

- Uniformity issues

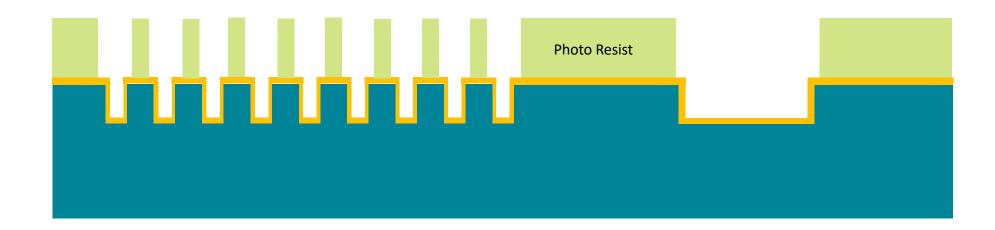

### Selective plating / pattern plating

### Wafer after selective ECD with resist in place

### Wafer after selective ECD and resist removal

#### Metal profile after selective ECD and resist removal

#### CMP process

- Axus Surface polisher with Crystal polish head

- Alkaline Cu-slurry with app. 10% H2O2 content (commodity HV slurry)

- Alkaline barrier slurry with tunable selectivity (commodity HV slurry)

- Hard pad (comparable to IC1000 class)

- Pad conditioner with "new grade diamonds"

- Brush clean (G&P412R) using DI-water and alkaline post-CMP cleaning chemistry

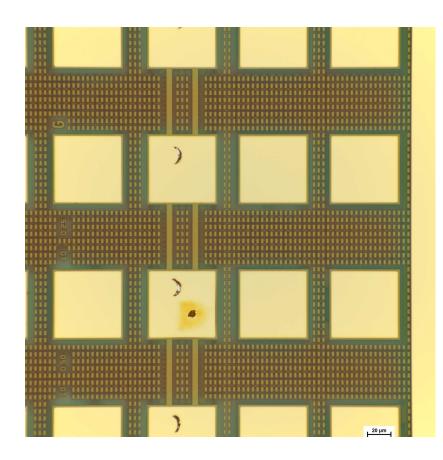

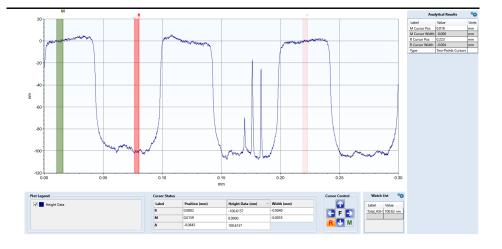

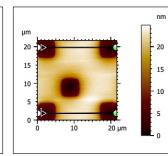

#### Wafer after Cu and barrier CMP

Height Data (nm)

Width (mm)

1.4009

0.0052

-182.3376 -183.7385

0.0052

Position (mm) 0.0088 0.1478 0.1389

Label R M

Cursor Control

Watch List 🛛 😭

Label Value Total\_ASH -183.74 nm

### Metal profile IO-pads after CMP

Plot Legend

🗹 📕 Height Data

Value

-18.75 nm

0.3014 nm

-19.05 nm

-18.45 nm

0.6027 nm

-18.07 nm

1.523 nm

-16.55 nm

3.045 nm

-19.59 nm

Unit

Parameters

Mean height - Mean

Mean height - Std dev

Mean height - Min

Mean height - Max

Mean height - Range

Mean height - Mean

Mean height - Min

Mean height - Max

Mean height - Range

Mean height - Std dev

| Statistical summary |        |         |        |        |       |      |  |  |  |  |

|---------------------|--------|---------|--------|--------|-------|------|--|--|--|--|

| Parameters          | Mean   | Std dev | Min    | Max    | Range | Unit |  |  |  |  |

| Mean height         | -18.41 | 1.149   | -19.59 | -16.55 | 3.045 | nm   |  |  |  |  |

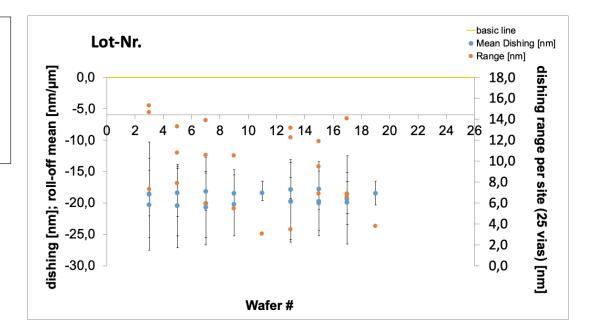

### Summary pattern plating / selective plating for IR-imagers

- Over-all polish time: app. 3:30 minutes

- For comparison polish time for a fully plated wafer of the same product: 9:50 minutes

#### 60% reduction of CMP process time

- Significant cost savings

- Better uniformity

- Less topography issues

- Additional efforts for this approach

- Photomask

- Litho step (1:1 lithography)

- Resist strip

# Outline

Background

Example IR imager

Hybrid bonding

Reminder ICPT2024

Seite 21 23.08.24

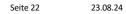

#### Example hybrid bonding Roughness to high Oxide to Oxide bond at Heat closes dishing gap room temperature (metal CTE > Oxide CTE) Silicon / GaAS / GaN / ... Silicon / GaAS / GaN / ... Dishing to high / low (protrusion) CMOS / LED / ... CMOS/LED/ ... Oxide Metal Oxide ta Oxide Oxide CMOS CMOS Silicon Silicon Erosion (higher CMP rate Critical parameters for bonding at higher pattern density) These parameters have to be Roughness Oxide • measured during processing in Dishing ٠ an adequate way to increase Erosion ٠ homogeneity, quality, yield, ... Topography (from underlying layers) • Other topography

Failure modes, which prevent bonding

#### Hybrid bonding – process requirements

- Good uniformity: within die, within wafer, wtw

- Low remaining topography

- Low roughness

#### Specific to hybrid bonding applications

- Oxide roughness: same as direct bonding < 0.5 nm</p>

- Oxide rounding: < 1 nm / μm</p>

- Cu roughness in lower nm range

- Dishing: no rule of thumb, depends on via size (Cu-volume) and temperature budget (typ. 1 nm ... 10 nm)

- Low remaining long-range topography (typ. less than 10 nm)

- Trenching: as low as possible (undesired effect)

#### How to achieve these requirements?

- Most elegant: the topmost layer (hybrid bond layer) is already perfect for hybrid bonding

- No topography, even in dicing lanes

- Very uniform pattern size and pattern distribution

- Reality

- Last layer has different metal patterns with different pattern sizes

- Still topography in 10<sup>th</sup> of nanometer scale from underlying layers and dicing streets

- Common workaround: adding another oxide layer(s) with embedded barrier and Cu

- Oxide layer and CMP will help to eliminate any remaining topography from lower layers and dicing streets

- Metal patterns in this oxide layer can be designed to adopt pattern size and pattern distribution

- Downside additional efforts, such as photo masks, litho, oxide patterning, resist stripping, CMP

Seite 24 23.08.24

# Outline

Background

Example IR imager

Hybrid bonding

Reminder ICPT 2024

Fraunhofer ENAS TECHNISCHE UNIVERSITÄT

Seite 25 23.08.24

# ICPT 2024 – only 7 weeks to go!

ICPT International Conference on Planarization/CMP Technology

Early bird rate ends on September 1! It saves you 100 Euro! Think about! German beer is not as cheap as it was 5 years ago!

TECHNISCHE UNIVERSITÄT

CHEMNITZ

ENAS

Seite 26 23.08.24

## ICPT 2024 – the venue: Kurhaus Wiesbaden (spa / cure house)

Seite 27 23.08.24

## ICPT 2024 – the conference room

Depending on table/chair layout up to 1350 persons

Seite 28 23.08.24

# We are looking forward seeing

# you in at ICPT 2024 in

# Wiesbaden, Germany!

Seite 29 23.08.24

# Thank you for your attention!

Imme Ellebrecht +49 176 46651838 imme.ellebrecht@erzm-tech.com

Dr. Knut Gottfried +49 179 2042873 knut.gottfried@erzm-tech.com

23.08.24 Seite 30