## The material removal and surface generation mechanism in ultra-precision grinding of silicon wafers

Hongfei Tao<sup>1</sup>, Yuanhang Liu<sup>1</sup>, Dewen Zhao<sup>1</sup> and Xinchun Lu<sup>1</sup>

State Key Laboratory of Tribology, Tsinghua University

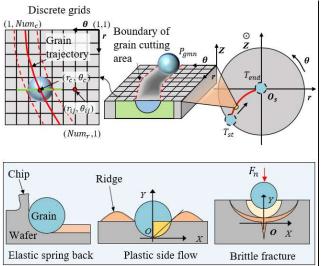

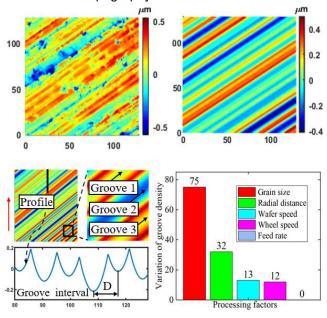

The ultra-precision grinding technology based on the workpiece self-rotational principle has been extensively employed to obtain a high surface accuracy and material removal rate during the wafer thinning process. However, no estimation methods and prediction models are currently available for the surface topography of ground especially considering the material wafers. removal characteristics between the grain and silicon. This paper proposed three-dimensional topography modeling framework from a micro-scale perspective to reveal the material removal and surface generation mechanism underlying the wafer self-rotational grinding process. First, the wheel morphology was reconstructed via the random operation for grain position and size, while the combined effects of plastic side flow, elastic spring back and brittle fracture were quantized according to the elasticity theory principle. Then, a new method was developed to calculate the profile height of the wafer topography using kinematic transformation. The groove angle and surface roughness were used to characterize the wafer surface topography. The findings were consistent with the simulation results and validated the correctness of the model. The simulation model was used to examine the impact of the grain size and grinding parameters on the wafer surface topography, while the degree of influence was further evaluated according to the change rate of the groove density curve. This work provided new insights into the material removal behavior during wafer self-rotational grinding and optimized the grinding parameters to obtain a smoother surface.

Abstracts must be submitted by the end of day, **May 1, 2022**. Please submit your abstract by email to **support@icpt2022.org**.

## **Corresponding Author:**

Xinchun Lu

Tel: +010-6279736

E-mail: xclu@tsinghua.edu.cn

Laboratory of Tribology, Tsinghua University,

Beijing 100084, China.

Fig.1 Schematic diagram of ground wafer topography simulation.

Fig.2 Experimental and simulated analysis for wafer surface topography.

Preference: √ Oral ☐ Poster

Topic Area: 3D ICs/TSV/packaging applications