### Trends with Sustainability and Emerging Developments in Wet and Dry Processes

NCC AVS User Group Meeting

December 1, 2022

Mike Corbett

mcorbett@linx-consulting.com

### Agenda

- Intro to Linx Consulting

- Review of SPCC and ESG Conferences

- Overlap of Wet and Dry Processes

- Perspectives on the Development and Implementation of Sustainable Processes in the Semiconductor Industry

### **Linx Consulting**

### **Linx Consulting**

- 1. We help our clients to succeed by creating knowledge and developing unique insights at the intersection of electronic thin film processes and the chemicals industry on a global basis

- 2. The knowledge is based on a core understanding of the semiconductor device technology; manufacturing processes and roadmaps; and the global structural industry dynamics

- *3. This knowledge is leveraged to create advanced models, simulations and real-world forecasts*

- 4. Our perspectives are by direct research and leveraging our extensive experience throughout the global industry value chain

| <ul> <li>Multi-Client Reports         <ul> <li>IC Materials</li> <li>CMP / Abrasives</li> <li>Deposition / ALE</li> <li>Patterning Materials</li> <li>Cleaning</li> <li>Electronic Gases</li> <li>Bulk Chemicals</li> </ul> </li> <li>Forecast services</li> </ul> | <ul> <li>Proprietary Projects <ul> <li>Market &amp; Strategic Planning</li> <li>M &amp; A Services</li> <li>Growth and Diversification</li> <li>Supply Chain Optimization</li> <li>Technology Commercialization</li> <li>Strategic Planning</li> <li>Scenario Planning</li> <li>Voice of the Customer</li> </ul> </li> </ul> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Econometric Semiconductor Forecast         <ul> <li>Financial planning</li> <li>Sales and Operational planning</li> <li>Forecasting</li> </ul> </li> </ul>                                                                                                | <ul> <li>Cost Modeling         <ul> <li>Client demand modeling</li> <li>Product development</li> <li>Bill of Materials quantification</li> </ul> </li> </ul>                                                                                                                                                                 |

| <ul> <li>Semi Technology Conferences         <ul> <li>The Business of Cleans &amp; SPCC</li> <li>Electronic Specialty Gas Conference</li> </ul> </li> </ul>                                                                                                        | <ul> <li>Wafer Demand Forecasting</li> <li>Regional Forecasting</li> </ul>                                                                                                                                                                                                                                                   |

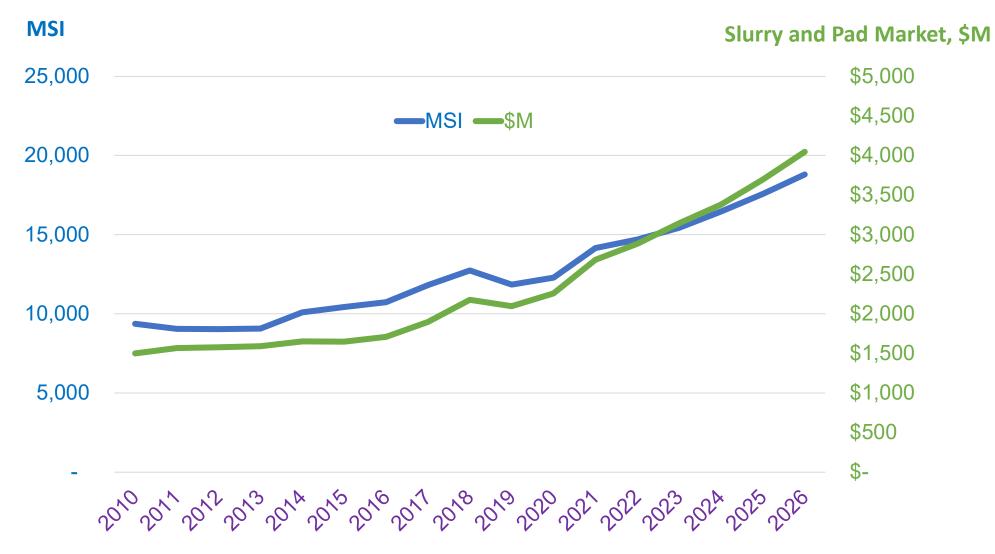

### **CMP Consumables Will Grow Above MSI**

CMP Markets & Technologies 2021 External Disclosure Not Permitted

# 24<sup>th</sup> Edition

# Surface Preparation and Cleaning Conference

17-18 October, 2022 Chandler, AZ

### Intel Keynote on Defectivity Trends

@Intel 2022

### **Critical Defect Trend**

Global Sourcing for Equipment & Materials

- Special cleaning formulations, increase # of damage-free cleaning (High aspect ratio structures), precision of patterning and cleaning, unprecedented etch selectivity with atomic level of etch control, more CMP steps, Particle control in ALD, high K deposition/Cleaning challenge

- Role of <<5nm conductive particle for complex topography of advanced 3D gate stack integrity and device reliability</p>

- > Poor signal to noise ratio (SNR) of localized information

- ➤ HVM EUV towards High NA Readiness: Print even smaller features on Si → 2025

- Key Measurement and Metrology challenge: Detection and Measurement of <<10nm SEVD process adders and interfacial defects/films (multiple stacks)

### **W PCMP**

THE SURFACE PREPARATION AND CLEANING CONFERENCE (SPCC)

SPCC 2022 October 17-18, 2022

# Ti ion contamination and removal mechanism during the W CMP process

**Palwasha Jalalzai**<sup>1</sup>, Ranjith Punathil Meethal<sup>1</sup>, Sumit Kumar<sup>1</sup>, Tae-Gon Kim<sup>2</sup>, Wonseob Cho<sup>3</sup>, Andreas Klipp<sup>4</sup>, Jin-Goo Park<sup>1\*</sup>

<sup>1</sup> Department of Materials Science and Chemical Engineering, Hanyang University, Ansan, Republic of Korea

<sup>2</sup> Department of Smart Convergence Engineering, Hanyang University ERICA, Ansan 15588, Korea,

<sup>3</sup> Electronic Material R&D Center Asia, BASF, Suwon, 16419, Republic of Korea

<sup>4</sup> BASF SE, Ludwigshafen, 67056, Germany

The Engine of Korea

\*jgpark@hanyang.ac.kr

### **PVA Brush Defects**

THE SURFACE PREPARATION AND CLEANING CONFERENCE (SPCC)

SPCC 2022 Wild Horse Pass, Chandler, AZ, USA October 17-18, 2022

### Characterization of impurities from incoming PVA brush for sub 10 nm post CMP cleaning process

October 17, 2022

Kwang-Min Han<sup>1</sup>, Suprakash Samanta<sup>2</sup>, Jerome Peter<sup>2</sup>, and Jin-Goo Park<sup>2,\*</sup>

<sup>1</sup>Department of Bio-Nano Technology and <sup>2</sup>Department of Materials Science and Chemical Engineering, Hanyang University, Ansan, 15588, Republic of Korea

\*jgpark@hanyang.ac.kr

The Engine of Korea

### **IMEC Backside Thinning**

# Extreme Silicon Thinning For Back Side Power Delivery Network Application: Need For a Highly Selective Alkaline Silicon Etch Stopping On SiGe Etch Stop Layer

Farid Sebaai<sup>1</sup>, Roger Loo<sup>1</sup>, Anne Jourdain<sup>1</sup>, Kurt Wostyn<sup>1</sup>, Eric Beyne<sup>1</sup>

<sup>1</sup> IMEC vzw, Kapeldreef 75, B-3001 Heverlee, Belgium

# Welcome

00000000

# 4<sup>th</sup> Electronics Specialty Gas Conference

111 1 111

## **Business Interface Conference**

## October 19 - 21

# ELECTRONICS KLAE (DUPONT)

### **Sponsors**

# SCREEN

### HUNTSMAN

Enriching lives through innovation

### **Sponsors**

### Business Interface Conference & Market Overlap of Wet and Dry Processes

| Time     | Title                                                                             | Speaker                                           |

|----------|-----------------------------------------------------------------------------------|---------------------------------------------------|

| 8:40 AM  | Keynote Speaker: Semiconductor Technology Roadmap –<br>Dry and Wet Tension Points | Scotten Jones<br>IC Knowledge                     |

| 9:20 AM  | Is the Economy in Recession? And Does It Matter for Semiconductors?               | Duncan Meldrum<br>Hilltop Economics               |

| 9:50 AM  | NIST Activities in the Semiconductor Agency                                       | James Maslar<br>NIST                              |

| 10:10 AM | Semiconductor Industry Growth and Opportunities in Greater Phoenix                | Chris Camacho<br>Greater Phoenix Economic Council |

| 10:30 AM | Break                                                                             |                                                   |

| 11:00 AM | Review of Gases and Chemicals by Process Module                                   | David Maloney<br>Linx Consulting                  |

| 11:30 AM | Wet vs. Dry Processing Challenges for Advanced<br>Transistors                     | Trace Hurd<br>Tokyo Electron                      |

| 12:00 PM | Strategies for Targeted Contaminants Removal in Gas and Liquid Filtration         | Jad Jaber<br>Entergris                            |

| 12:30 PM | Lunch                                                                             |                                                   |

### Sustainability Within The Semiconductor Industry

| Time    | Title                                                                                                | Speaker                                                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1:30 PM | Introduction to the Sustainability Session                                                           | Mike Corbett<br>Linx Consulting                                                                                                         |

| 1:45 PM | Keynote Speaker: Net-Zero Semiconductor Manufacturing in the Future                                  | Suresh Ramarajan<br>Micron                                                                                                              |

| 2:30 PM | Panel Discussion: Sustainability                                                                     | Moderator: James Amano – SEMI<br>Panelist: Taimur Burki – Intel<br>Tracey Christiansen - Entegris<br>Benjamin Gross – Applied Materials |

| 3:45 PM | Break                                                                                                |                                                                                                                                         |

| 4:15 PM | ESG Sustainability via Materials Innovation and Process<br>Improvement                               | James Nehlsen<br>EMD Electronics                                                                                                        |

| 4:45 PM | Toward Sustainable Fab: Reducing Bulk Chemicals by SPM<br>Reuse in Single-Wafer Process Applications | Jim Snow<br>Screen                                                                                                                      |

| 5:15 PM | Closing Remarks - End of Wednesday Sessions                                                          | Mike Corbett                                                                                                                            |

### **ICKnowledge Roadmaps**

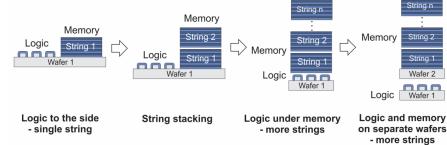

#### **3D NAND Evolution**

#### **IC** KNOWLEDGE LLC

**IC** KNOWLEDGE LLC

- 3D NAND layers likely to continue to increase to around 1,000 layers.

- String stacking controls aspect ratio by splitting up the layers into strings.

- Logic under the array improves scaling but presents process challenges.

- Long term the logic and memory will likely be on separate wafers for process simplicity and yield reasons.

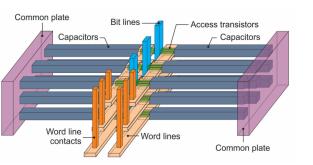

#### **3D Stacked DRAM**

- Stacked horizontal capacitors.

- Memory array and peripheral logic likely to be on separate bonded wafers.

- Vertical pitch ~80nm with ~100 layers needed for density = ~8,000nm stack of epitaxially deposited single crystal Si/SiGe (SiGe is a sacrificial film).

- Vertical bit line.

- Stair step word line that surrounds the access transistor (GAA).

- No EUV

#### 3D DRAM Memory Array

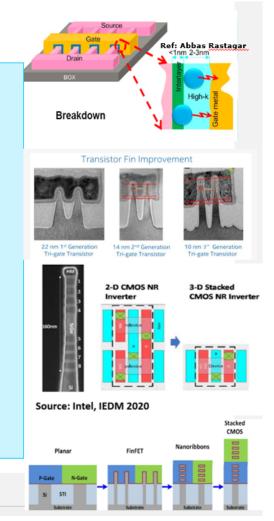

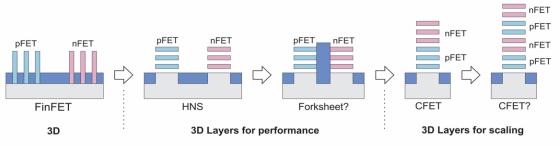

#### Logic Evolution

- FinFETs are 3D but not layer based.

- Horizontal Nano-Sheets (HNS) use layers for performance. HNS may evolve to Forksheets for density but only Imec appears to be pursuing it.

- Complimentary FETs (CFETs) use layers for scaling. Two device stacks are clearly on the roadmaps at major logic providers, three, four or more device stacks are being evaluated.

### **TEL – Wet & Dry Approaches**

#### Future Challenges

- Growing the Tool Kit

- Selectivity requirements among Si based films will continue to increase

- New gases and gas mixtures will be needed

- Optimizing speed, cost, and selectivity could open new applications in 3D Memory

- Metal and Metal Containing Film Etches

- Cu, Co, Ru partial etches for FSAV integration

- Mo, W etches for 3D memory enablement

- 2D Material Compatibility

- Thermal Atomic Layer Etching

- Research ongoing at numerous universities, e.g. Colorado, NC State...

Trace Q. Hurd PhD / Tokyo Electron America / October 19, 2022

#### TEL. 19

#### Conclusions

- Device Technology Roadmap 3D Trends Driving Significant Challenges

- High Aspect Ratio Structures

- Confined Space Processing / Hidden Surfaces

- Increase in Risk of Pattern Collapse

- Multi-Film Selectivity Requirements Increasing

- Isotropic Gas Phase Etch Processes Address Many of These Challenges

- Elimination of capillary forces, atomic scale precision, high reactant mobility, little to no pattern loading, morphological control

- Applications for Isotropic Gas Phase Processing Expected to Grow in both Logic and Memory

### **Challenges - Dry vs Wet Etching**

#### Dry

#### Horizontal-direction etch

The anisotropic nature of gas phase etching reaction make lateral etch difficult to control

#### Damage

Ionized molecules generated by RF power during plasma reaction can damage the underlying substrates

#### Selectivity

Compared to liquid phase processes, gas phase processes can't effectively accommodate sophisticated chemistries to address selectivity requirements

#### • EHS

Many dry etch chemistries rely on greenhouse gases (CF<sub>4</sub>, SF<sub>6</sub>...)

#### Wet

#### Etch profile management

• Wet etch is an isotropic process. Difficult to maintain straight vertical post-etch shape through precise control

#### • Post drying

• The post clean step after wet etch requires IPA drying, which can cause patterned structures to collapse

#### High Aspect Ratio

• Wet etchant is unable to penetrate small dimensions at the bottoms of high aspect-ratio structures

#### Throughput

• Some wet etch applications like H<sub>3</sub>PO<sub>4</sub>-based nitride etch take several hours and become bottleneck in the fab

• EHS

Disposal cost of waste wet process streams continue to go up www.linx-consulting.com

### **High-Selectivity Nitride Etch**

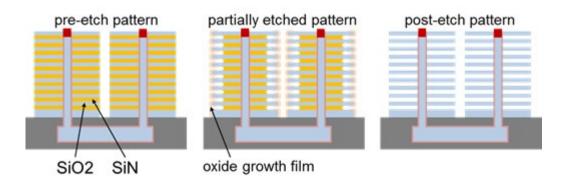

#### **Nitride Strip and Cell Formation**

- A slot mask is applied and etched down through the stack. A wet etch is used to etch out the nitride layers that are then replaced with aluminum oxide and titanium nitride memory cell films and then the horizontal layers are filled with tungsten. The tungsten is etched back in the slot, oxide is deposited, and the trench is filled with tungsten.

- Nitride strip in charge trap still remains a challenge. New chemistries are required. This is getting more difficult as the number of layers and HAR increases.

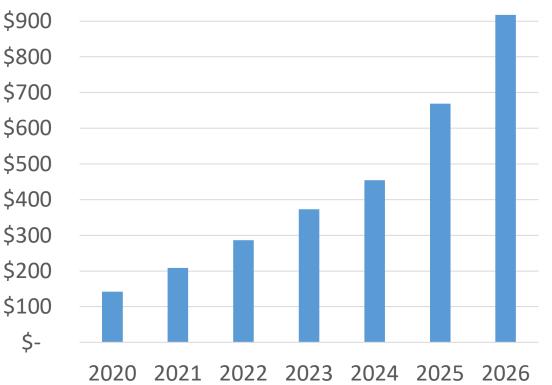

### \$ Million \$1,000 \$900 \$800

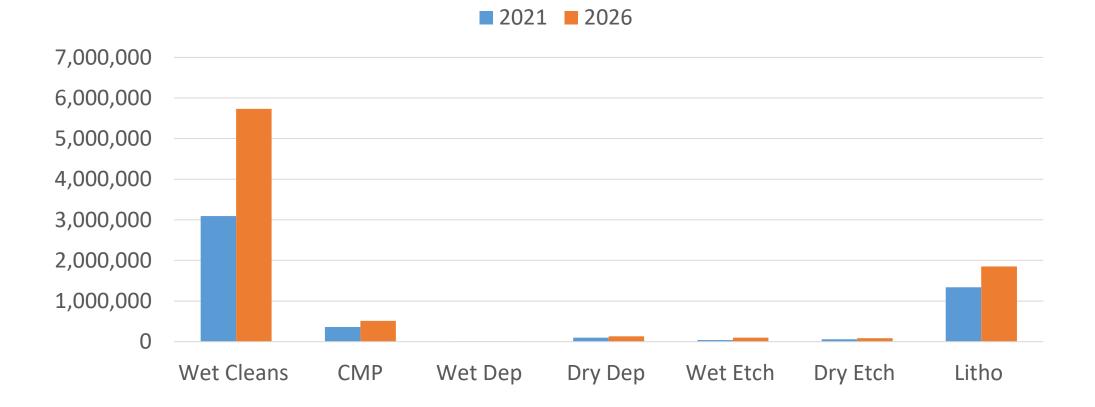

# Chemical Volume by Process (MT), 2021 & 2026

# Sustainability – Major Focus on the Uses of Chemicals in Fabs

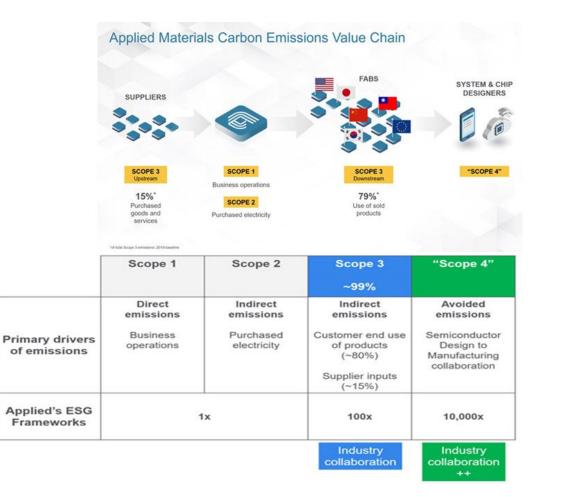

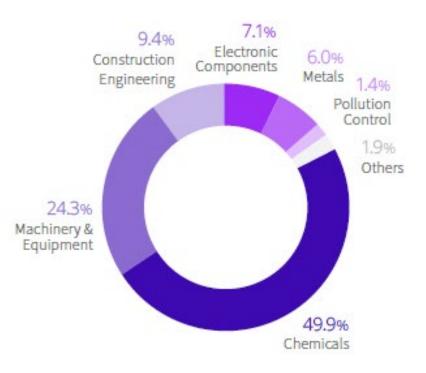

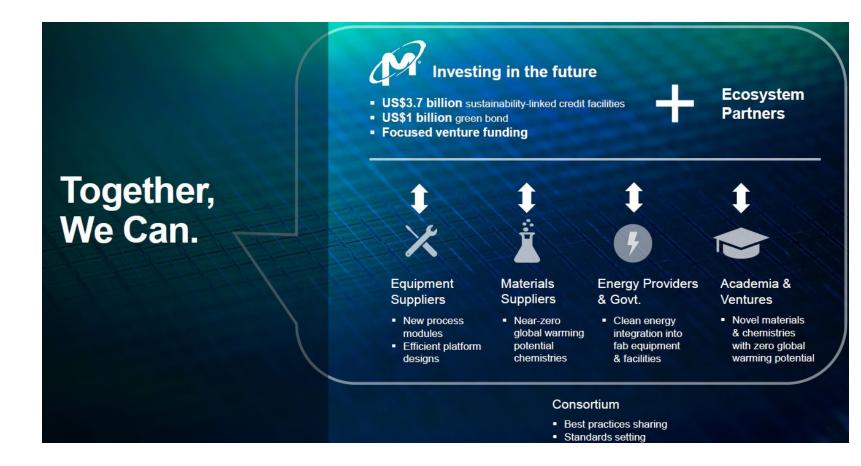

#### **OEM PERSPECTIVE**

#### **SEMI PRODUCER PERSPECTIVE**

Environmental Hotspot Analysis of the Supply Chain

### **Micron Perspectives**

- Process GHG Decarbonization Preferred Innovations

- 1. Eliminate / Replace

- 2. Reduce / Reuse

- 3. Destroy

- 4. Data Visibility / Smart Controls

- Heat Transfer Fluid

Decarbonization

- Fuel Decarbonization

- Energy Decarbonization

### **Screen & EMD – Pathways to Sustainability**

#### Low CoM Through SPM Reuse SCREEN Chemical consumption data **Test Condition** 300 SPM-1 250 1. SPM-1/No reclaim Consumption mL/wafer SPM mixing ratio : 2:1, 30sec New SPM 200 150 2. New SPM SPM mixing ratio : Y:1, 30sec With Reclaim 50 SPM H2SO4 H2O2

SCREEN Semiconductor Solutions Co., Ltd.

SCREEN Semiconductor Solutions Co., Ltd

SPE-221003152443464-L1

#### Keys to Sustainability Reducing Emissions with Chemistry

#### Abatement

Minimize formation of highly stable molecules during process to improve DRE and reduce secondary emissions

#### **Process Recipe Tuning**

Optimize for low generation of high-GWP species like CF<sub>4</sub>

#### New Materials

Can be tailored to specific applications to reduce process emissions by >90% while maintaining or improving performance

12 ESG Conference | Oct 2022

#### Sustainable Etch & Clean

Achievable through multiple pathways while driving capabilities forward

### Conclusions

- Vertical scaling bring many challenges

- Many tension points still exist between wet and dry processing

- These tension points may cause inflections on how devices are manufactured, integration approaches and materials

- Sustainability is a major industry driver

- Materials are a target for sustainability initiatives; all process modules will be impacted

### **More Information**

Mike Corbett +1 973 698 2331 <u>mcorbett@linx-consulting.com</u>

www.linx-consulting.com

Conference presentations from 2016 to 2019 are posted and available for CMPUG members to review at:

https://www.linx-consulting.com/technical-archive/.