# SIA MEMBERSHIP

**CHARTER**

INTERNATIONAL

**CORPORATE**

**CORPORATE PARTNER**

# 2022 CHIPS & SCIENCE ACT

Signed summer 2022 in historic win for the industry

\$39 billion manufacturing incentive program

25% manufacturing investment tax credit

(estimated at \$24.3 billion over duration of credit)

\$13 billion in R&D and workforce investment

# **CHIPS IMPLEMENTATION – GRANTS**

| TOPIC                               |            | REQUIREMENTS/CRITERIA                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Authority                           |            | <ul> <li>Commerce Department – CHIPS Program Office (CPO)</li> <li>White House – CHIPS Steering Council</li> </ul>                                                                                                                                                                                                                                                                                                                                  |  |

| Eligibility                         | <b>***</b> | <ul> <li>Fabs, ATP, SME, research facilities</li> <li>Construction, expansion, and modernization; not a relocation</li> </ul>                                                                                                                                                                                                                                                                                                                       |  |

| Process & Timing                    | <u>(I)</u> | <ul> <li>Application materials released by Feb. 2023 (within 6 mos.)</li> <li>Pre-application phase to allow for Commerce feedback</li> <li>Projects funded in increments as milestones are achieved</li> </ul>                                                                                                                                                                                                                                     |  |

| Funding Priorities & Considerations | \$         | <ul> <li>\$28 billion for leading edge logic/memory; \$10 billion for mature/current tech, new and specialty technologies, equipment and materials</li> <li>Supply chain and national security</li> <li>Jobs, community investment, opportunity and inclusion</li> <li>Workforce development &amp; education partnerships</li> <li>Commercial viability post-CHIPS</li> <li>State/local incentive packages</li> <li>Taxpayer protections</li> </ul> |  |

| Clawbacks                           | $\bigcirc$ | <ul> <li>10-year prohibition on a "significant transaction Involving the material expansion of semiconductor manufacturing capacity"         <ul> <li>Exception for "legacy" – 28nm and older for logic, TBD others</li> </ul> </li> <li>Stock buybacks or dividends</li> <li>Failure to meet target dates</li> </ul>                                                                                                                               |  |

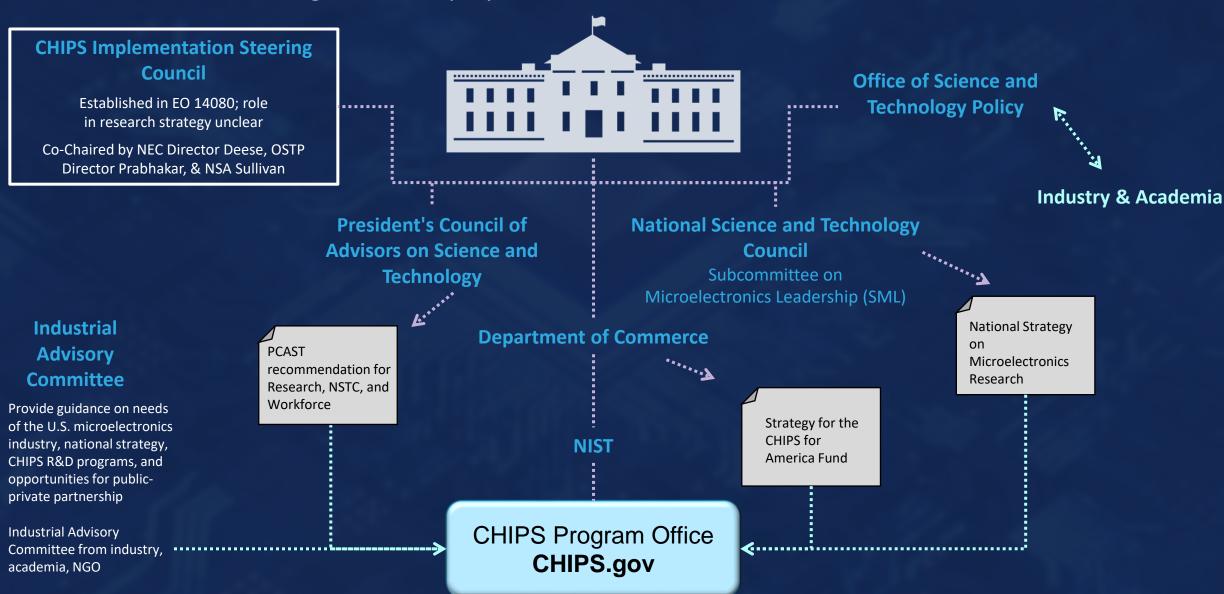

#### RESEARCH STRATEGY DESIGN

Various administrative organizations play a role

# CHIPS IMPLEMENTATION – RESEARCH

#### National Semiconductor Technology Center Dept. of Commerce

- \_\_\_

- Public-private consortium including DOE/NSF

- Work with DOL & universities for post-secondary education

#### National Advanced Packaging Manufacturing Program

Dept. of Commerce

- Strengthen advanced assembly, test, and packaging ("ATP") capabilities

- Coordinate with NSTC and Manufacturing USA Institutes

# Manufacturing USA Semiconductor Institutes

NIST (Dept. of Commerce)

- 1-3 manufacturing centers

- Virtualization & automation of semiconductor equipment; novel assembly, test, & packaging capabilities

# CHIPS Defense Fund

- University-based prototyping, lab-to-fab transition of semiconductor technologies

- DoD-specific workforce training programs

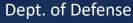

CHIPS & Science Act includes ~\$170 billion in authorizations for research at NSF, NIST, and DOE, subject to future appropriations

### **RESEARCH AUTHORIZATIONS**

Division B of CHIPS & Science increases U.S. science authorizations; appropriations still needed

| Key Programs                                   | 5-year<br>Authorization | Increase over<br>Baseline |

|------------------------------------------------|-------------------------|---------------------------|

| National Science Foundation                    | \$81 billion            | \$36 billion              |

| NSF Tech Directorate                           | \$20 billion            | \$20 billion              |

| NSF Core Activities                            | \$61 billion            | \$16 billion              |

| National Institute of Standards and Technology | \$10 billion            | \$5 billion               |

| NIST Research                                  | \$6.9 billion           | \$2.8 billion             |

| Manufacturing USA                              | \$829 million           | \$744 million             |

| Manufacturing Extension Partnership            | \$2.3 billion           | \$1.5 billion             |

| Department of Energy                           | \$67.9 billion          | \$30.5 billion            |

| DOE Office of Science                          | \$50.3 billion          | \$12.9 billion            |

| Additional DOE Science and Innovation          | \$17.6 billion          | \$17.6 billion            |

| Total                                          | \$169.9 billion         | \$82.5 billion            |

American Institute of Physics | aip.org/fyi

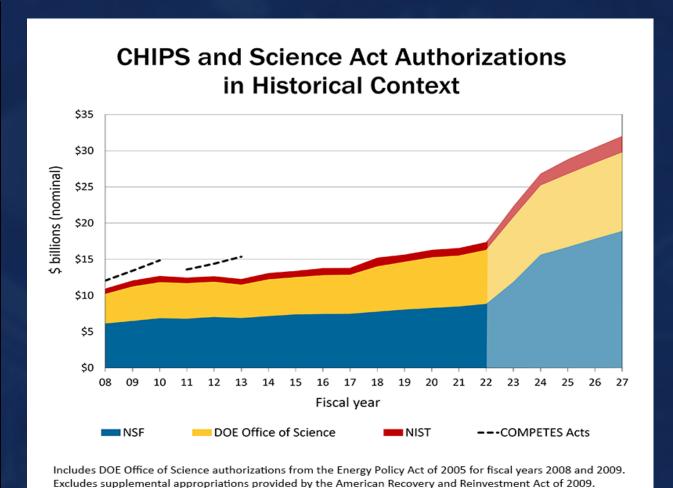

# RESEARCH LANDSCAPE: NSTC/NAPMP & Valley of Death

# CHIPS IMPLEMENTATION – WORKFORCE

#### **Direct Workforce Funding**

CHIPS Workforce & Education Fund National Science Foundation

- \$200 million over 5 years

- **Establishes National Network for** Microelectronics Education

#### **Company Workforce Initiatives**

**CHIPS Manufacturing Incentives** Dept. of Commerce

- Incentive applications require company workforce development commitments

- Partnerships w/ regional institutions encouraged

#### **Indirect Workforce Funding**

NSTC/NAPMP, CHIPS Defense Fund, & Manufacturing USA

Dept. of Commerce, Dept. of Defense, NIST

- \$13 billion R&D funding supports STEM education

- Workforce & skills training explicit in legislation

**CHIPS Funding**

#### **Immigration & Workforce**

NSTC/NAPMP, Manufacturing USA Dept. of Commerce, NIST

- R&D funding creates opportunities for low-volume, high-value visa categories

- PCAST report recommends premium processing for semiconductor visas

## **CHIPS R&D IMPLEMENTATION**

Goal: Promote collaborative R&D ecosystem aligned with industry technology agenda

Key investment areas for NSTC and NAPMP

Support transition pathways for innovative technologies

Upgrade research infrastructure for early-stage ecosystem

Establish and expand access for mid-stage development and prototyping infrastructure

Convene industry, academia, and government for collaborative innovation partnerships

Promote dynamic workforce programs to increase and hone domestic workforce

American

Semiconductor Research:

Leadership Through Innovation

semiconductors.org